Clear Sky Science · zh

嵌入氧化物半导体增益单元的存储器:面向下一代片上存储的材料与集成策略

为何更快、更智能的存储很重要

我们的手机、笔记本和数据中心不断提升性能,但存在一个隐藏的速度瓶颈:在处理器与存储器之间移动数据。本文探讨了一种新型的片上存储,有望缓解这道“存储墙”,使未来计算机在人工智能、云计算及日常应用等任务中更快且更节能。通过重新构想存储单元的构造与所用材料,研究人员旨在将更多数据紧密放置于处理器附近,同时降低功耗和热量。

现代计算机内部的瓶颈

几十年来,处理器性能的提升远快于为其提供数据的主存储器。这种不匹配被称为“存储墙”,意味着高速芯片常常因等待数据而空闲。设计者通过在处理器上部署多层缓存来缓解这一问题。现有缓存依赖一种称为 SRAM 的存储类型,它非常快但面积大且耗电,因为每个位需要六个晶体管。为了获得更大容量,企业将 SRAM 芯片进行三维堆叠或在芯片上集成 DRAM,但传统 DRAM 仍依赖微小电容器,这些电容在极限尺度下难以制造,并且难以与标准逻辑电路集成。

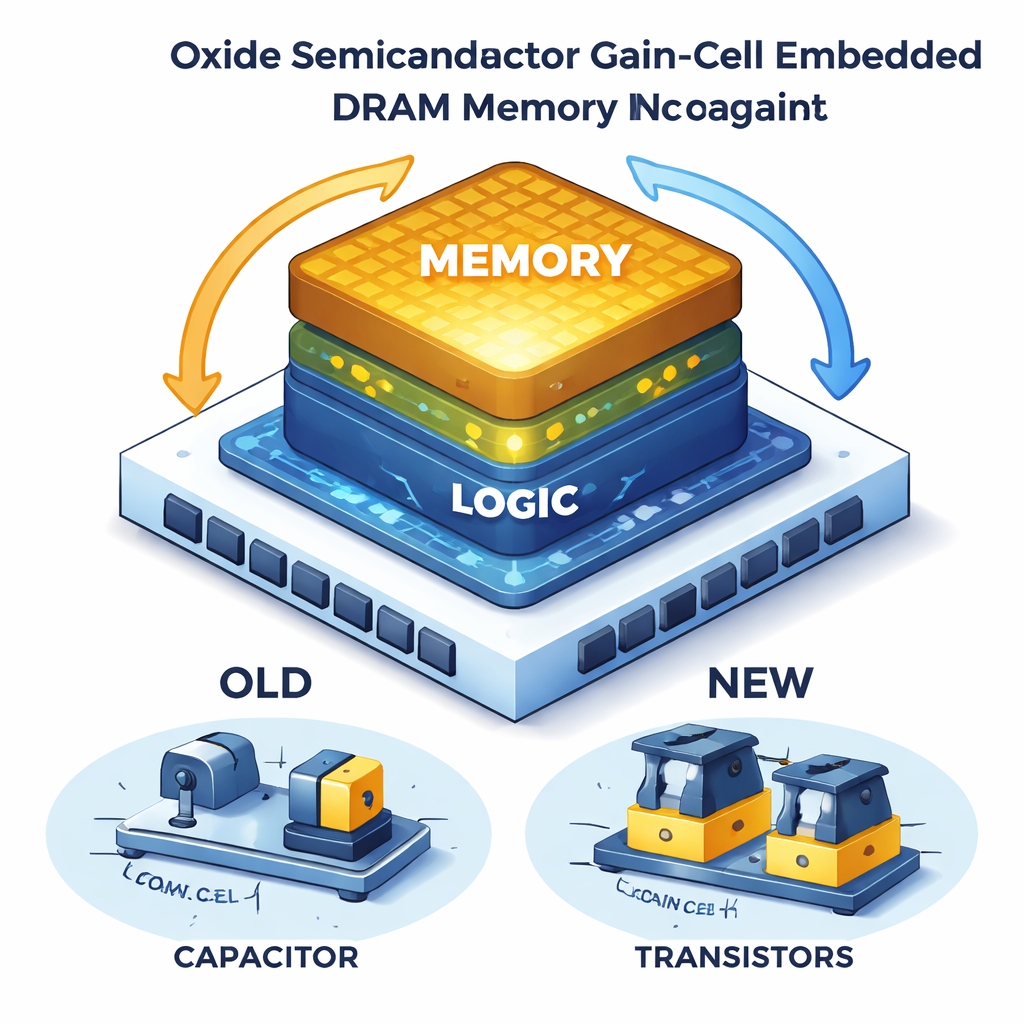

一种不同类型的存储单元

本文重点介绍一种替代方案,称为增益单元嵌入式 DRAM(GC-eDRAM)。与使用独立电容存储电荷不同,增益单元仅用晶体管保存数据,简化了结构并更适合标准芯片制造。该设计自然适合在逻辑电路之上进行三维堆叠,有望实现高密度的“逻辑上方存储”布局。另一个优势是其“非破坏性读出”特性:读取存储值不会立即耗尽它,从而可能减少刷新的频率。然而,在传统硅基实现中,存储电荷在不到毫秒的时间内泄漏,因此频繁的刷新仍然浪费能量并限制实用性。

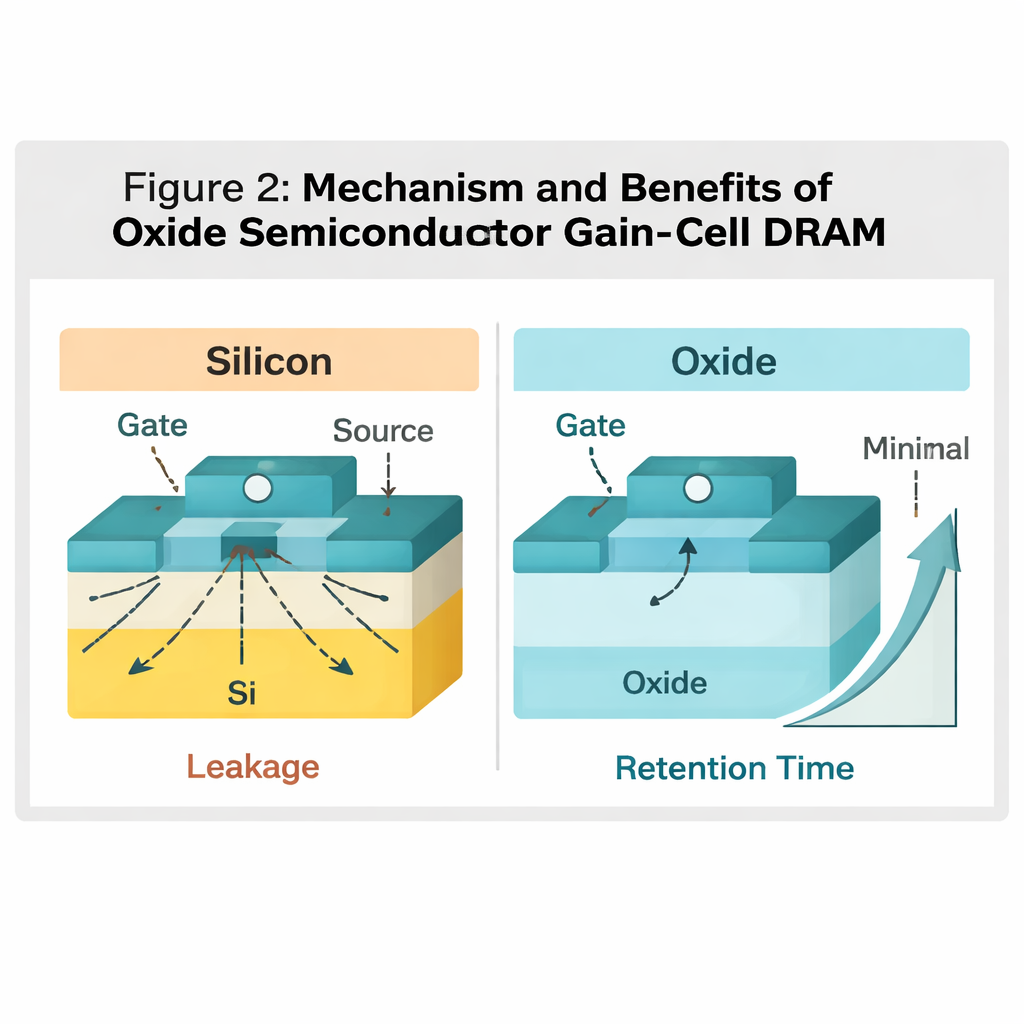

氧化物半导体:更安静、更冷的开关器件

为克服增益单元中的泄漏问题,作者强调了氧化物半导体——如铟镓锌氧化物(IGZO)及相关化合物——作为晶体管沟道材料的新前景。这类氧化物具有较宽的能隙,可在晶体管应处于关闭状态时强烈抑制不想要的电流。实验测得的关电流微小,已接近测试仪器的极限,原型增益单元的数据保持时间可达数秒、数小时甚至超过一天,与硅设计中的毫秒级相比有显著提升。关键在于,这些氧化物可以在相对较低的温度下沉积,兼容芯片制造的“后端”工艺,允许工程师直接在现有硅逻辑之上构建致密的存储层而不损伤其结构。

向上构建:三维堆栈与微小晶体管

随着芯片不断缩小,单纯把晶体管做小会带来新问题,例如对沟道控制变差和泄漏上升。文章回顾了先进的晶体管形状,这些结构将栅极包裹于沟道周围(全栅包围和全通道包围设计),以在纳米级尺寸下仍保持严格控制。将氧化物半导体应用于这些多栅结构,研究人员已展示出超短沟道、极低泄漏和强数据保持能力,并实现了多层存储的垂直堆叠。一些实验性设计的面积效率已达到或超过当今最佳 DRAM 单元,表明未来芯片可在处理器核心正上方极小的占地上承载巨大的存储容量。

从实验室材料到可靠产品

将这些有前景的器件转化为实用存储需要精细的材料工程。文章描述了通过调整氧化物中金属的配比、控制氧含量和使薄膜结晶,来在高速度与长期稳定性之间取得平衡。还讨论了管理缺陷、氢污染以及氧化物与绝缘层之间脆弱界面的方法,以保证器件在高温和长期运行下保持稳定。最后,还涉及工程化金属互连以防止接触电阻抵消新材料带来的益处。综合这些策略的目标是提供既高密度又足够可靠、可进行大规模制造的存储器。

对日常计算的意义

作者总结认为,氧化物半导体增益单元存储可能重塑未来芯片的构建方式。通过将微小、低泄漏的存储单元与逻辑电路上的三维堆叠相结合,设计者可以在处理器旁放置更多快速存储,同时控制功耗。这将缓解存储墙,帮助从 AI 加速器到云服务器与个人设备在速度和能效上取得提升。尽管在可靠性、制造均匀性和整片集成方面仍存在挑战,但文中回顾的工作勾画出一条通往更紧凑、更强大且更节能计算系统的清晰路径。

引用: Chung, S.W., Yoon, S.H. & Jeong, J.K. Oxide semiconductor gain cell-embedded memory: materials and integration strategies for next generation on-chip memory. Commun Eng 5, 39 (2026). https://doi.org/10.1038/s44172-026-00616-5

关键词: 片上存储, 氧化物半导体, DRAM 缩放, 3D 集成电路, 人工智能硬件