Clear Sky Science · zh

三维异质集成微电子器件的热管理:挑战与未来研究方向

为什么芯片堆叠会改变你的日常设备

从手机和笔记本到为人工智能提供动力的数据中心,我们的电子设备在体积不断缩小的同时承担着比以往更多的工作。为了实现这一点,工程师们开始将不同类型的芯片垂直堆叠,形成紧凑的三维封装。这一巧妙做法提升了性能并减少了信号延迟,但也在极小的空间内积聚了大量热量。综述文章解释了为什么热量已成为这一代新型电子设备的主要威胁之一——以及研究人员如何努力防止这些硅制“微型摩天楼”过热。

构建微型电子高层建筑

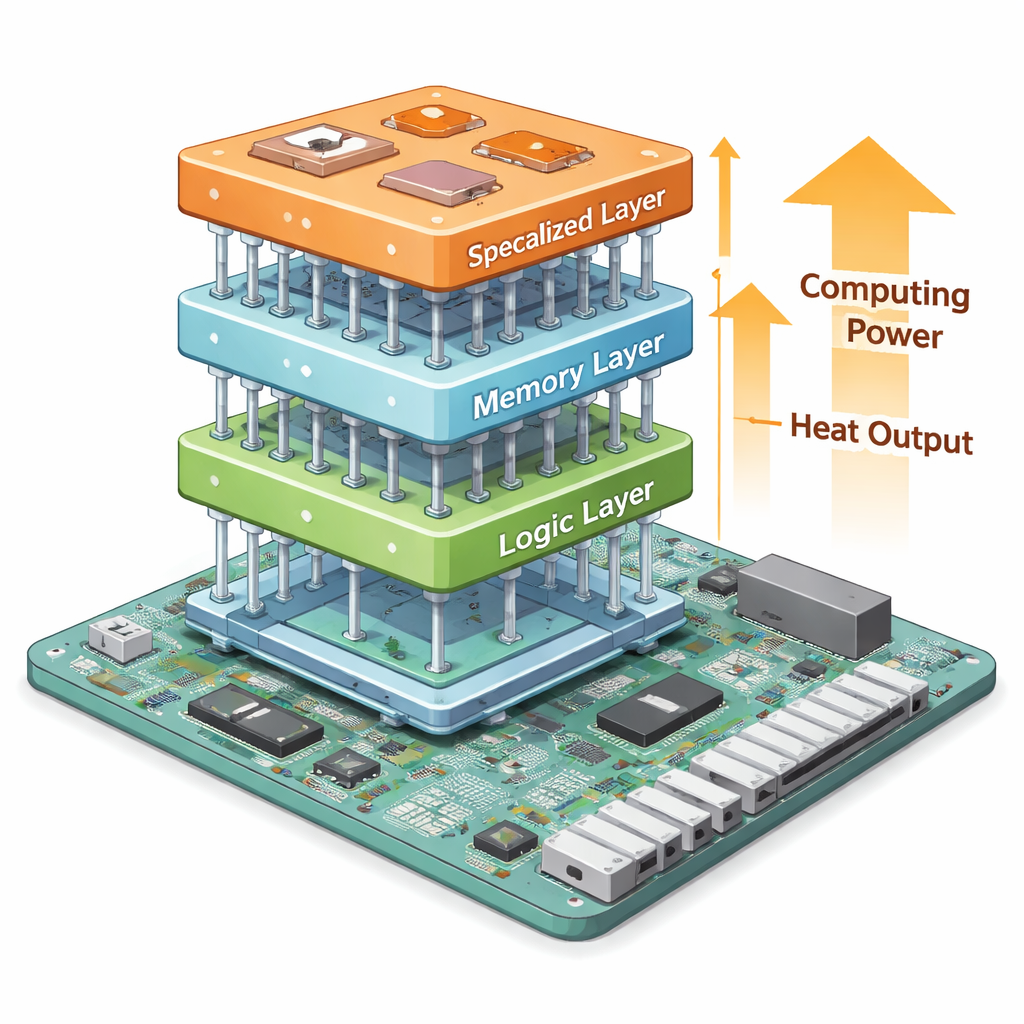

传统芯片大多是平面的:电路在一片硅片上并排展开。随着在二维上继续缩小特征变得愈发困难,行业正转向三维异质集成,将若干层不同功能的芯片——逻辑、存储、射频、光子学等——垂直堆叠并通过金属柱互联。这种布置缩短了通信路径,并允许设计者将不同工厂制造的工艺混合使用。结果是处理更快、通信延迟更低、能效更好,这对人工智能、云计算和先进通信系统尤其重要。

更高功率密度的隐性代价

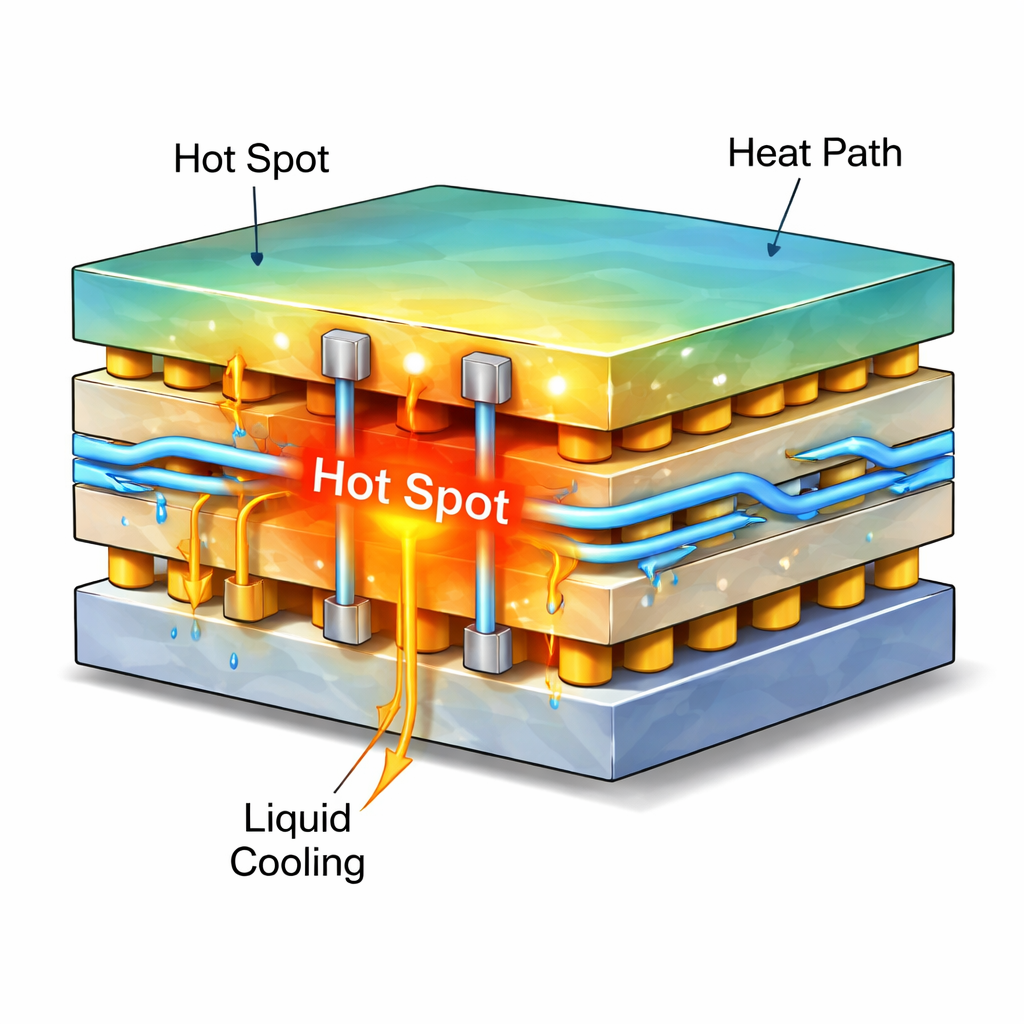

如此紧密的堆叠带来了严重的缺点:热量更难散出。每一层都会因常见的电能损耗产生热量——导线电阻、开关的切换损耗以及始终存在的微小漏电流。在三维堆栈中,这些损耗会累积,中间层(最远离任何冷却表面)往往成为最热的区域。温度可能不均匀上升,形成仅几分之一毫米宽但远高于周围温度的热点。即使比预定工作温度高出几摄氏度,也会大幅降低可靠性、加速老化,并在极端情况下触发热失控——一种温度上升导致电流增加、进而进一步升温的自我增强循环。

当热量扩散、弯曲并破坏结构时

综述指出,温度问题不仅仅是芯片变热;它们会悄然损害整个封装。堆栈中不同材料——硅、金属、高分子和陶瓷——在受热时膨胀量不同。随着器件在空闲和满负荷间循环,这些不匹配会产生机械应力,可能导致焊点开裂、界面处产生间隙以及填充金属的垂直互连受损。与此同时,不均匀加热会引发热串扰:一个发热的逻辑芯片可能无意中加热其上的低功耗存储或光学层,降低其性能。随着时间推移,围绕传热结构的小空洞与裂纹会扩展,增加额外的热阻,使从关键位置移除热量变得更加困难。

在三维移动热量的新手段

为应对这些挑战,研究人员正在重新审视热路径的每一部分。一些策略旨在通过更好的填充材料和层间材料更有效地在堆栈内扩散热量,这些材料在不干扰电信号的前提下具有良好的导热性。还有人将垂直金属柱改造为专用的热导路径,或在信号通道旁加入仅用于散热的额外金属柱。综述还强调了冷却系统向热源更靠近的转变。微小的液体通道和微米级的针鳍阵列可以直接蚀刻到芯片层内或层间,使冷却液离最热点仅几十微米。这些嵌入式冷却器能够去除极高的热流密度并根据每层需求定制流动,但它们也带来了机械强度、制造复杂性以及在压力和湿度下长期可靠性的新问题。

该领域的下一步走向

总体而言,文章得出结论:热控将在很大程度上决定三维堆叠电子技术能走多远。没有单一方案能够解决所有问题:芯片布局、材料、垂直互联、界面层和冷却通道必须协同设计,而非孤立考虑。未来工作将侧重于可扩展的方法,将高导热且机械兼容的材料与可制造的低温工艺相结合,以及开发能将热特性与速度和功耗同等看待的更聪明设计工具。如果这些难关能够克服,三维芯片堆栈有望在更小的封装中持续提供更强的计算能力——而不会自我烧毁。

引用: Sharma, M.K., Ramos-Alvarado, B. Thermal management of 3-D heterogeneously integrated microelectronics: challenges and future research directions. Commun Eng 5, 28 (2026). https://doi.org/10.1038/s44172-026-00590-y

关键词: 3D 芯片堆叠, 电子散热, 热管理, 微流体冷却, 异质集成