Clear Sky Science · zh

通过矩形电压波形中的边缘偏压和结构阻抗变化提高 HARC 蚀刻均匀性

为什么芯片制造商在意笔直的孔

现代存储芯片通过在硅片上钻出数十亿个超深、像铅笔一样细的孔来在更小的空间内容纳更多信息。这些“高纵横比”孔必须几乎完全垂直;即使是轻微的倾斜或形状扭曲也可能毁掉器件并大幅降低良率。本文展示了一种新方法,通过微调等离子体蚀刻过程中硅片边缘处电场的作用,来保持这些孔在整片硅片上的直线性和均匀性。

硅片脆弱边缘的问题

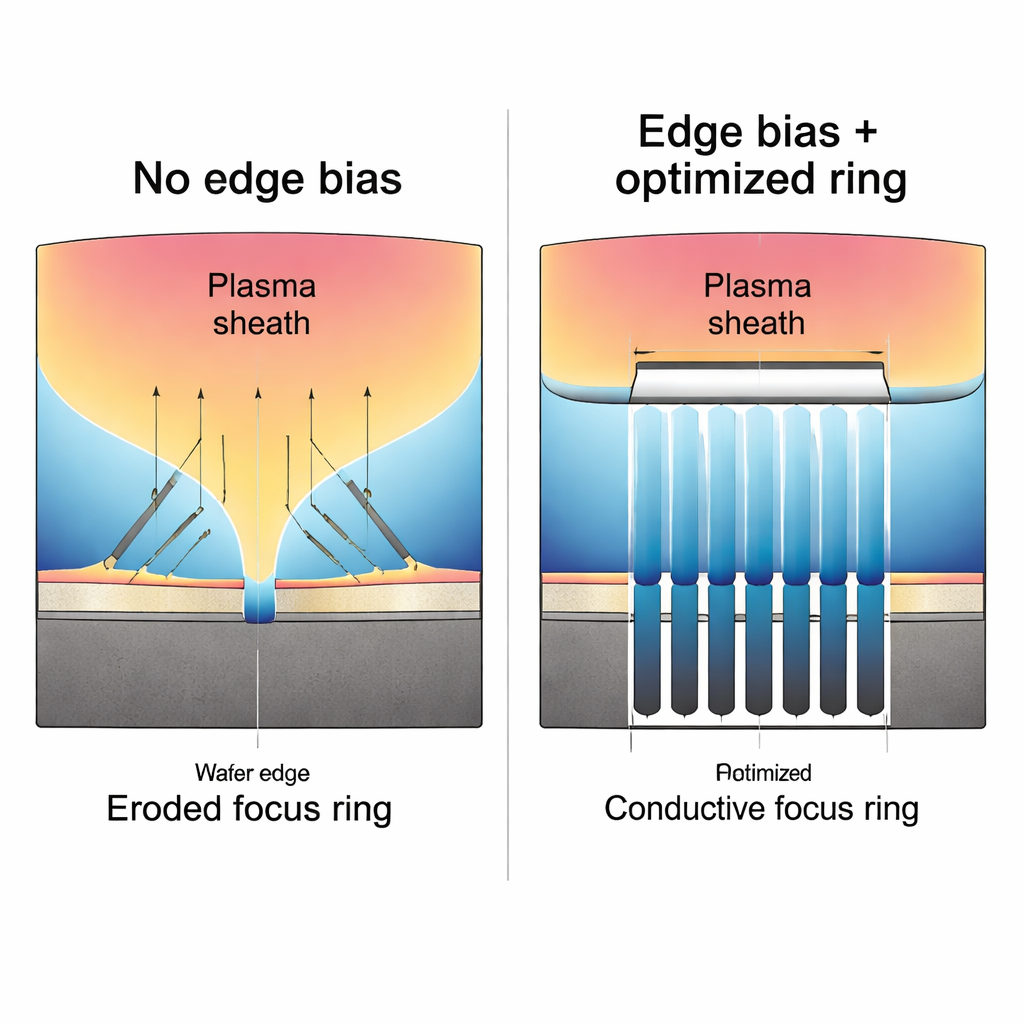

为了在硅片上刻蚀图形,制造商使用等离子体——一种充满高能离子的发光气体,这些离子会轰击并去除材料。硅片周围有一个牺牲性的“聚焦环”,有助于维持从中心到边缘的等离子体均匀性。随着时间推移,该环会在同样严苛的蚀刻环境中被磨损。随着聚焦环侵蚀,指引离子到达硅片的电鞘在边缘处变形。离子不再垂直入射,而是以倾斜角度到达,导致孔向中心倾斜并拉伸成椭圆形。这不仅会扭曲微小的电容结构,还会减少可用面积并降低良率。

在边缘增加可控的“方向盘”

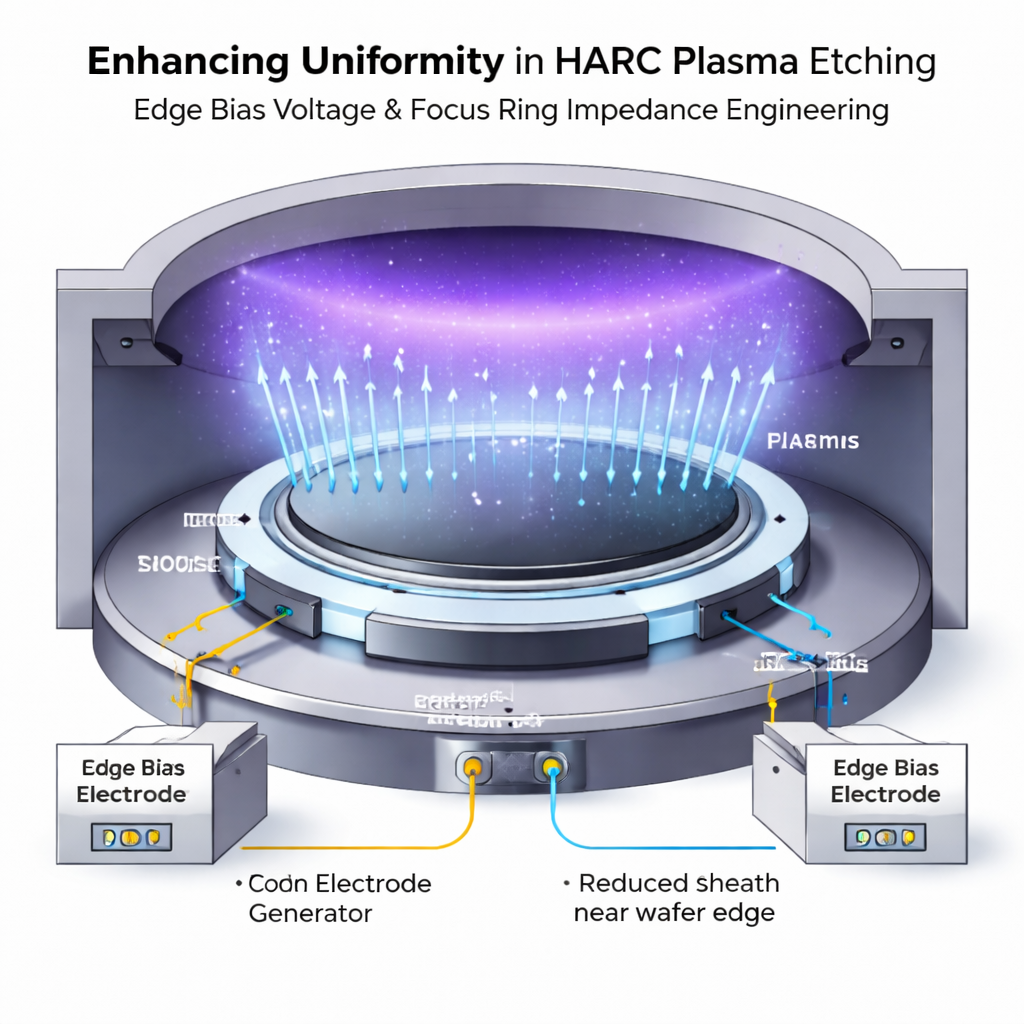

研究人员通过在聚焦环下方增加一个独立可控的边缘电极来解决这个问题,该电极由一个与主硅片偏压分开的矩形形偏压驱动。与通常的平滑正弦波不同,这种方形波形在开与关之间急剧切换,使等离子体与表面之间的电压差在时间上更为稳定。更稳定的推动力使离子以更窄的能量和角度分布到达。通过谨慎提高边缘偏压,团队能够加强并重塑硅片边缘处的电鞘,将离子路径拉回更垂直的方向,即使在聚焦环磨损的区域也能恢复圆形且定义良好的沟槽剖面。

当更高的功率反而变糟

然而,将边缘电压调得过高会产生新问题。在大约 280–300 伏以上,边缘电极与中心电极之间的电耦合导致通过等离子体的不期望电流泄漏。监测显示设备试图施加的电压与硅片实际看到的电压之间出现越来越大的不匹配,同时硅片区域电流升高。这扰乱了精心调谐的电鞘,使等离子体不稳定,并重新引入了非均匀蚀刻:中心区域蚀刻更快,边缘变慢,尽管边缘偏压更高,孔形状仍再次变形。

通过重设计硬件来驯服电场

为了在高电压下恢复控制,团队重新设计了围绕硅片的绝缘和导电部件堆栈——尤其是聚焦环下方和周围的材料。通过更换组件并改变它们的电学特性,他们调整了聚焦环路径与硅片卡盘之间的阻抗比。较高的比值(约 1.31)限制了两个偏压电路之间的不期望耦合,使边缘偏压能够独立发挥作用而不会牵连中心。实验表明,在该优化配置下,即使在 300 伏的边缘偏压下,沟槽仍保持接近圆形和垂直,且整个硅片的蚀刻速率更加均匀。计算机模拟也支持这些结果,显示不同聚焦环材料(硅与石英)如何改变电鞘厚度、等离子体密度以及垂直电场强度。

这对未来存储芯片意味着什么

对非专业读者来说,核心信息是作者找到了一种方法,可以“引导”硅片边缘的不可见电场,使等离子体离子钻出更直、更一致的孔。通过将独立控制的矩形边缘偏压与电性优化的支撑结构相结合,他们既能纠正边缘倾斜,又能避免因过度提升电压而产生的不稳定性。这种方法应能帮助制造商在存储单元持续缩小的情况下,保持对深而精细结构的精确蚀刻,从而提高下一代半导体器件的良率和可靠性。

引用: Park, C., Cho, J., Um, J. et al. Enhancing uniformity in HARC etching via edge bias voltage and structural impedance variations in a rectangular voltage waveform. Sci Rep 16, 5851 (2026). https://doi.org/10.1038/s41598-026-36323-6

关键词: 等离子体蚀刻, 半导体制造, 高纵横比, 边缘偏压, 聚焦环设计