Clear Sky Science · zh

迈向将 MATLAB 模型转化为基于 FPGA 的硬件加速器

把实验室算法变为现实设备

许多现代医学和工程的突破最初是研究人员用易用工具(如 MATLAB)编写的软件。但当这些算法必须实时运行——例如从心电图(ECG)中检测危险的心律问题——它们就需要定制硬件的速度和效率。本文展示了如何可靠地将一个复杂的心跳检测神经网络从 MATLAB 转移到一种名为 FPGA 的专用芯片上,同时不牺牲医生和工程师所依赖的准确性。

为何将代码改写为芯片代码如此困难

FPGA(现场可编程门阵列)是一种因其速度快且能耗低而受青睐的可重构芯片。传统上,对它们编程需要像 VHDL 或 Verilog 这样的硬件语言,这些语言与科学家在 MATLAB 中编写的高层数学和信号处理代码相去甚远。新的工具可以自动将算法转换为硬件描述,但它们往往需要手动调整并主要关注性能:芯片运行多快、使用多少资源。缺失的,是一种能逐层、逐数值证明硬件“完全”按原软件运行的明确方法。

对每一层进行逐步检验

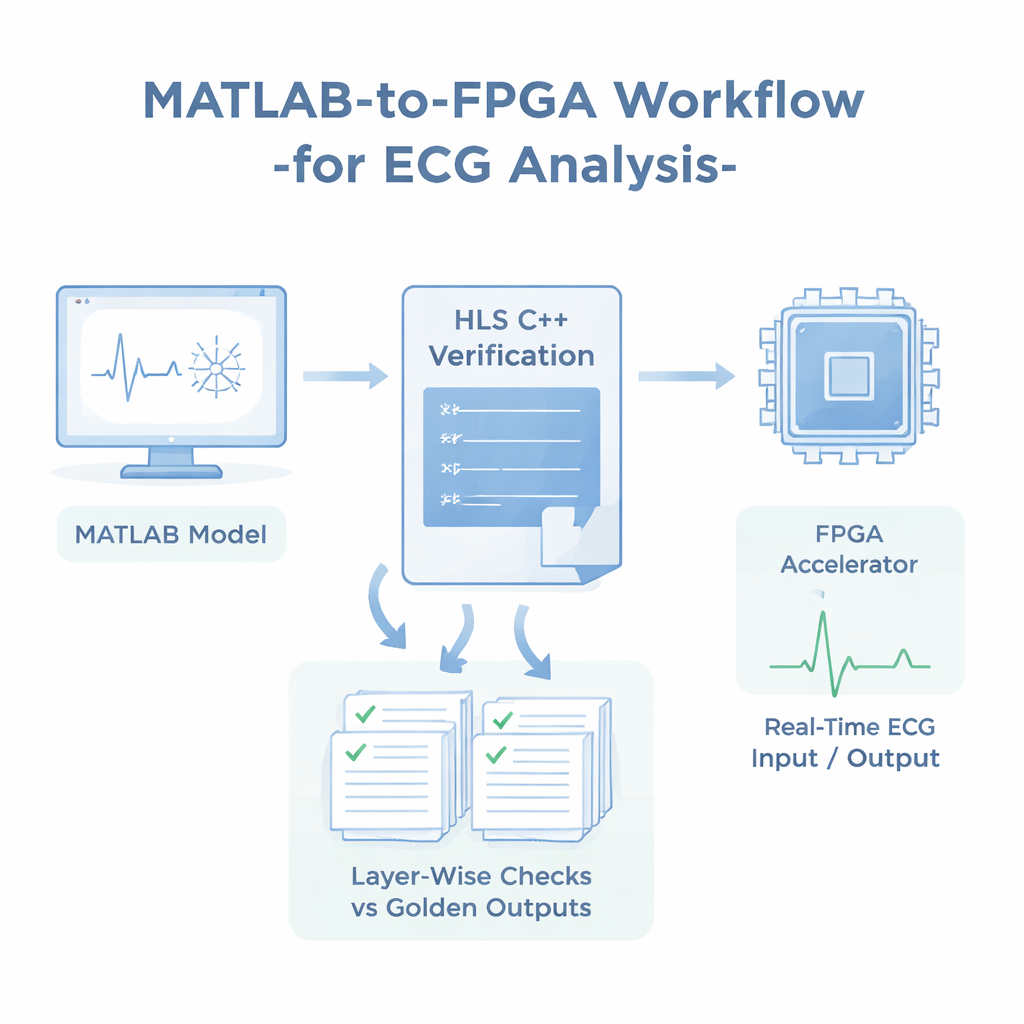

作者通过提出一种以验证为中心的工作流程来弥补这一空白,针对一个用于对心跳进行分类的一维卷积神经网络,该网络使用著名的 MIT-BIH 心律失常数据库。该网络在 MATLAB 中构建,检查短片段的 ECG 数据并将其分为五种心跳类型之一,包括正常和若干异常心律。网络有三个不同深度的版本,在相同数据上训练。训练结束后,将每一层的权重、偏置以及在测试信号上的输出保存为“黄金输出”——这是对 MATLAB 模型行为的精确数值记录。

从 MATLAB 到 C++ 再到 FPGA,同时跟踪数值

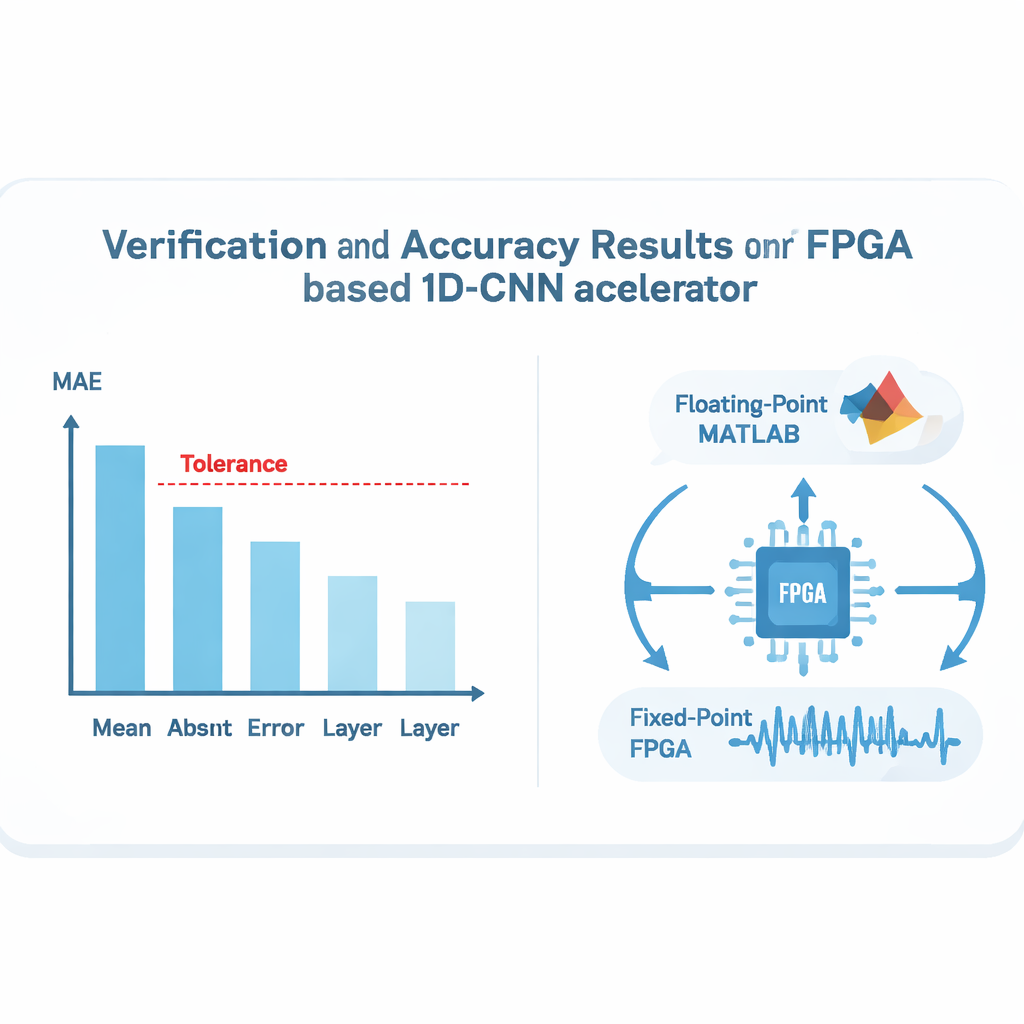

作者没有按下自动“转换”按钮,而是手工在 C++ 中重实现网络,遵循与 MATLAB 相同的数据布局和数学步骤。然后使用该 C++ 代码配合高层次综合工具生成可在 PYNQ-Z1 FPGA 板上运行的硬件。在每个阶段——MATLAB、C++ 和 FPGA——都将各层输出与保存的黄金输出进行比较,采用一个简单的度量:平均绝对误差,用以衡量两组结果之间的平均数值差异。研究设置了严格的容差:所有层的误差必须低于 1.5×10⁻³。在数千个 ECG 样本上,所有测试层均满足该目标,最终分类精度几乎不变:MATLAB 和 C++ 的准确率约为 98.3–98.4%,而 FPGA 上仅低约 0.2 个百分点,这一差异与在硬件中使用更短定点数时预期的影响一致。

在不破坏数学精度的前提下提升硬件速度

在确保正确性之后,设计被调优以提高速度。网络中最耗资源的部分——卷积层——被映射到 FPGA 的可编程逻辑上,采用定点算术以提高效率,而诸如最终 softmax 计算等较轻的任务则在芯片内置处理器上以常规浮点数执行。诸如循环流水线、循环展开以及将内存谨慎地拆分为并行银行等技术,使计算与数据传输的不同部分可以并行运行。优化后的硬件可在约 1.7 毫秒内处理一个心跳窗口,并且在 FPGA 的资源和功耗限制内运行良好,同时保留了原始 MATLAB 模型的逐层数值行为。

这对未来智能设备意味着什么

对非专业读者而言,关键结论是:现在不仅可以在低功耗芯片上加速一个复杂的基于 MATLAB 的心律分类器,而且可以证明该芯片的内部工作在每一层上都与受信任的软件模型高度一致。与其以牺牲可靠性来追求速度,这种方法建立了从浮点 MATLAB 代码到定点 FPGA 硬件的清晰审计轨迹。相同的验证流程——保存黄金输出、将逐层误差与严格阈值比较并检查最终准确率——可应用于其他一维神经网络领域,例如可穿戴健康监测器、工业传感器和智能车辆,帮助确保当算法离开实验室进入设备时,其决策仍然可信赖。

引用: Bal, S. Towards the transformation of MATLAB models into FPGA-Based hardware accelerators. Sci Rep 16, 5027 (2026). https://doi.org/10.1038/s41598-026-36033-z

关键词: FPGA 加速器, MATLAB 神经网络, 心电图心律失常分类, 硬件验证, 定点深度学习