Clear Sky Science · zh

晶圆级高κ HfO2 介电薄膜,实现亚5 Å 等效氧化层厚度,用于二维 MoS2 晶体管

为何更薄的绝缘层对未来芯片至关重要

智能手机、数据中心和人工智能都依赖于称为晶体管的小型电子开关。为了在减少能耗的同时在芯片上集成更多此类开关,工程师不仅需要缩小晶体管本身,还要缩减控制其行为的绝缘层厚度。本文介绍了一种制备极薄且高质量绝缘薄膜的方法,该薄膜仍能阻止电流泄漏,并可在整片晶圆上用于前沿的二维(2D)晶体管电路。

一种新型超薄电绝缘屏障

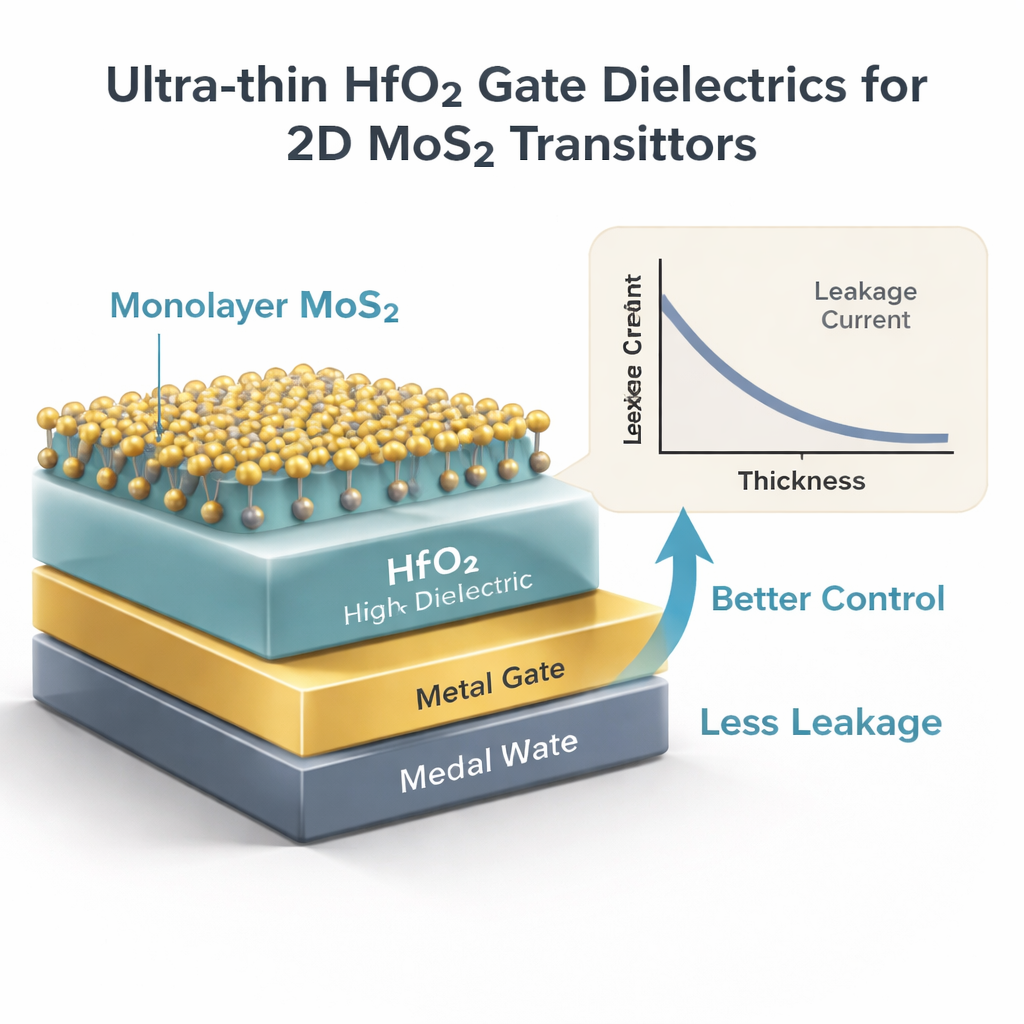

每个现代晶体管的核心都有一个“栅极”,它通过通道开关电流。栅极与通道之间是薄薄的一层绝缘体,即介电层。多年来,业界使用氧化铪(HfO2)这一所谓的高κ材料,它允许在不需要物理上很厚的情况下强力控制通道。但在原子层尺度上推进这一策略一直很困难:薄膜常常泄漏电流或在电应力下击穿。作者提出了一种改进的生长方法,称为多次氧化原子层沉积(MOALD),可制备仅 1.3 纳米厚的 HfO2 薄膜——仅几层原子——同时保持其致密且缺陷极少,从而实现可靠工作。

在原子尺度上清除缺陷

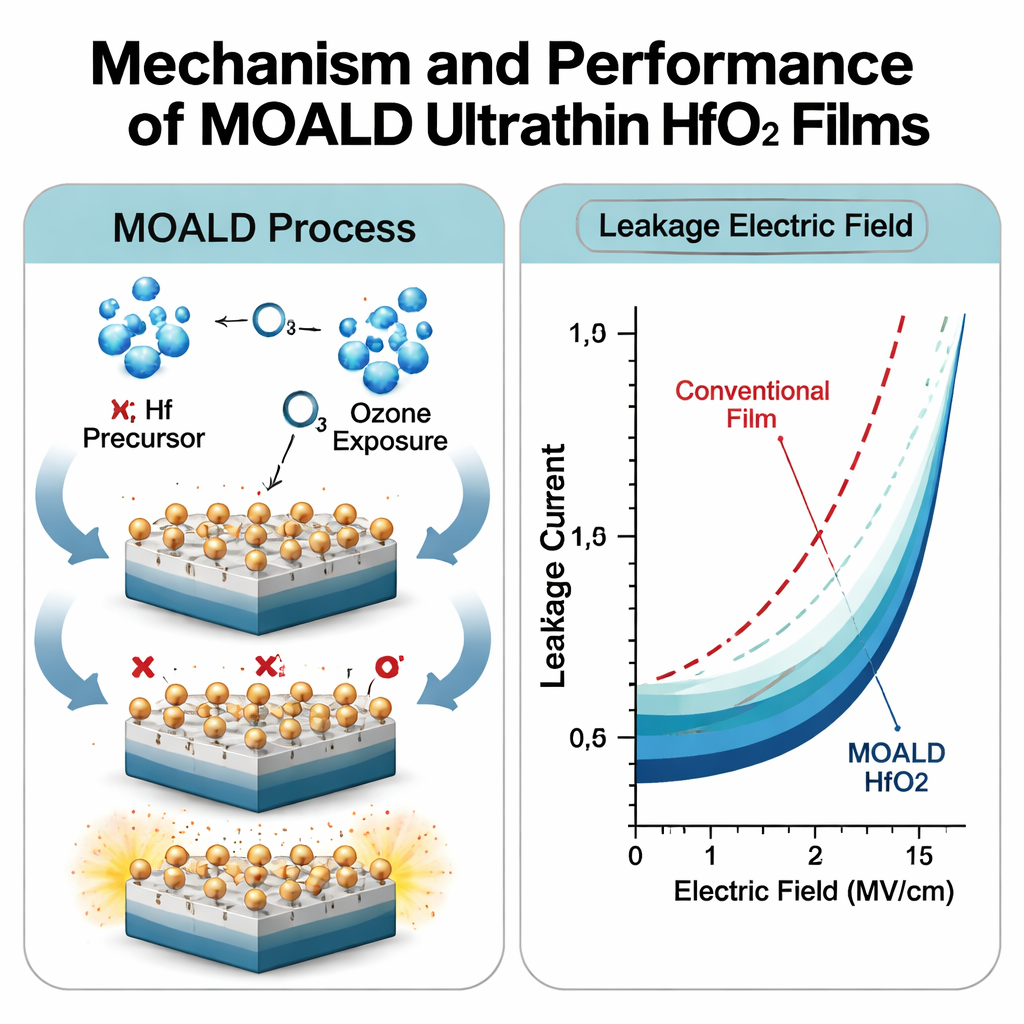

传统的 HfO2 生长通常使用单次氧化步骤,这会留下大量缺少氧原子的缺陷。这些缺陷像电子的捷径,削弱了绝缘性能。在 MOALD 方法中,每个生长循环包括两次氧化,先用臭氧然后用氧等离子体。显微镜和光谱分析表明,这种串联处理显著减少了氧空位,使得即便在 1.3 纳米厚度下也能得到更平滑、更连续的薄膜。计算机模拟支持这一结论:当缺陷丰富时,材料的电子带隙收窄且在带隙内出现额外态,从而更容易发生击穿;当缺陷被最小化时,带隙扩大,泄漏通道被抑制,恢复了介电层的强度。

创纪录的超薄绝缘同时低泄漏

团队在简单的金属–绝缘体–金属测试结构中测量了这些超薄薄膜。尽管其物理厚度极小,HfO2 层在电控方面表现得像传统二氧化硅的更薄等效层,达到仅 2.5 埃的等效氧化层厚度。这低于国际路线图对未来逻辑器件提出的激进目标。关键是,在工作电压下,泄漏电流保持在每平方厘米低于百万分之一安的水平,且薄膜在击穿前能承受超过 22 兆伏每厘米的电场。与多种实验替代材料(如奇异钙钛矿、分子晶体及其它高κ 氧化物)比较时,这些薄膜在极小的等效厚度、低泄漏和强击穿特性之间达成了此前材料难以兼得的组合。

让二维晶体管与电路更接近实用

为证明新型介电层并非实验室好奇,作者将其与单层二硫化钼(MoS2)集成,MoS2 是作为可能替代硅的二维半导体而被广泛研究的材料。他们构建了两类器件:先栅(gate‑first)晶体管,即在添加 MoS2 之前生长介电层;以及后栅(gate‑last)晶体管,即在已有 MoS2 层上用一层薄的氧化锑“种子”层沉积介电层。在两种情况下,器件开关表现良好,开关电流比约为一亿比一,阈下斜率接近理论热极限。短沟道的 MoS2 晶体管(沟长仅 100 纳米)在适度电压下可提供高达每微米 260 微安的导通电流密度,同时栅极泄漏极低。

从单个器件到整片晶圆电路

任何新材料方法的关键测试是能否扩展到工业使用的大尺寸晶圆。研究者在一片 8 英寸硅晶圆上以仅 200 °C 的温度均匀生长了 1.3 纳米的 HfO2 层,这一温度与标准芯片制造工艺以及脆弱的二维材料兼容。在此基础上,他们制备了晶圆级的 MoS2 逻辑电路,包括反相器、基本逻辑门如 AND、NAND 和 NOR,以及五级环形振荡器。这些电路在异常低的供电电压(降至 0.1–0.2 伏)下仍能正确工作,具有高增益并消耗极小的静态功率,说明超薄高质量介电层可直接转化为低能耗计算。

这对日常电子设备意味着什么

对于非专业读者,结论是作者制造出了用于晶体管的最薄实用电绝缘体之一,并且能以工业友好的方法在整片晶圆上批量生产它。通过仅几层原子就能严格控制电流,这些 HfO2 薄膜使得二维 MoS2 晶体管切换更快、能耗更低。如果这类技术能进一步完善并集成到商业工艺中,便有望延续向更小、更高效电子器件发展的趋势,为从移动设备到大规模 AI 硬件的应用带来更强大且更节能的未来芯片。

引用: Zhang, S., Zhang, T., Yu, H. et al. Wafer-scale high-κ HfO2 dielectric films with sub-5-Å equivalent oxide thickness for 2D MoS2 transistors. Nat Commun 17, 1888 (2026). https://doi.org/10.1038/s41467-026-68584-0

关键词: 高κ 介电材料, 氧化铪, 二维 MoS2 晶体管, 超薄栅绝缘层, 低功耗电子学