Clear Sky Science · tr

Hafıza içi çarpıp-topla hesaplama hatalarını LDPC ile düzeltme

Hafıza içi matematik hatalarını düzeltmenin önemi

Günümüz yapay zeka çipleri, veriyi ayrı işlemcilere sürekli taşımanın yerine hesaplamaları doğrudan belleğin içinde yaparak donanımdan daha fazla hız ve verim elde ediyor. Bu “hafıza içinde işleme” yaklaşımı enerji tasarrufu sağlasa da önemli bir sorun getiriyor: küçük elektriksel kusurlar saklanan bitleri çevirebilir veya analog sinyalleri bozarak görüntü tanıma gibi görevlerin doğruluğunu sessizce düşürebilir. Makale, bu hataları anında otomatik olarak algılayıp düzelten yeni bir yöntemi anlatıyor; bu sayede geleceğin yapay zeka donanımları hem hızlı hem de güvenilir kalabiliyor.

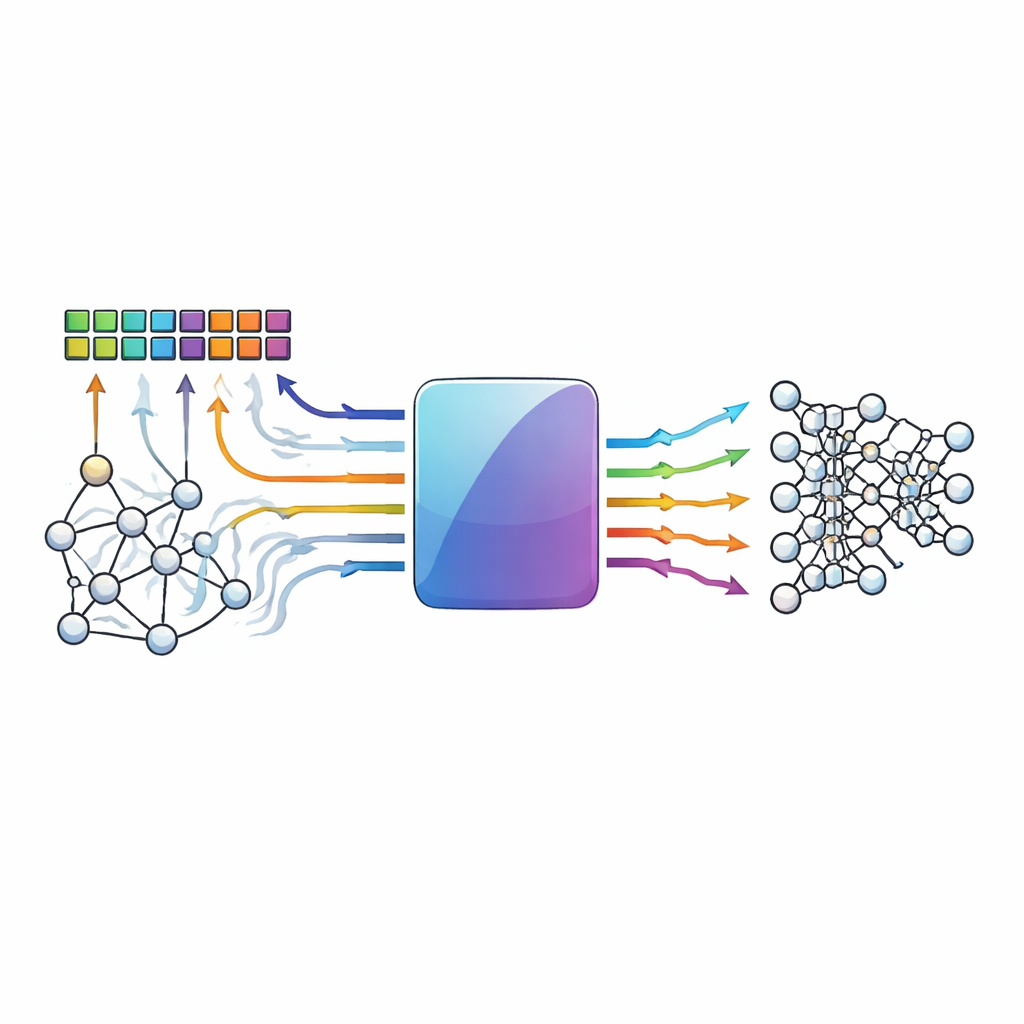

Verinin yaşadığı yerde hesaplama

Geleneksel bilgisayarlar, veriyi bellek ile işlemci arasında taşımak zorunda oldukları için yavaşlar. Hafıza içi tasarımlar, sinir ağlarının temelini oluşturan çarpıp-topla (multiply-and-accumulate) işlemlerini yoğun bellek hücresi dizileri içinde gerçekleştirerek bu darboğazı ortadan kaldırır. Dirençli RAM ve diğer memristif elemanlar gibi yeni cihazlar, birçok değeri depolayıp analog tarzı aritmetiği çok verimli yapabildikleri için özellikle caziptir. Ancak bu cihazların analog doğası ve cihazlar arası değişkenlik onları güçlü kılarken aynı zamanda gürültülü de yapar: termal dalgalanmalar, cihaz uyumsuzlukları ve voltaj düşüşleri saklanan değerleri veya hesaplanan sonuçları olması gereken yerden saptırabilir.

Küçük aksaklıklar birikince

Bu hafıza içi dizilerde birçok hücre satırı birlikte etkinleştirilir ve katkıları ortak kablolar boyunca toplanır. Daha fazla satır katıldıkça, bireysel kusurları toplanır ve hem sık hem de karmaşık hata örüntüleri oluşturur. Tek bir yanlış bitten ziyade, tasarımcılar sık sık bir matrisin aynı sütununda kümelenmiş çoklu hatalar veya geleneksel hata düzeltme yöntemlerini etkisiz kılan birden fazla sütuna yayılan hatalar görürler. Standart kodlar genellikle basit hata örüntülerini ve kısa sözcük uzunluklarını varsayar; çok bitli aksaklıkları kaçırabilir veya nadir ama zararlı kombinasyonlar için arama tablolarında giriş eksikliği yaşayabilir. Sonuç olarak, temel donanım biraz güvenilmez hale geldiğinde derin sinir ağlarının model doğruluğu hızla düşebilir.

Yeni tür bir dijital emniyet ağı

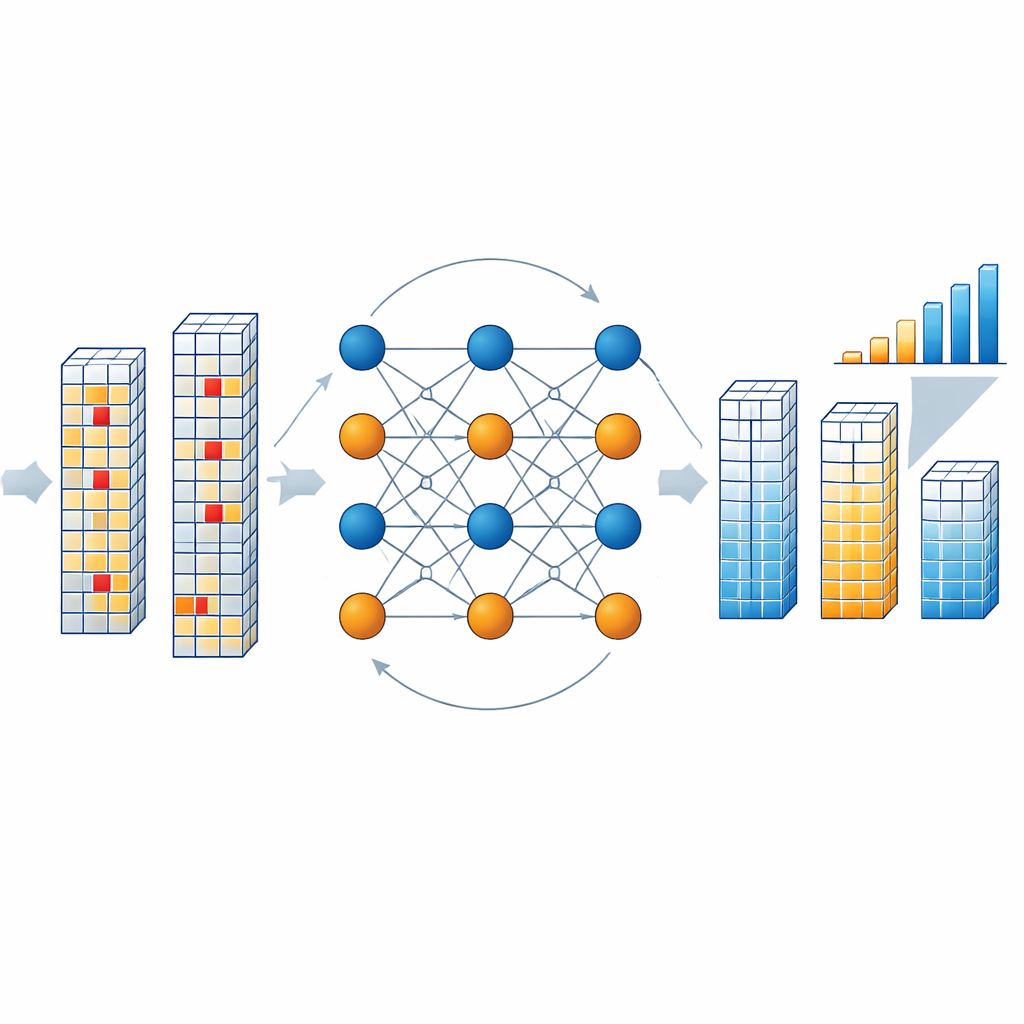

Yazarlar, hafıza içi donanıma özel olarak uyarlanmış ikili olmayan düşük yoğunluklu eşlik-kontrol (NB-LDPC) kodu tanıtıyor. Yalnızca sıfır ve birlerle çalışmak yerine, şemaları asal bir sayıdan (burada üç) oluşturulmuş sonlu bir alan içinde semboller olarak ele alınan küçük bit grupları üzerinde işlem yapıyor. Bu, aynı kodun hem normal ikili depolamayı hem de analog hızlandırıcılarda yaygın olarak kullanılan çok seviyeli veya diferansiyel kodlamaları korumasına izin veriyor. Sistem her veri bloğuna mütevazı sayıda ek sembol—kontrol sembolleri—ekliyor. Hem normal bellek okumaları sırasında hem de hafıza içinde çarpıp-topla işlemleri yapılırken donanım, veri ve kontrol sembollerinin sonuçlarını birlikte hesaplıyor; böylece hata algılama hesaplamanın içine doğal olarak örülmüş oluyor.

Düzeltme motorunun çip içindeki işleyişi

Çip bir sonuç bloğunu okuduğunda, ayrılmış bir çözücü (decoder) veri ve kontrol sembollerinin kod tarafından tanımlanan eşlik ilişkilerine uyup uymadığına bakar. Uygunlarsa blok temiz kabul edilir. Değilse çözücü, her sembolü temsil eden “değişken düğümler” ile eşlik koşullarını temsil eden “kontrol düğümleri”nin olasılık mesajları alışverişi yaptığı yinelemeli bir süreci başlatır. Bu mesajlar, gözlemlenen çıktılara ve belleğin beklenen bit-flip hata oranına dayanarak her sembolün izin verilen değerleri alma olasılığını tahmin eder. Yazarlar, bu matematik ağırlıklı akıl yürütmeyi Manhattan mesafesi yaklaşımlarıyla basitleştiriyor; bu, donanım maliyetini büyük ölçüde azaltırken performansı yüksek tutuyor. Genellikle üç tur içinde çözücü, belleği yeniden okumaya veya hesaplama akışını durdurmaya gerek kalmadan, sonuç vektörünün en makul düzeltilmiş versiyonuna yakınsıyor.

Silisyum doğrulaması ve yapay zekâ doğruluğuna etkisi

Fikri pratikte test etmek için ekip, dirençli RAM dizisi, hafif analogdan-dijitale dönüştürücüler ve yeni NB-LDPC çözücüsünü birleştiren 40 nanometre bir süreçte prototip bir çip inşa etti. 256 bilgi sembolünü 32 kontrol sembolüyle koruyan bir yapılandırmayla çözücü yüksek bir kod oranı (yaklaşık 0,8), watt başına düzeltilmiş veri başına yaklaşık 88 terabit gibi ölçülen yüksek bir güç verimliliği ve birkaç bellek makrosu arasında bir çözücü paylaşarak daha da azaltılabilecek yalnızca mütevazı bir alan overhead'i elde ediyor. Birçok kod boyutu üzerinde yapılan simülasyonlar, 1024 veri sembolünü 128 kontrol sembolüyle korurken şemanın bit hata oranını neredeyse 60 kata kadar iyileştirebildiğini gösteriyor. İşlem hafızası içinde çalışan bir ResNet-34 görüntü sınıflandırma modeline uygulandığında, bu düzeltme zorlu hata koşullarında kaybedilen doğruluğun 20'den fazla yüzde puanını geri getiriyor.

Gelecek yapay zeka çipleri için anlamı

Basitçe söylemek gerekirse, çalışma hafıza içi donanım için zengin sembol setlerini ve karmaşık hata örüntülerini anlayan, veri akışını yavaşlatmayan sağlam bir “yazım denetleyicisi” sağlıyor. Hem saklanan veriyi hem de anlık hesaplamaları korumayı birleştirerek ve verimli bir silisyum uygulaması göstererek çalışma, yüksek yoğunluklu, düşük güçlü hafıza içi hızlandırıcıların güvenilirlikten ödün vermek zorunda olmadığını gösteriyor. Bu tür özel hata düzeltme, gelecekteki nöromorfik ve yapay zekâ hızlandırıcılarını mobil cihazlardan büyük ölçekli veri merkezlerine kadar gerçek dünya uygulamaları için hem enerji verimli hem de yeterince güvenilir kılmada önemli bir bileşen haline gelebilir.

Atıf: Shi, D., Fu, Y., Zhu, Y. et al. Correcting processing-in-memory multiply-accumulate arithmetic errors with LDPC. npj Unconv. Comput. 3, 14 (2026). https://doi.org/10.1038/s44335-026-00061-9

Anahtar kelimeler: hafıza içinde işleme, hata düzeltme, LDPC kodları, dirençli RAM, sinir ağı donanımı