Clear Sky Science · tr

Kare dalga formunda kenar bias voltajı ve yapısal empedans değişimleriyle HARC aşındırmada tekdüzeliğin artırılması

Çip üreticilerinin düz deliklere neden önem verdiği

Modern bellek çipleri, milyarlarca ultra-derin, kalem inceliğinde deliği silisyuma açarak daha fazla bilgiyi daha küçük alanlara sıkıştırır. Bu "yüksek en-boy oranlı" deliklerin neredeyse kusursuz dik olması gerekir; hafif eğilme veya şekil bozulması bile bir cihazı kullanılamaz hale getirip üretim verimini düşürebilir. Bu çalışma, plazma aşındırma sırasında wafer kenarındaki elektrik alanlarının nasıl davranacağını ince ince ayarlayarak bu deliklerin tüm wafer boyunca düz ve uniform kalmasını sağlayan yeni bir yöntemi gösteriyor.

Wafer’ın hassas sınırının sorunu

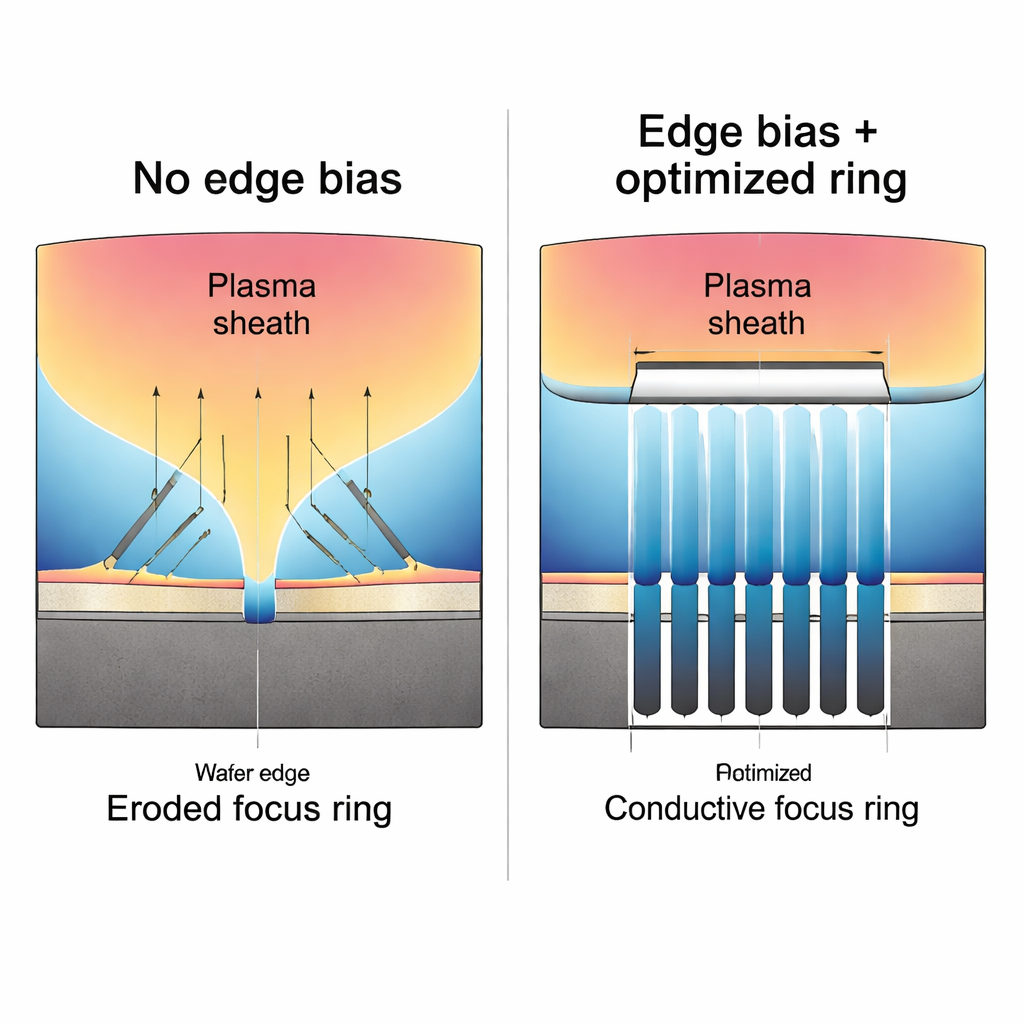

Wafer üzerine desen açmak için üreticiler plazma kullanır — enerji dolu iyonlarla dolu parlayan bir gaz, malzemeyi aşındırır. Wafer çevresinde, plazmanın merkezden kenara kadar dengeli kalmasına yardımcı olan fedakâr bir "focus ring" bulunur. Zamanla bu halka aynı sert ortam tarafından aşınır. Aşındıkça, iyonları wafer’a yönlendiren elektrik örtüsü (sheath) kenar yakınında bozulur. İyonlar dik olarak gelmek yerine açıyla gelir, bu da deliklerin merkeze doğru eğilmesine ve elips şeklini almasına yol açar. Bu sadece küçük kondansatör yapılarını bozmakla kalmaz, aynı zamanda kullanılabilir alanı azaltır ve verimi düşürür.

Kenar için kontrol edilebilir bir "direksiyon" eklemek

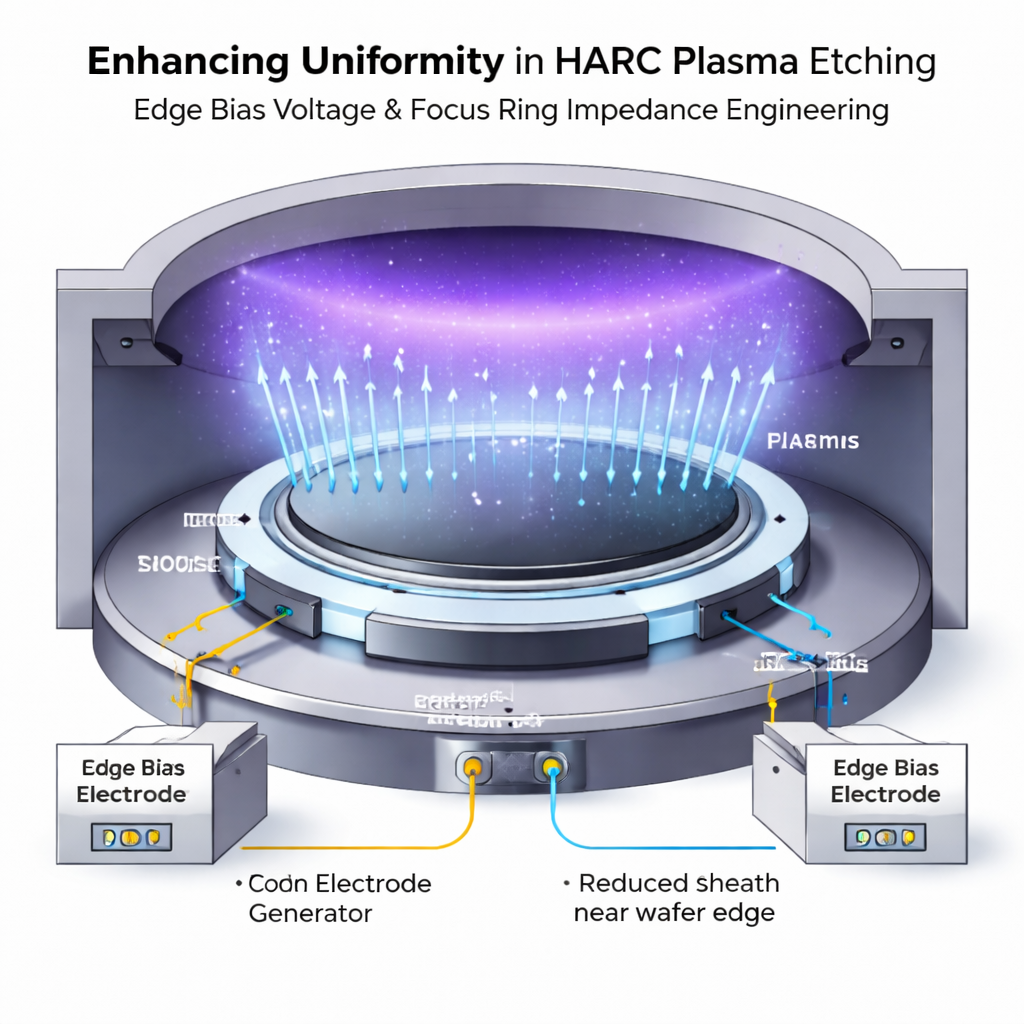

Araştırmacılar bunu, focus ring’in altına bağımsız olarak kontrol edilen bir kenar elektrodu ekleyerek çözdü; bu elektrodun beslemesi ana wafer bias’ından ayrı, dikdörtgensi bir bias voltajıydı. Alışılmış pürüzsüz sinüs dalgası yerine bu kareye yakın dalga biçimi keskin geçişlerle açık ve kapalı arasında değişerek plazma ile yüzey arasındaki voltaj farkını zamana göre daha sabit tutar. Bu daha istikrarlı itiş, iyonların daha dar bir enerji ve açı dağılımıyla gelmesini sağlar. Kenar bias’ını dikkatlice yükselterek ekip, wafer kenarındaki elektrik örtüsünü güçlendirebildi ve yeniden şekillendirerek iyon yollarını dikeye çekti; böylece focus ring aşınmış olsa bile çukur profilleri dairesel ve iyi tanımlı biçimde geri getirildi.

Daha yüksek güç bazen işleri kötüleştirir

Ancak kenar voltajını çok yükseltmek yeni bir sorun yarattı. Yaklaşık 280–300 voltun üzerinde, kenar ve merkez elektrotları arasındaki elektriksel etkileşim plazma üzerinden istenmeyen akım kaçaklarına neden oldu. Ölçümler, ekipmanın uygulamaya çalıştığı voltaj ile wafer’ın gerçekten gördüğü voltaj arasında artan uyumsuzluklar ve wafer bölgesinde yükselen akımlar gösterdi. Bu, hassas şekilde ayarlanmış örtüyü bozdu, plazmayı kararsız hale getirdi ve yine heterojen aşındırmayı gündeme getirdi: orta bölgeler daha hızlı aşındı, kenar yavaşladı ve delik şekilleri, kenar bias’ı daha yüksek olmasına rağmen yeniden bozuldu.

Alanları dizginlemek için donanımı yeniden tasarlamak

Yüksek voltajlarda kontrolü geri kazanmak için ekip, wafer çevresindeki yalıtkan ve iletken parça yığını — özellikle focus ring altı ve çevresindeki malzemeleri — yeniden mühendislik yaptılar. Bileşenleri değiştirip elektriksel özelliklerini değiştirerek, focus ring yolu ile wafer chuck arasındaki empedans oranını ayarladılar. Yaklaşık 1.31 civarındaki daha yüksek bir oran, iki bias devresi arasındaki istenmeyen koppengini sınırlayarak kenar bias’ının merkezi sürüklemeden işini yapmasına izin verdi. Deneyler, bu optimize edilmiş konfigürasyonla kenar bias’ı 300 volt olsa bile hendeklerin neredeyse dairesel ve dik kaldığını, aşındırma hızının ise wafer boyunca çok daha uniform olduğunu gösterdi. Bilgisayar simülasyonları da bunu destekleyerek farklı focus ring malzemelerinin (silikon vs kuvars) sheath kalınlığını, plazma yoğunluğunu ve dikey elektrik alanın gücünü nasıl değiştirdiğini ortaya koydu.

Gelecek bellek çipleri için bunun anlamı

Uzman olmayanlar için ana mesaj, yazarların wafer kenarındaki görünmez elektrik alanlarını "yönlendirecek" bir yol bulmuş olmalarıdır; böylece plazma iyonları daha dik ve daha tutarlı delikler açar. Ayrı kontrol edilen, dikdörtgensi bir kenar bias’ı ile elektriksel olarak optimize edilmiş bir taşıyıcı yapıyı birleştirerek, kenar eğilmesini düzeltebiliyor ve voltajları çok yükseltmenin yol açtığı kararsızlıklardan kaçınabiliyorlar. Bu yaklaşım, bellek hücreleri küçülmeye devam ettikçe üreticilerin hassas, derin yapıları aşındırmasını kolaylaştırmalı; böylece gelecek nesil yarıiletken cihazlarda verim ve güvenilirlik artacaktır.

Atıf: Park, C., Cho, J., Um, J. et al. Enhancing uniformity in HARC etching via edge bias voltage and structural impedance variations in a rectangular voltage waveform. Sci Rep 16, 5851 (2026). https://doi.org/10.1038/s41598-026-36323-6

Anahtar kelimeler: plazma aşındırma, yarıiletken üretimi, yüksek en-boy oranı, kenar bias voltajı, focus ring tasarımı