Clear Sky Science · sv

Korrigering av multiply-accumulate‑fel i processing-in-memory med LDPC

Varför det är viktigt att åtgärda beräkningsfel i minnet

Moderna artificiell intelligens‑kretsar pressar ut mer hastighet och energieffektivitet ur hårdvaran genom att utföra beräkningar direkt i minnet, istället för att ständigt skicka data fram och tillbaka till separata processorer. Detta ”processing‑in‑memory”‑angreppssätt sparar energi men introducerar ett allvarligt problem: små elektriska imperfektioner kan vända lagrade bitar eller förvränga analoga signaler och tyst försämra noggrannheten i uppgifter som bildigenkänning. Artikeln beskriver ett nytt sätt att automatiskt upptäcka och korrigera dessa fel i farten, vilket hjälper framtida AI‑hårdvara att förbli både snabb och pålitlig.

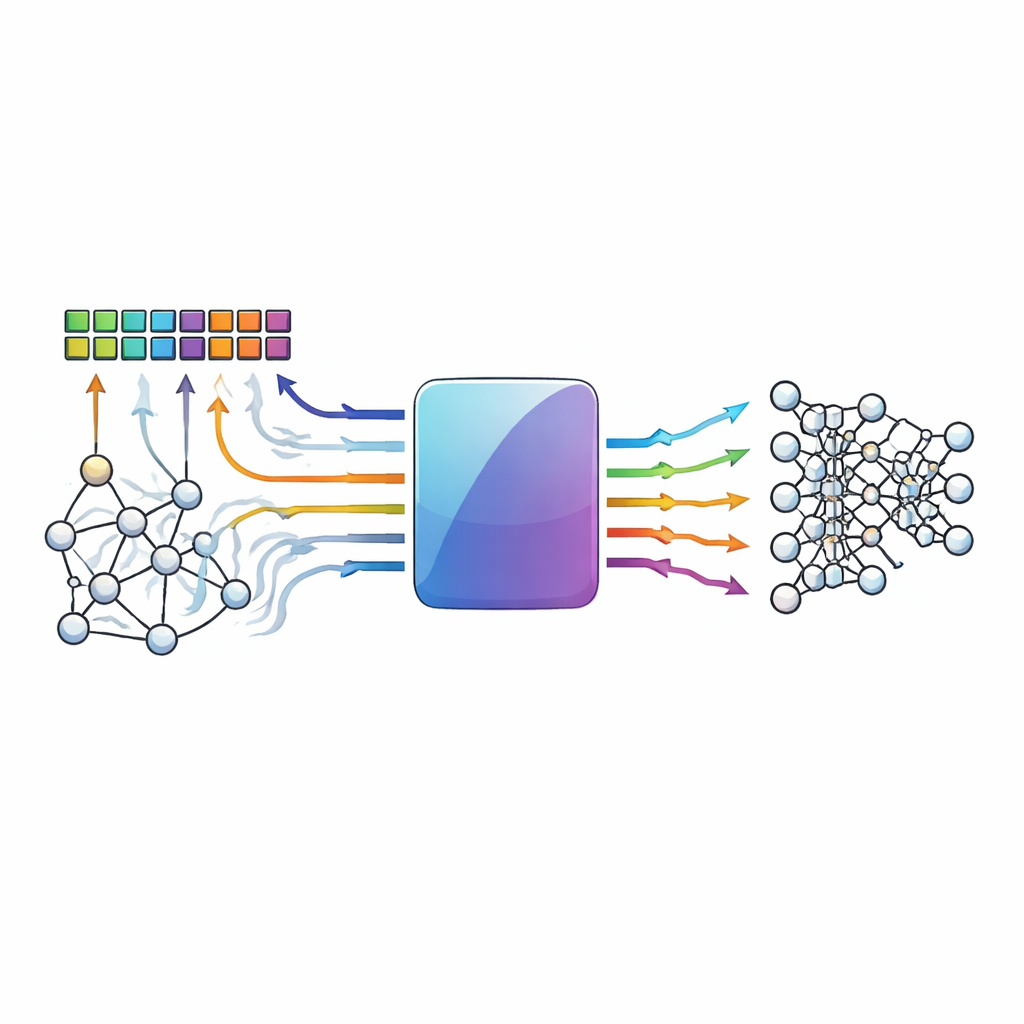

Att beräkna där data finns

Konventionella datorer bromsas av behovet att flytta data mellan minne och processor. Processing‑in‑memory‑designer undviker denna flaskhals genom att utföra multiply‑and‑accumulate‑operationer—ryggraden i neurala nätverk—inne i täta matriser av minnesceller. Framväxande enheter såsom resistiv RAM och andra memristiva element är särskilt attraktiva eftersom de kan lagra många värden och utföra analog‑liknande aritmetik mycket effektivt. Men samma analoga natur och enhetsvariabilitet som gör dem kraftfulla gör dem också bullriga: termiska fluktuationer, avvikelser mellan enheter och spänningsfall kan alla knuffa lagrade värden eller beräknade resultat bort från där de borde vara.

När små störningar bygger upp

I dessa in‑memory‑matriser aktiveras många rader av celler samtidigt och deras bidrag summeras längs delade ledare. När fler rader deltar adderas deras individuella imperfektioner, vilket skapar felmönster som både är frekventa och komplicerade. I stället för enstaka felande bitar ser konstruktörer ofta multipla fel klustrade i samma kolumn i en matris eller spridda över flera kolumner på ett sätt som slår ut traditionella felkorrigeringsmetoder. Standardkoder antar vanligtvis enkla felmönster och korta ordlängder; de kan missa flervals‑fel eller sakna entydigheter i sina uppslagslistor för sällsynta men skadliga kombinationer. Som ett resultat kan modellens noggrannhet för djupa neurala nätverk falla kraftigt när den underliggande hårdvaran blir ens måttligt opålitlig.

En ny typ av digitalt säkerhetsnät

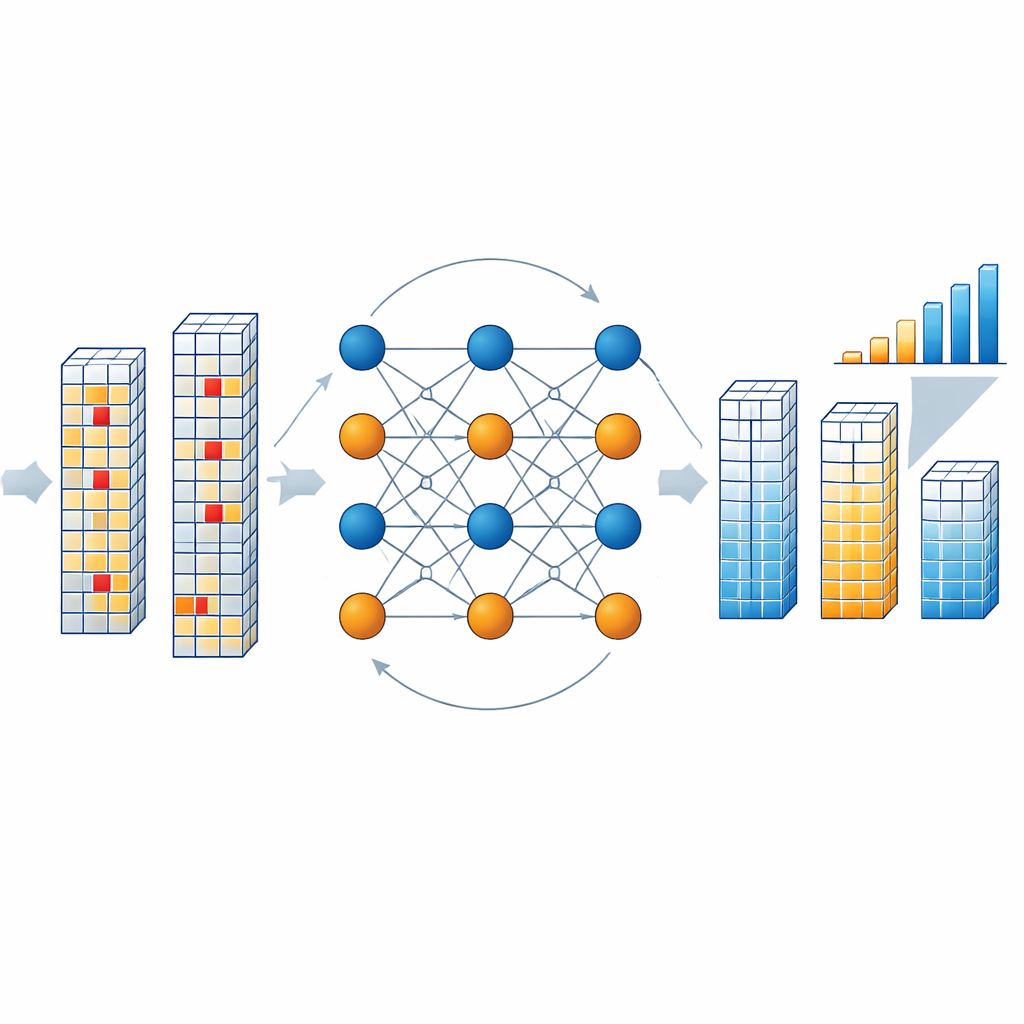

Författarna introducerar en icke‑binär low‑density parity‑check‑kod (NB‑LDPC) särskilt anpassad till processing‑in‑memory‑hårdvara. I stället för att arbeta enbart med nollor och ettor opererar deras schema på små grupper av bitar som behandlas som symboler i en matematisk struktur kallad ett ändligt fält byggt från ett primtal (här tre). Detta låter samma kod skydda både vanlig binär lagring och flervärdiga eller differentiella kodningar som ofta används i analoga acceleratorer. Systemet lägger till ett måttligt antal extra symboler—kontrollsymboler—till varje datablock. Under både normala minnesläsningar och in‑memory multiply‑and‑accumulate‑operationer beräknar hårdvaran resultat för data och kontrollsymboler tillsammans, så felupptäckt vävs naturligt in i beräkningen.

Hur korrigeringsmotorn fungerar inne i kretsen

När kretsen läser ut ett block av resultat undersöker en dedikerad avkodare om de kombinerade data‑ och kontrollsymbolerna följer paritetsrelationerna som definieras av koden. Om de gör det antas blocket vara rent. Om inte startar avkodaren en iterativ process där abstrakta ”variabelnoder” som representerar varje symbol och ”kontrollnoder” som representerar paritetsvillkor utbyter sannolikhetsmeddelanden. Dessa meddelanden uppskattar hur sannolikt det är att varje symbol antar var och en av de tillåtna värdena, baserat på de observerade utgångarna och det förväntade bitflipps‑felriktvärdet i minnet. Författarna förenklar detta matematikintensiva resonemang med Manhattan‑avståndsapproximationer, vilket kraftigt reducerar hårdvarukostnaden samtidigt som prestandan behålls hög. Efter några rundor—vanligen tre—konvergerar avkodaren till den mest troliga korrigerade versionen av resultatvektorn, utan att behöva läsa om minnet eller stoppa beräkningsströmmen.

Silicon‑bevis och påverkan på AI‑noggrannhet

För att testa idén i praktiken byggde teamet en prototypkrets i en 40‑nanometerprocess som kombinerar en resistiv RAM‑matris, lättviktiga analog‑till‑digital‑omvandlare och den nya NB‑LDPC‑avkodaren. Med en konfiguration som skyddar 256 informationssymboler med 32 kontrollsymboler uppnår avkodaren en hög kodhastighet (cirka 0,8), en bästa uppmätta energieffektivitet på ungefär 88 terabit korrigerade data per sekund och watt, samt endast blygsam area‑överhead som kan minskas ytterligare genom att dela en avkodare mellan flera minnesmakron. Simuleringar över många kodstorlekar visar att när man skyddar 1024 datasymboler med 128 kontrollsymboler kan schemat förbättra bitfelshastigheten nästan 60‑faldigt. När det tillämpas på en ResNet‑34‑bildklassificeringsmodell som körs på processing‑in‑memory‑hårdvara återställer korrigeringen mer än 20 procentenheter av förlorad noggrannhet under krävande felvillkor.

Vad detta betyder för framtida AI‑kretsar

Enkelt uttryckt ger arbetet processing‑in‑memory‑hårdvara ett robust ”stavningskontroll” för dess matematik—en som förstår rikare symboluppsättningar och komplexa felmönster utan att sakta ner dataströmmen. Genom att förena skydd för både lagrade data och beräkningar i farten, och genom att visa en effektiv kiselimplementation, visar studien att högdensitets, låg‑effekt in‑memory‑acceleratorer inte behöver offra tillförlitlighet. Denna typ av skräddarsydd felkorrigering kan bli en nyckelingrediens för att göra framtida neuromorfiska och AI‑acceleratorer både energisnåla och tillräckligt tillförlitliga för verkliga tillämpningar, från mobila enheter till storskaliga datacenter.

Citering: Shi, D., Fu, Y., Zhu, Y. et al. Correcting processing-in-memory multiply-accumulate arithmetic errors with LDPC. npj Unconv. Comput. 3, 14 (2026). https://doi.org/10.1038/s44335-026-00061-9

Nyckelord: processing-in-memory, felkorrigering, LDPC‑koder, resistiv RAM, neuralt nätverkshårdvara