Clear Sky Science · sv

Oxidhalvledare med förstärkarcell inbyggt minne: material och integreringsstrategier för nästa generations minne på chip

Varför snabbare, smartare minne spelar roll

Våra telefoner, bärbara datorer och datacenter blir allt kraftfullare, men en dold hastighetsbegränsning kvarstår: att flytta data mellan processorn och minnet. Denna artikel undersöker en ny typ av minne på chip som skulle kunna lätta på denna "minnesvägg" och göra framtidens datorer snabbare och mer energieffektiva för uppgifter som artificiell intelligens, molntjänster och vardagsappar. Genom att ompröva hur minnesceller byggs och vilka material de använder, siktar forskare på att packa mycket mer data nära processorn samtidigt som strömförbrukning och värme minskas.

Flaskhalsen inuti moderna datorer

Under årtionden har processorprestanda förbättrats mycket snabbare än huvudminnet som matar den med data. Denna obalans, känd som minnesväggen, innebär att snabba kretsar ofta står oförmögna att arbeta medan de väntar på information. Konstruktioner har försökt mildra denna flaskhals med flera lager cacheminne placerade direkt på processorn. Dagens cacheminnen bygger på en typ av minne kallad SRAM, som är mycket snabb men volymkrävande och strömkrävande eftersom varje bit data behöver sex transistorer. För att få större kapacitet staplar företag SRAM-chip i tre dimensioner eller lägger inbäddad DRAM på kretsen, men konventionell DRAM är fortfarande beroende av små kondensatorer som är svåra att tillverka i extrema skalor och svåra att integrera med standard logik-kretsar.

En annan typ av minnescell

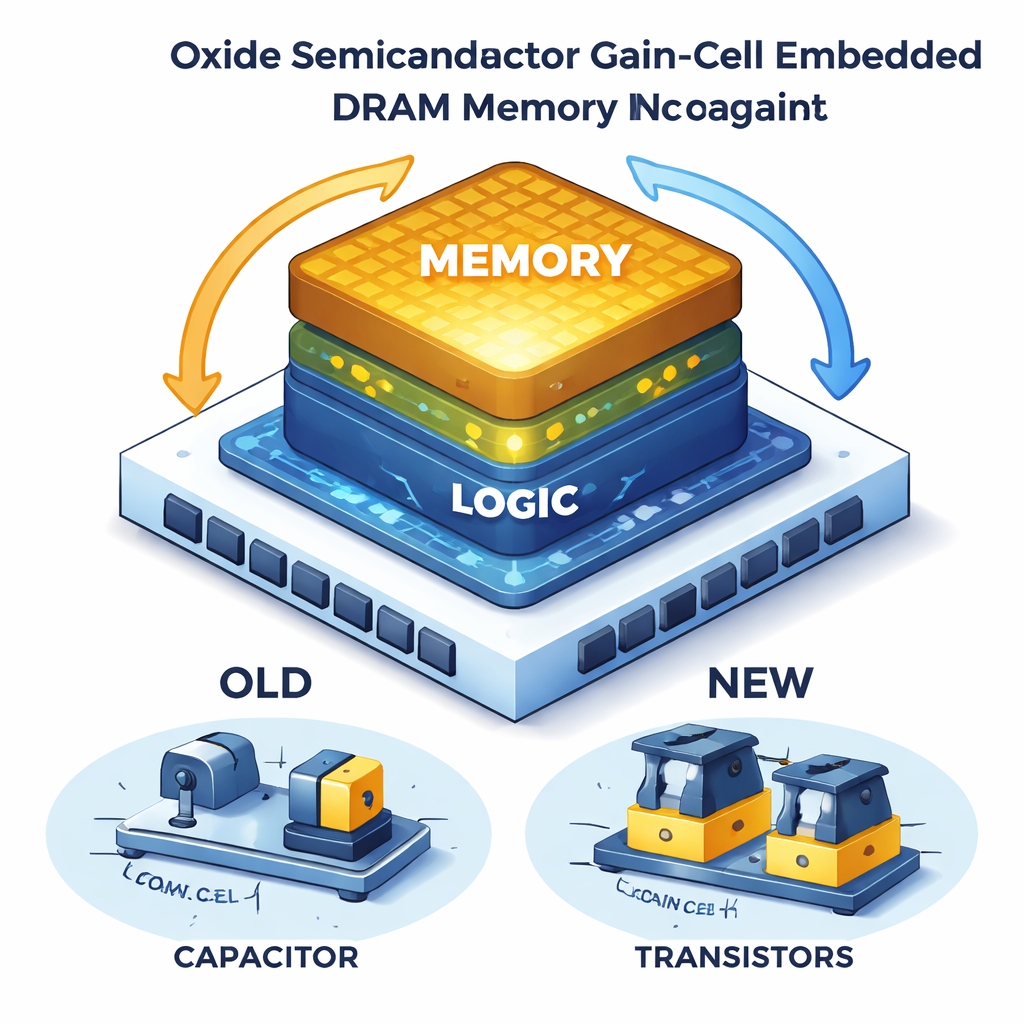

Artikeln fokuserar på ett alternativ kallat gain-cell inbyggd DRAM, eller GC-eDRAM. Istället för att använda en separat kondensator för att lagra laddning använder en gain-cell enbart transistorer för att hålla data, vilket förenklar strukturen och gör den mer vänlig mot standard tillverkning av chip. Denna design passar naturligt för tredimensionell stapling ovanpå logikkretsar och lovar högdensitets "memory-on-logic"-lösningar. En annan fördel är dess icke-destruktiva läsning: att läsa ett lagrat värde dränerar det inte omedelbart, vilket kan minska hur ofta minnet måste uppfriskas. I traditionella kiselversioner läcker dock den lagrade laddningen bort på mindre än en millisekund, så frekventa uppfriskningar slösar fortfarande energi och begränsar användbarheten.

Oxidhalvledare: tystare, svalare brytare

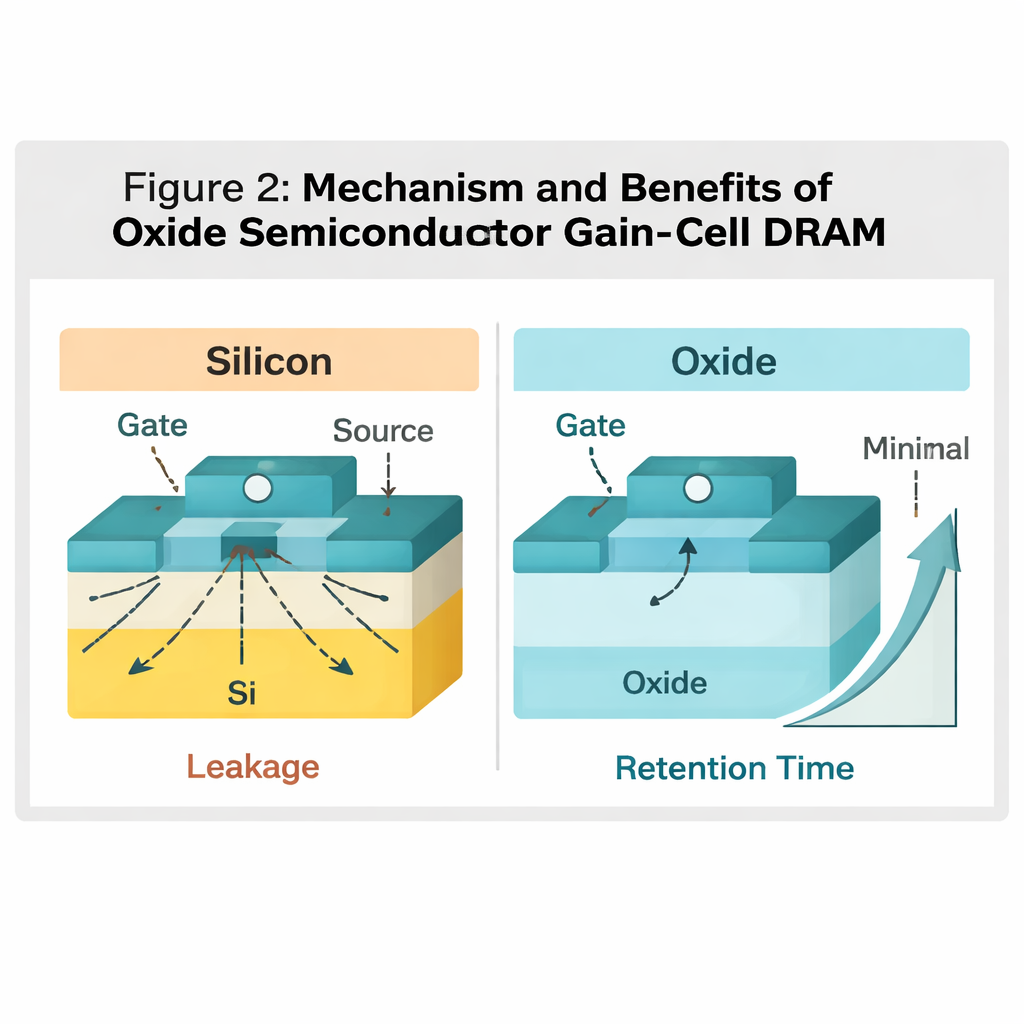

För att övervinna läckage i gain-celler lyfter författarna fram oxidhalvledare — material som indium-gallium-zinkoxid (IGZO) och närbesläktade föreningar — som nya kanalmaterial för transistorerna. Dessa oxider har ett stort bandgap, vilket starkt undertrycker oönskad ström när en transistor ska vara avstängd. Experiment har mätt avströmningar så små att de närmar sig gränserna för mätutrustning, och prototyp-gain-celler håller nu data i många sekunder, timmar eller till och med mer än en dag, jämfört med tusendelar av en sekund i kiselbaserade konstruktioner. Viktigt är att dessa oxider kan deponeras vid relativt låga temperaturer som är kompatibla med "back-end" i kretstillverkning, vilket tillåter ingenjörer att bygga täta minneslager direkt ovanpå befintlig kisel- logik utan att skada den.

Bygga uppåt: 3D-staplar och pyttesmå transistorer

När kretsar fortsätter att krympa leder det att göra transistorer mindre till nya problem, såsom dålig kontroll över kanalen och ökat läckage. Artikeln går igenom avancerade transistorformer som omsluter kanalen med grindar (gate-all-around och channel-all-around-designs) för att bibehålla tät kontroll även i nanometerskala. Genom att använda oxidhalvledare i dessa flergate-strukturer har forskare demonstrerat mycket korta kanaler, extremt lågt läckage och stark databehållning samtidigt som flera minneslager staplas vertikalt. Vissa experimentella konstruktioner når redan eller överträffar arealeffektiviteten hos dagens bästa DRAM-celler, vilket tyder på att framtida kretsar kan rymma enorm minneskapacitet i ett mycket litet avtryck direkt ovanför processorkärnorna.

Från laboratoriematerial till pålitliga produkter

Att förvandla dessa lovande enheter till praktiskt minne kräver noggrann materialteknik. Artikeln beskriver hur justering av metalldelen i oxiden, kontroll av syreinnehåll och kristallisering av filmer kan balansera hög hastighet med långsiktig stabilitet. Den tar också upp sätt att hantera defekter, väteföroreningar och de känsliga gränssnitten mellan oxider och isolerande lager så att enheterna förblir stabila under värme och långvarig drift. Slutligen diskuteras hur man konstruerar metallkontakter så att kontaktresistansen inte upphäver fördelarna med de nya materialen. Tillsammans syftar dessa strategier till att leverera minne som både är tätt packat och tillräckligt pålitligt för storskalig tillverkning.

Vad detta betyder för vardaglig databehandling

Författarna drar slutsatsen att oxidhalvledare-baserade gain-cell-minnen kan omforma hur framtida chip byggs. Genom att kombinera små, lågläckage minnesceller med 3D-stapling över logikkretsar skulle konstruktörer kunna placera mycket mer snabbt minne intill processorn samtidigt som energianvändningen hålls i schack. Detta skulle lindra minnesväggen och hjälpa allt från AI-acceleratorer till molnservrar och personliga enheter att köra snabbare och mer effektivt. Trots att utmaningar kvarstår vad gäller tillförlitlighet, tillverkningsuniformitet och fullchipintegration, skisserar arbetet som här granskas en tydlig väg mot mer kompakta, kraftfulla och energieffektiva datorsystem.

Citering: Chung, S.W., Yoon, S.H. & Jeong, J.K. Oxide semiconductor gain cell-embedded memory: materials and integration strategies for next generation on-chip memory. Commun Eng 5, 39 (2026). https://doi.org/10.1038/s44172-026-00616-5

Nyckelord: minne på chip, oxidhalvledare, DRAM-skalning, 3D-integrerade kretsar, AI-hårdvara