Clear Sky Science · sv

Mot omvandling av MATLAB-modeller till FPGA-baserade hårdvaruacceleratorer

Att förvandla laboratoriealgoritmer till verkliga enheter

Många moderna medicinska och tekniska genombrott börjar som programvara skriven av forskare, ofta i användarvänliga verktyg som MATLAB. Men när samma algoritmer måste köras i realtid — till exempel för att upptäcka farliga hjärtrytmrubbningar i ett elektrokardiogram (EKG) — behöver de snabbheten och effektiviteten hos kundanpassad hårdvara. Denna artikel visar hur man på ett tillförlitligt sätt flyttar ett komplext nätverk för hjärtslagsdetektion från MATLAB till en specialiserad krets kallad FPGA, utan att förlora den noggrannhet som läkare och ingenjörer litar på.

Varför det är så svårt att skriva om kod för kretsar

FPGAs (Field-Programmable Gate Arrays) är omkonfigurerbara kretsar uppskattade för sin snabbhet och låga energiförbrukning. Traditionellt krävde programmering av dem hårdvarunära språk som VHDL eller Verilog, som ligger långt från den hög-nivås matematik- och signalbehandlingskod som forskare skriver i MATLAB. Nya verktyg kan automatiskt konvertera algoritmer till hårdvarubeskrivningar, men de kräver ofta manuell finjustering och fokuserar främst på prestanda: hur snabbt kretsen går och hur mycket resurser den använder. Vad som har saknats är ett tydligt sätt att bevisa att hårdvaran gör exakt det som originalprogramvaran gjorde, lager för lager, tal för tal.

En steg-för-steg-kontroll för varje nätverkslager

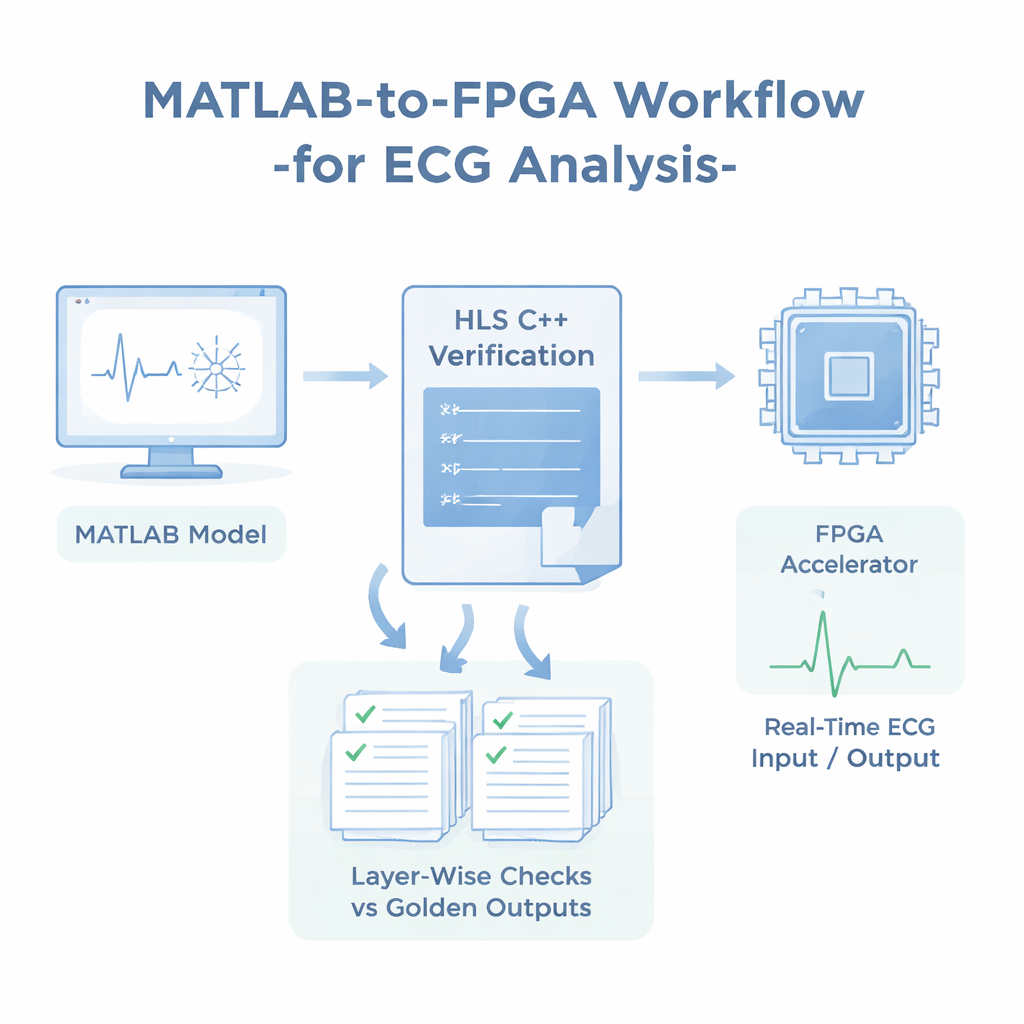

Författaren tar itu med detta gap genom att föreslå ett verifieringsfokuserat arbetsflöde för ett endimensionellt konvolutionellt neuralt nätverk som klassificerar hjärtslag från den välkända MIT-BIH Arrhythmia Database. Nätverket, byggt i MATLAB, undersöker korta utdrag av EKG-data och tilldelar dem till en av fem slagtyper, inklusive normala och flera avvikande rytmer. Tre versioner av nätverket, med olika djup, tränas på samma data. Efter träning sparas vikter, biaser och utgångarna från varje lager på testsignaler som "golden outputs" — en precis numerisk redogörelse för hur MATLAB-modellen beter sig.

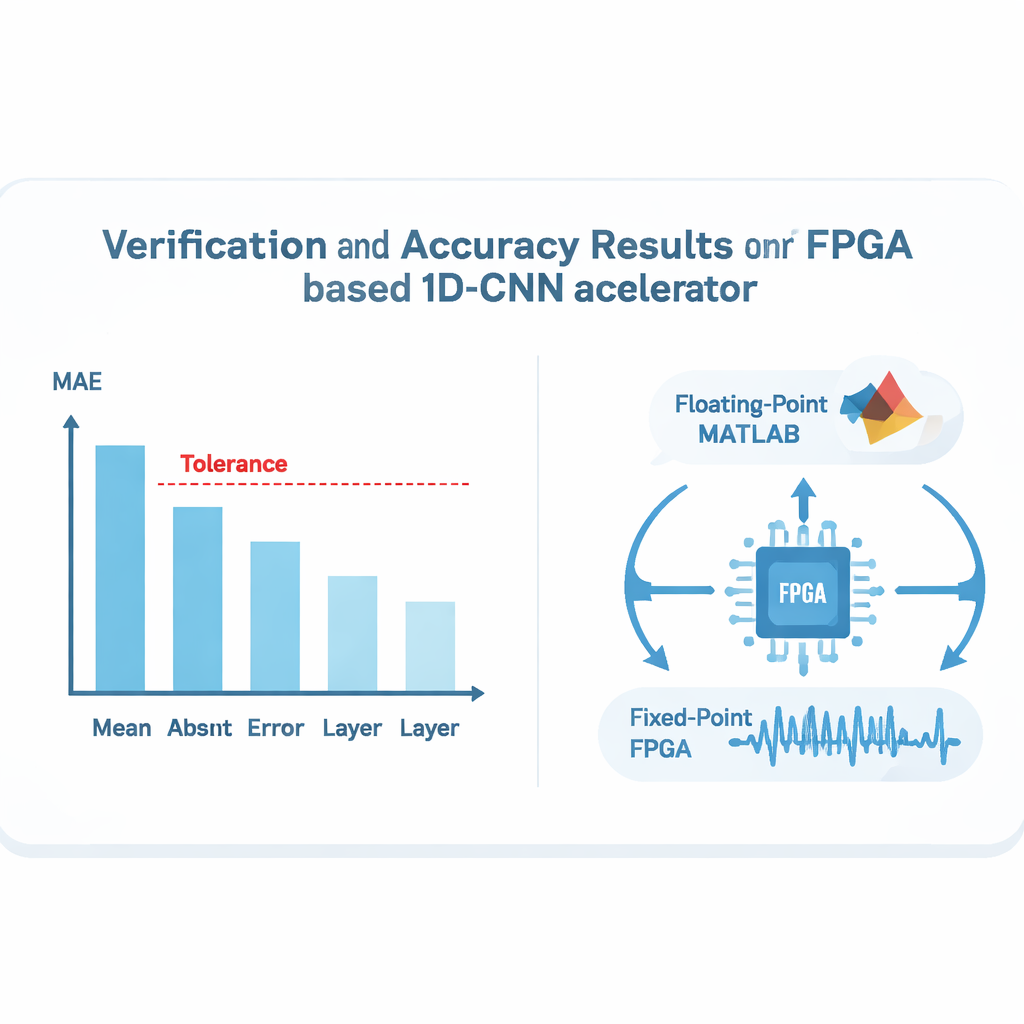

Från MATLAB till C++ till FPGA, med siffror spårade

I stället för att trycka på en automatisk "konvertera"-knapp implementeras nätverket manuellt i C++, enligt samma datalayout och matematiska steg som i MATLAB. Denna C++-kod används sedan med ett hög-nivå-syntesverktyg för att generera hårdvara som körs på ett PYNQ-Z1 FPGA-kort. I varje steg — MATLAB, C++ och FPGA — jämförs lagsutgångarna mot de sparade golden outputs med ett enkelt mått: medelabsolutfel, som mäter den genomsnittliga numeriska skillnaden mellan två uppsättningar resultat. Studien sätter en strikt tolerans: alla lager måste hålla sig under ett fel på 1.5×10⁻³. Över tusentals EKG-prov uppfyller varje testat lager detta mål, och slutlig klassificeringsnoggrannhet förblir nästan oförändrad: cirka 98.3–98.4 % i MATLAB och C++, och endast omkring 0.2 procentenheter lägre på FPGA, en skillnad i linje med de förväntade effekterna av att använda kortare, fastpunktstal i hårdvara.

Göra hårdvaran snabb utan att bryta matematiken

När korrektheten är säkerställd finjusteras designen för hastighet. De mest krävande delarna av nätverket — konvolutionslagren — mappas till FPGA:ns programmerbara logik, med fastpunktaritmetik för effektivitet, medan lättare uppgifter som slutlig softmax-beräkning körs på kretsens inbyggda processor med vanlig flyttalsaritmetik. Tekniker som loop-pipelining, loop-unrolling och noggrann uppdelning av minne i parallella bankar tillåter olika delar av beräkningen och dataöverföringarna att köras parallellt. En optimerad version av hårdvaran bearbetar ett hjärtslagsfönster på cirka 1,7 millisekunder och passar väl inom FPGA:ns resurs- och effektbegränsningar, samtidigt som den bevarar den lager-vise numeriska beteendet hos den ursprungliga MATLAB-modellen.

Vad detta betyder för framtida smarta enheter

För icke-specialister är huvudbudskapet att det nu är möjligt inte bara att accelerera en sofistikerad MATLAB-baserad hjärtrytmklassificerare på en lågförbrukande krets, utan också att bevisa att kretsens inre funktioner matchar den betrodda programvarumodellen noggrant på varje lager. Istället för att jaga hastighet på bekostnad av tillförlitlighet, bygger detta tillvägagångssätt en tydlig revisionskedja från flyttals-MATLAB-kod till fastpunkt-FPGA-hårdvara. Samma verifieringsrecept — spara golden outputs, jämföra lager-fel mot en strikt tröskel och kontrollera slutlig noggrannhet — kan tillämpas på andra endimensionella neurala nätverk inom områden som bärbar hälsouppföljning, industrisensorer och smarta fordon, och bidra till att säkerställa att när algoritmer lämnar laboratoriet och flyttar in i enheter, förblir deras beslut tillförlitliga.

Citering: Bal, S. Towards the transformation of MATLAB models into FPGA-Based hardware accelerators. Sci Rep 16, 5027 (2026). https://doi.org/10.1038/s41598-026-36033-z

Nyckelord: FPGA-acceleratorer, MATLAB neurala nätverk, EKG arytmi-klassificering, hårdvaruverifiering, fastpunkt djupinlärning