Clear Sky Science · ru

К трансформации моделей MATLAB в аппаратные ускорители на базе FPGA

Преобразование лабораторных алгоритмов в реальные устройства

Многие современные прорывы в медицине и технике возникают как программные решения, написанные исследователями в удобных средах, таких как MATLAB. Но когда те же алгоритмы должны работать в режиме реального времени — например, обнаруживать опасные нарушения ритма сердца по электрокардиограмме (ЭКГ) — им требуются скорость и энергоэффективность специализированного оборудования. В этой статье показано, как надежно перенести сложную нейронную сеть для обнаружения сердечных сокращений из MATLAB на специализированный чип FPGA, не потеряв точности, от которой зависят врачи и инженеры.

Почему переписывать код под чипы так сложно

FPGA (Field-Programmable Gate Arrays) — это перенастраиваемые микросхемы, ценимые за скорость и низкое энергопотребление. Традиционно их программирование требовало языков, ориентированных на аппаратную часть, таких как VHDL или Verilog, которые сильно отличаются от высокоуровневых математических и сигнальных алгоритмов, которые учёные пишут в MATLAB. Появляются инструменты, автоматически преобразующие алгоритмы в описания аппаратуры, но они нередко требуют ручной доработки и сосредоточены прежде всего на производительности: как быстро работает чип, сколько ресурсов он использует. Однако не хватало ясного способа доказать, что аппаратное воплощение делает именно то же самое, что и исходное программное обеспечение, слой за слоем, число за числом.

Пошаговая проверка для каждого слоя сети

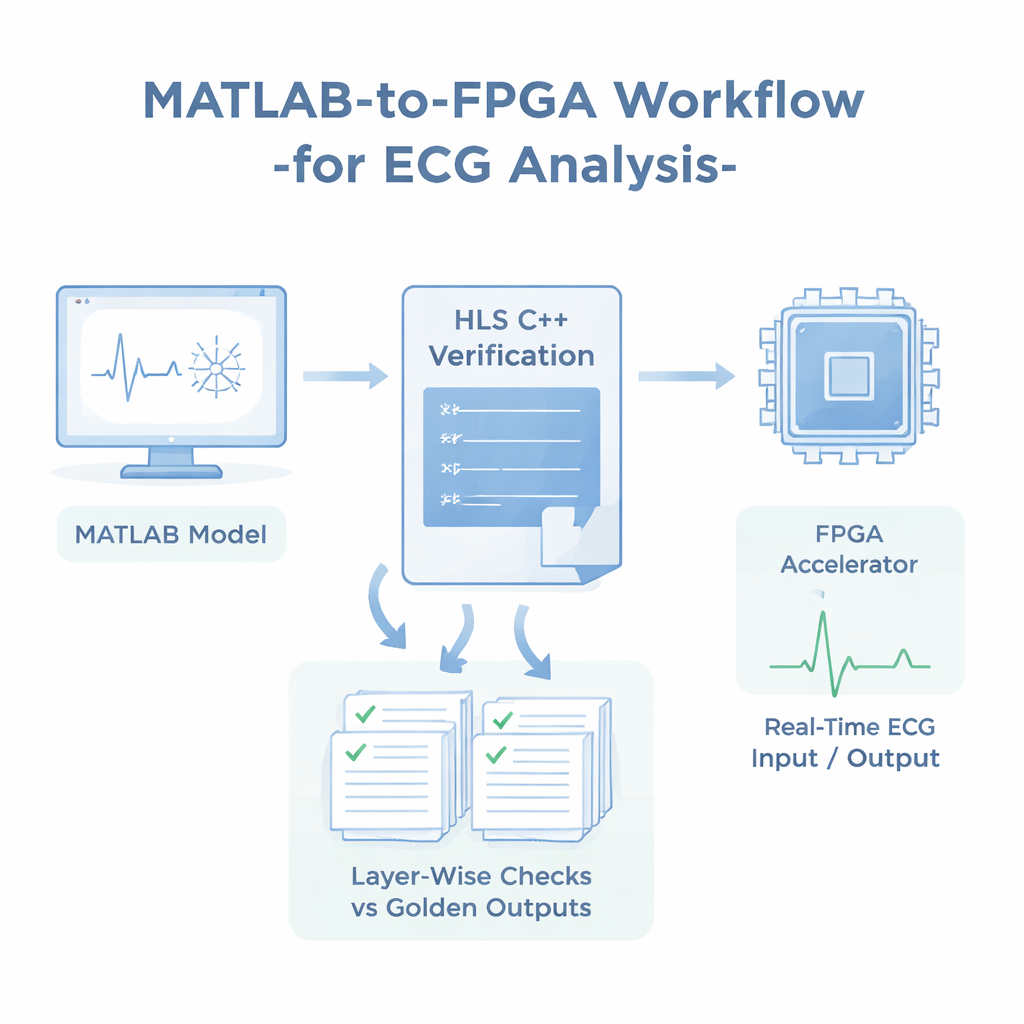

Автор закрывает этот пробел, предлагая рабочий процесс с приоритетом верификации для одномерной свёрточной нейронной сети, классифицирующей сердечные сокращения по известной базе MIT-BIH Arrhythmia Database. Сеть, построенная в MATLAB, анализирует короткие фрагменты ЭКГ и отнесёт их к одному из пяти типов сердечных сокращений, включая нормальный и несколько отклоняющихся ритмов. Три версии сети различной глубины обучаются на одних и тех же данных. После обучения веса, смещения и выходы каждого слоя на тестовых сигналах сохраняются как «золотые» выходы — точная числовая запись поведения модели MATLAB.

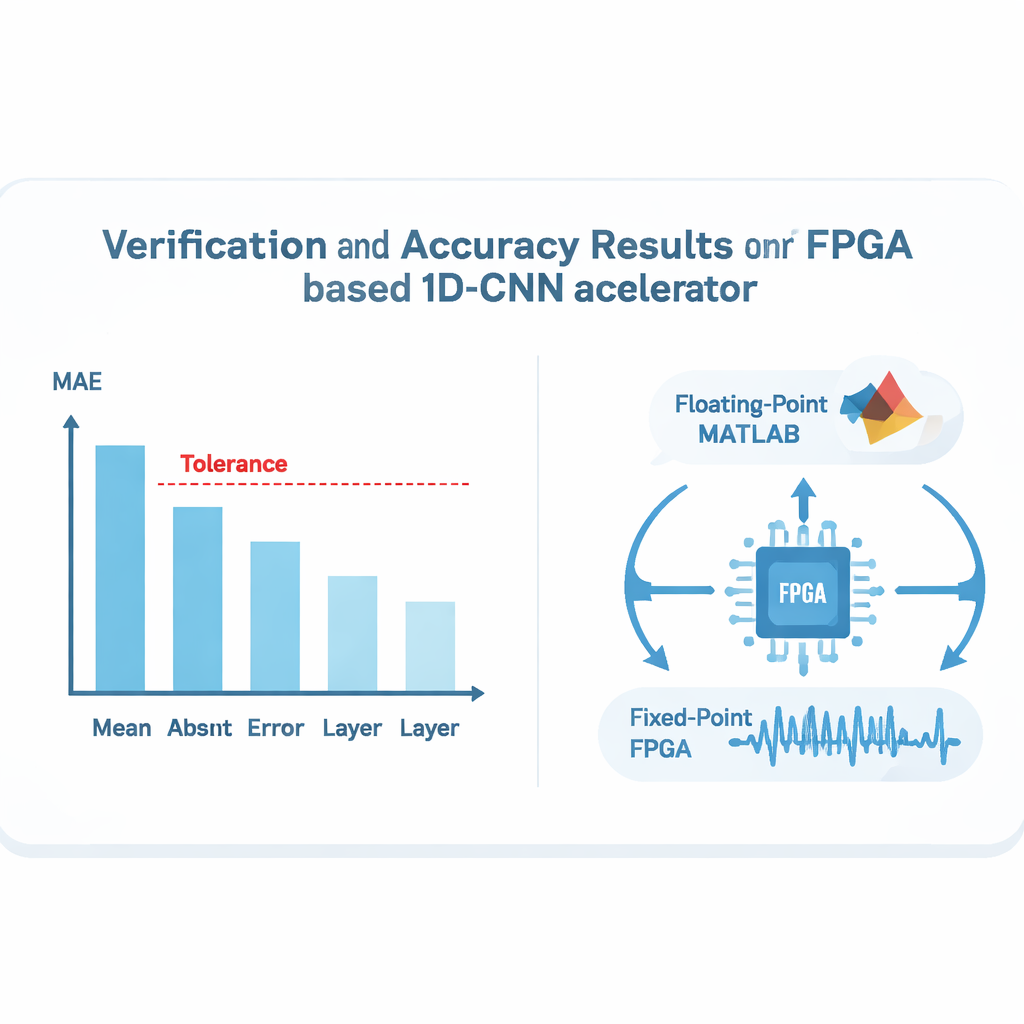

От MATLAB через C++ к FPGA с учётом чисел

Вместо нажатия кнопки автоматического «конвертирования» сеть вручную реализуют на C++, соблюдая ту же организацию данных и математические операции, что и в MATLAB. Этот C++ код затем используется с инструментом высокоуровневой синтезы для генерации аппаратуры, работающей на плате PYNQ-Z1 с FPGA. На каждом этапе — MATLAB, C++ и FPGA — выходы слоёв сравниваются с сохранёнными «золотыми» выходами с помощью простого показателя: средняя абсолютная ошибка, которая измеряет среднюю числовую разницу между двумя наборами результатов. В исследовании установлена строгая допустимая погрешность: все слои должны оставаться ниже ошибки 1.5×10⁻³. На тысячах образцов ЭКГ каждый проверенный слой удовлетворяет этому требованию, а итоговая точность классификации практически не меняется: около 98.3–98.4% в MATLAB и C++, и лишь примерно на 0.2 процентных пункта ниже на FPGA — разница, согласующаяся с ожидаемыми эффектами применения укороченных фиксированных чисел в аппаратуре.

Ускоряем аппарат без нарушения математики

Когда корректность подтверждена, дизайн настраивают на скорость. Самые требовательные части сети — свёрточные слои — выносятся в программируемую логику FPGA и используют фиксированную арифметику для эффективности, тогда как лёгкие операции, такие как финальный расчёт softmax, выполняются на встроенном процессоре с обычной плавающей запятой. Приёмы типа конвейеризации циклов, развёртывания циклов и аккуратного разделения памяти на параллельные банки позволяют выполнять разные части вычислений и передачи данных одновременно. Оптимизированная версия аппаратуры обрабатывает окно сердечного сокращения примерно за 1.7 миллисекунды и удобно размещается в ресурсных и энергетических пределах FPGA, при этом сохраняя покомпонентное числовое поведение исходной модели MATLAB.

Что это значит для будущих умных устройств

Для неспециалистов ключевой вывод в том, что теперь возможно не только ускорить сложный классификатор ритма сердца, разработанный в MATLAB, на энергоэффективном чипе, но и доказать, что внутренние вычисления этого чипа тесно соответствуют доверенной программной модели на каждом слое. Вместо того чтобы гнаться за скоростью в ущерб надёжности, этот подход создаёт понятную проверяемую цепочку от плавающей точки в MATLAB до фиксированной точки в FPGA. Та же методика верификации — сохранение «золотых» выходов, сравнение покомпонентных ошибок с жёстким порогом и проверка итоговой точности — может применяться к другим одномерным нейросетям в областях вроде носимых медицинских приборов, промышленных датчиков и умных автомобилей, помогая обеспечить, что при переносе алгоритмов из лаборатории в устройства их решения остаются надёжными.

Цитирование: Bal, S. Towards the transformation of MATLAB models into FPGA-Based hardware accelerators. Sci Rep 16, 5027 (2026). https://doi.org/10.1038/s41598-026-36033-z

Ключевые слова: ускорители FPGA, нейросети MATLAB, классификация аритмий по ЭКГ, аппаратная верификация, фиксированная точка в глубоком обучении