Clear Sky Science · pt

Corrigindo erros aritméticos de multiplicação-acumulação em processamento na memória com LDPC

Por que consertar erros matemáticos na memória importa

Chips de inteligência artificial modernos extraem mais velocidade e eficiência do hardware realizando cálculos diretamente na memória, em vez de transferir dados continuamente para processadores separados. Essa abordagem de “processamento-na-memória” economiza energia, mas introduz um problema sério: pequenas imperfeições elétricas podem inverter bits armazenados ou distorcer sinais analógicos, degradando silenciosamente a precisão de tarefas como reconhecimento de imagens. O artigo descreve uma nova forma de detectar e corrigir automaticamente esses erros em tempo real, ajudando o hardware de IA do futuro a permanecer rápido e confiável.

Computação onde os dados residem

Computadores convencionais são retardados pela necessidade de mover dados entre memória e processador. Projetos de processamento-na-memória evitam esse gargalo executando operações de multiplicação e acumulação — a espinha dorsal das redes neurais — dentro de matrizes densas de células de memória. Dispositivos emergentes, como memória resistiva e outros elementos memristivos, são especialmente atraentes porque conseguem armazenar muitos valores e realizar aritmética em estilo analógico com grande eficiência. Contudo, a mesma natureza analógica e a variabilidade dos dispositivos que os tornam potentes também os tornam ruidosos: flutuações térmicas, descompassos entre dispositivos e quedas de tensão podem todos deslocar valores armazenados ou resultados computados para longe do que deveriam ser.

Quando pequenos defeitos se acumulam

Nessas matrizes in‑memory, muitas linhas de células são ativadas simultaneamente e suas contribuições são somadas ao longo de fios compartilhados. À medida que mais linhas participam, suas imperfeições individuais se somam, criando padrões de erro que são frequentes e complexos. Em vez de um único bit errado, os projetistas frequentemente observam múltiplos erros agrupados na mesma coluna de uma matriz ou espalhados por várias colunas de um modo que derrota truques tradicionais de correção de erros. Códigos padrão geralmente assumem padrões de erro simples e comprimentos de palavra curtos; eles podem deixar passar falhas de múltiplos bits ou não ter entradas em suas tabelas de consulta para combinações raras, mas danosas. Como resultado, a precisão de modelos profundas pode cair abruptamente assim que o hardware subjacente se torna moderadamente pouco confiável.

Um novo tipo de rede de segurança digital

Os autores introduzem um código LDPC de baixa densidade não binário (NB-LDPC) projetado especificamente para hardware de processamento-na-memória. Em vez de trabalhar apenas com zeros e uns, o esquema opera em pequenos grupos de bits tratados como símbolos em uma estrutura matemática chamada campo finito construído a partir de um número primo (aqui, três). Isso permite que o mesmo código proteja tanto o armazenamento binário comum quanto codificações multinível ou diferenciais usadas em aceleradores analógicos. O sistema adiciona um número modesto de símbolos extras — símbolos de verificação — a cada bloco de dados. Durante leituras normais de memória e durante operações de multiplicação-acumulação na memória, o hardware computa resultados para os dados e os símbolos de verificação juntos, de modo que a detecção de erros fica naturalmente tecida na computação.

Como o motor de correção funciona dentro do chip

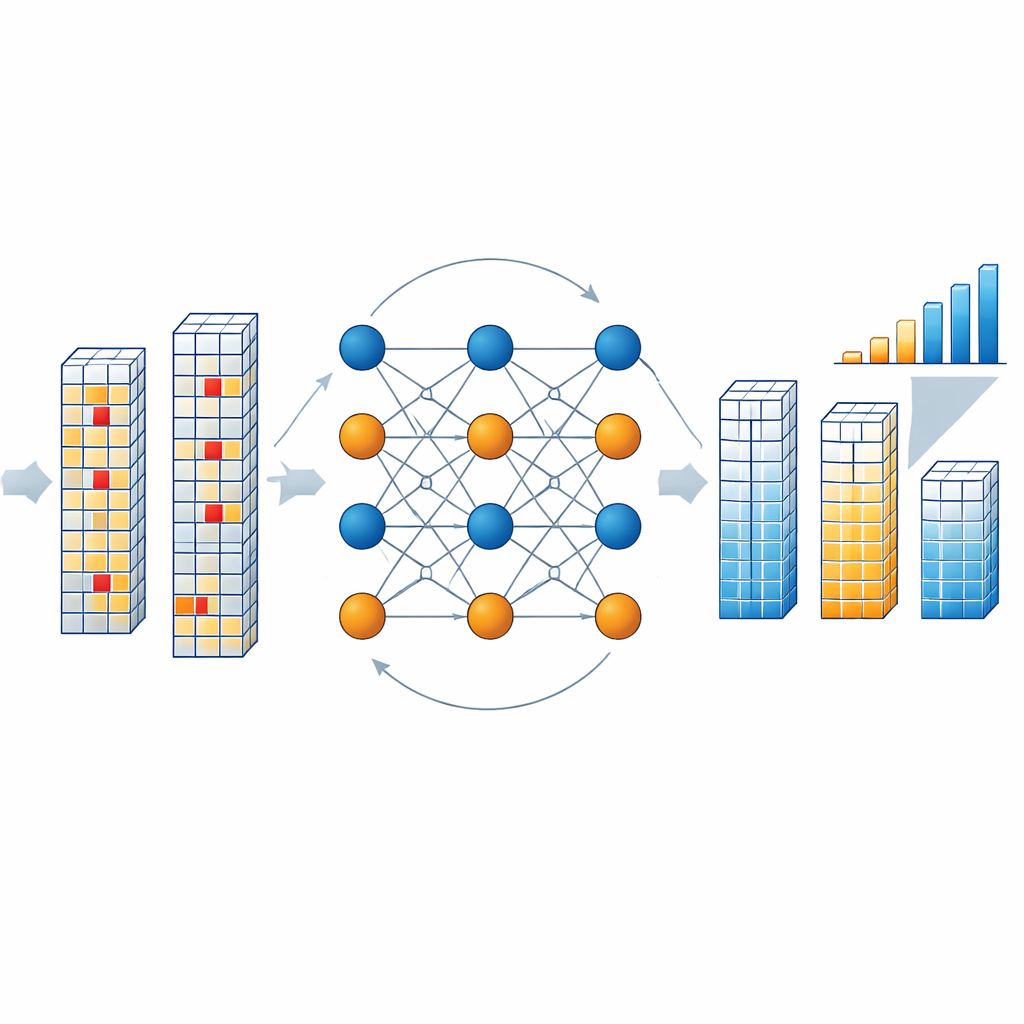

Quando o chip lê um bloco de resultados, um decodificador dedicado examina se os símbolos de dados combinados e de verificação obedecem às relações de paridade definidas pelo código. Se obedecem, o bloco é considerado limpo. Caso contrário, o decodificador inicia um processo iterativo no qual “nós variáveis” abstratos representando cada símbolo e “nós de verificação” representando condições de paridade trocam mensagens de probabilidade. Essas mensagens estimam quão provável é que cada símbolo assuma cada um dos valores permitidos, com base nas saídas observadas e na taxa de erro por inversão de bit esperada da memória. Os autores simplificam esse raciocínio matemático pesado usando aproximações de distância de Manhattan, o que reduz muito o custo de hardware mantendo alto desempenho. Após algumas rodadas — tipicamente três — o decodificador converge para a versão corrigida mais plausível do vetor de resultados, sem nunca precisar reler a memória ou interromper o fluxo de computação.

Prova em silício e impacto na precisão de IA

Para testar a ideia na prática, a equipe construiu um chip protótipo em um processo de 40 nanômetros que combina uma matriz de memória resistiva, conversores analógico‑para‑digital leves e o novo decodificador NB-LDPC. Com uma configuração que protege 256 símbolos de informação usando 32 símbolos de verificação, o decodificador atinge uma alta taxa de código (cerca de 0,8), uma melhor eficiência energética medida de aproximadamente 88 terabits de dados corrigidos por segundo por watt e apenas uma sobrecarga de área modesta que pode ser reduzida compartilhando um decodificador entre vários blocos de memória. Simulações em vários tamanhos de código mostram que, ao proteger 1024 símbolos de dados com 128 símbolos de verificação, o esquema pode melhorar a taxa de erro de bit em quase 60 vezes. Aplicado a um modelo de classificação de imagens ResNet‑34 rodando em hardware de processamento‑na‑memória, a correção recupera mais de 20 pontos percentuais da acurácia perdida sob condições de erro desafiadoras.

O que isso significa para chips de IA futuros

Em termos simples, o trabalho fornece ao hardware de processamento‑na‑memória um “corretor ortográfico” robusto para sua matemática, que entende conjuntos de símbolos mais ricos e padrões de erro complexos sem desacelerar o fluxo de dados. Ao unificar a proteção tanto para dados armazenados quanto para cálculos em tempo real, e ao demonstrar uma implementação eficiente em silício, o estudo mostra que aceleradores in‑memory de alta densidade e baixo consumo não precisam sacrificar a confiabilidade. Esse tipo de correção de erro sob medida pode se tornar um ingrediente chave para tornar aceleradores neuromórficos e de IA do futuro ao mesmo tempo econômicos em energia e suficientemente confiáveis para aplicações no mundo real, desde dispositivos móveis até data centers em grande escala.

Citação: Shi, D., Fu, Y., Zhu, Y. et al. Correcting processing-in-memory multiply-accumulate arithmetic errors with LDPC. npj Unconv. Comput. 3, 14 (2026). https://doi.org/10.1038/s44335-026-00061-9

Palavras-chave: processamento-na-memória, correção de erros, códigos LDPC, memória resistiva, hardware para redes neurais