Clear Sky Science · pt

Célula de ganho com semicondutor óxido incorporada à memória: materiais e estratégias de integração para a próxima geração de memória on-chip

Por que uma memória mais rápida e inteligente importa

Nossos telefones, laptops e centros de dados ficam cada vez mais potentes, mas um limite oculto de velocidade persiste: mover dados entre o processador e a memória. Este artigo explora um novo tipo de memória on-chip que pode aliviar essa “barreira da memória”, tornando computadores futuros mais rápidos e energeticamente eficientes para tarefas como inteligência artificial, computação em nuvem e apps do dia a dia. Ao repensar como as células de memória são construídas e quais materiais elas usam, os pesquisadores buscam concentrar muito mais dados perto do processador enquanto reduzem consumo de energia e calor.

O gargalo dentro dos computadores modernos

Por décadas, o desempenho do processador melhorou muito mais rápido do que a memória principal que o alimenta com dados. Essa desconexão, conhecida como barreira da memória, faz com que chips rápidos muitas vezes fiquem ociosos aguardando informação. Projetistas tentaram amenizar esse gargalo com múltiplas camadas de cache localizadas no próprio processador. Os caches atuais dependem de um tipo de memória chamado SRAM, que é muito rápida, mas volumosa e com alto consumo de energia porque cada bit precisa de seis transistores. Para obter mais capacidade, empresas empilham chips SRAM em três dimensões ou adicionam DRAM incorporada no chip, mas a DRAM convencional ainda depende de capacitores minúsculos difíceis de fabricar em escalas extremas e difíceis de integrar com circuitos lógicos padrão.

Um tipo diferente de célula de memória

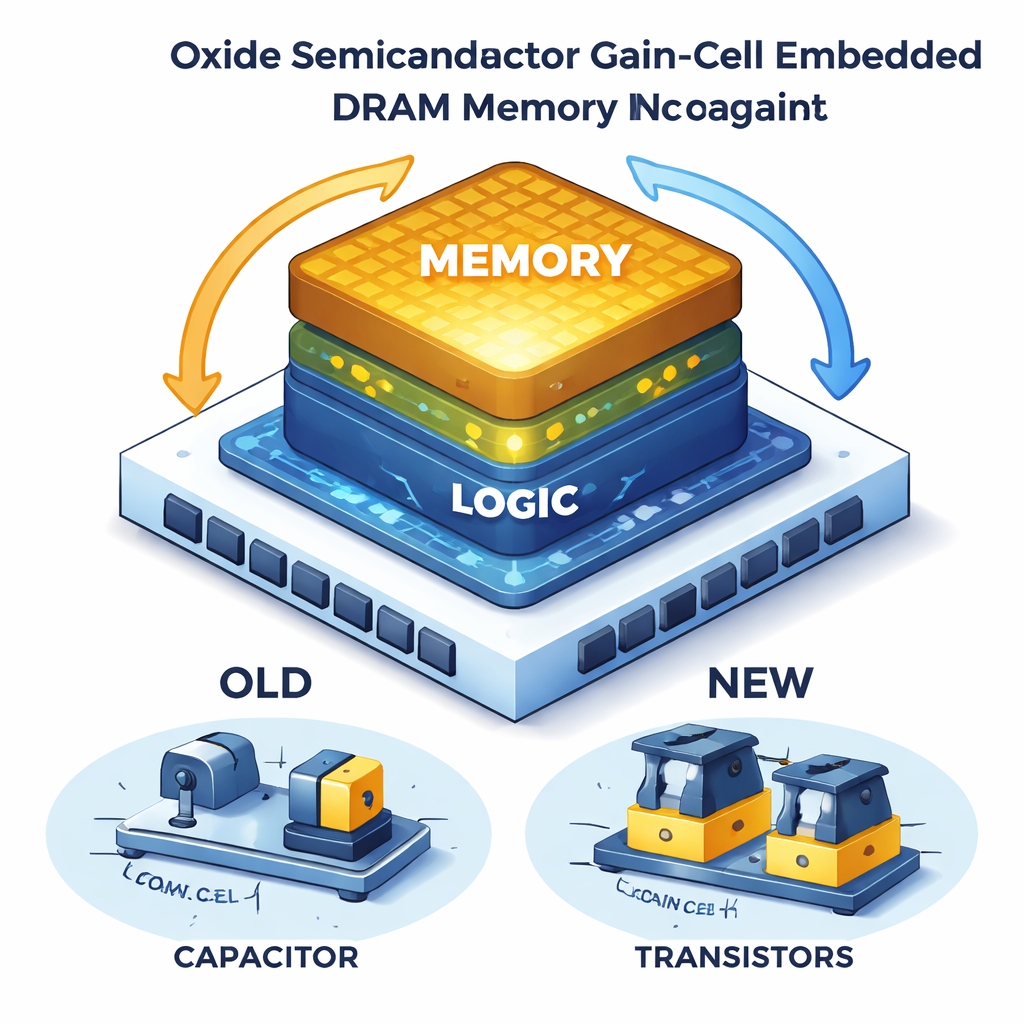

O artigo foca em uma alternativa chamada DRAM incorporada com célula de ganho, ou GC-eDRAM. Em vez de usar um capacitor separado para armazenar carga, uma célula de ganho usa apenas transistores para manter os dados, simplificando a estrutura e tornando-a mais compatível com a fabricação de chips padrão. Esse projeto se ajusta naturalmente à empilhamento tridimensional acima de circuitos lógicos, prometendo arranjos de “memória sobre lógica” de alta densidade. Outra vantagem é seu comportamento de “leitura não destrutiva”: ler um valor armazenado não o drena imediatamente, o que pode reduzir a frequência de operações de refresh. Entretanto, em versões tradicionais de silício, a carga armazenada vaza em menos de um milissegundo, então operações frequentes de refresh ainda desperdiçam energia e limitam a utilidade.

Semicondutores de óxido: chaves mais silenciosas e frias

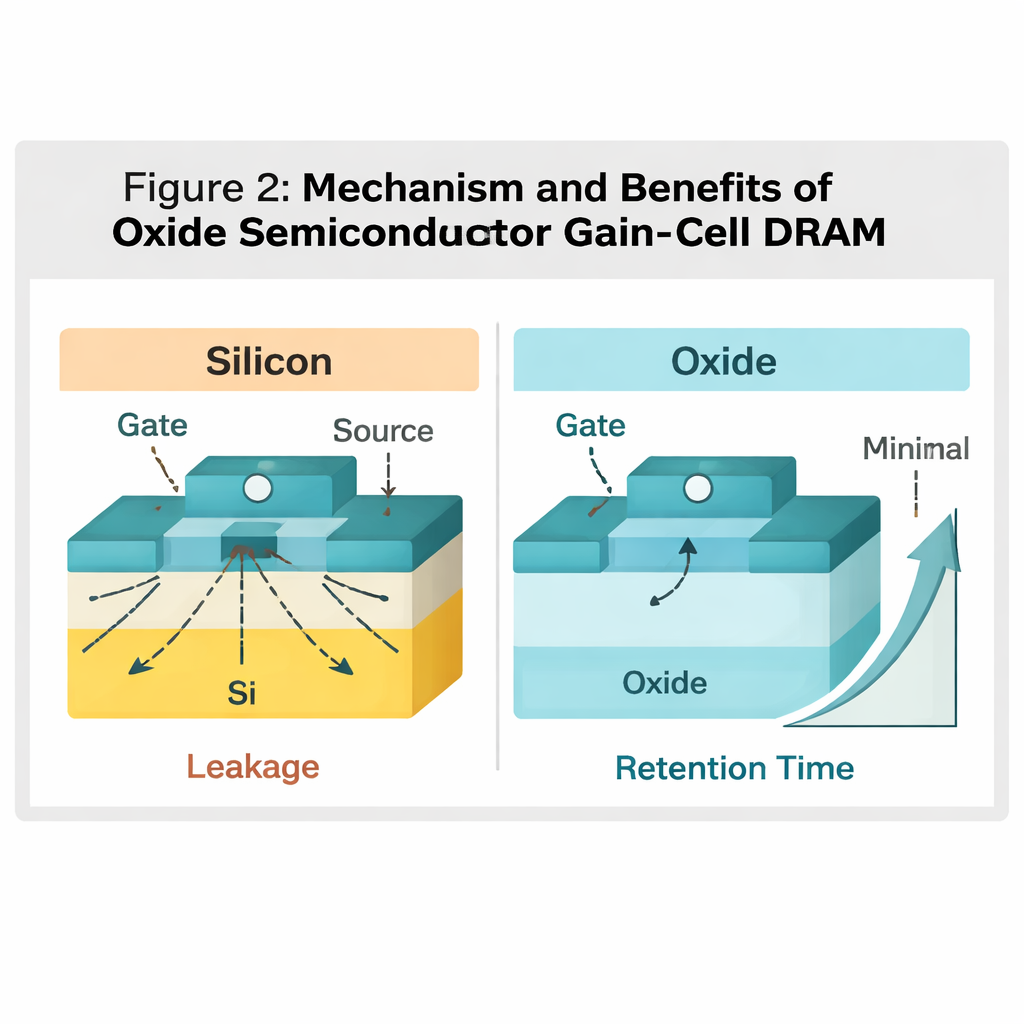

Para superar o vazamento em células de ganho, os autores destacam semicondutores de óxido — materiais como óxido de índio-gálio-zinco (IGZO) e compostos relacionados — como novos materiais de canal para os transistores. Esses óxidos têm uma ampla lacuna de energia, o que suprime fortemente a corrente indesejada quando um transistor deveria estar desligado. Experimentos mediram correntes de off tão minúsculas que se aproximam dos limites dos equipamentos de teste, e protótipos de células de ganho agora mantêm dados por muitos segundos, horas ou até mais de um dia, em comparação com milésimos de segundo em projetos de silício. Fundamentalmente, esses óxidos podem ser depositados a temperaturas relativamente baixas compatíveis com o “back-end” da fabricação de chips, permitindo que engenheiros construam camadas de memória densas diretamente sobre a lógica de silício existente sem danificá-la.

Construindo para cima: pilhas 3D e transistores minúsculos

À medida que os chips continuam a encolher, simplesmente reduzir o tamanho dos transistores traz novos problemas, como controle fraco do canal e aumento do vazamento. O artigo revisa formatos avançados de transistor que envolvem a porta ao redor do canal (projetos gate-all-around e channel-all-around) para manter controle rigoroso mesmo em tamanhos nanométricos. Usando semicondutores de óxido nessas estruturas multi-gate, os pesquisadores demonstraram canais muito curtos, vazamento extremamente baixo e forte retenção de dados enquanto empilham múltiplas camadas de memória verticalmente. Alguns designs experimentais já alcançam ou superam a eficiência de área das melhores células DRAM atuais, sugerindo que chips futuros poderiam abrigar capacidade de memória enorme em uma pegada muito pequena logo acima dos núcleos do processador.

De materiais de laboratório a produtos confiáveis

Transformar esses dispositivos promissores em memória prática exige engenharia cuidadosa de materiais. O artigo descreve como ajustar a mistura de metais no óxido, controlar o teor de oxigênio e cristalizar os filmes pode equilibrar alta velocidade com estabilidade a longo prazo. Cobre também maneiras de gerenciar defeitos, contaminação por hidrogênio e as interfaces delicadas entre óxidos e camadas isolantes para que os dispositivos permaneçam estáveis sob calor e operação prolongada. Por fim, discute a engenharia das conexões metálicas para que a resistência de contato não anule os benefícios dos novos materiais. Juntas, essas estratégias visam entregar uma memória densa e confiável o suficiente para fabricação em larga escala.

O que isso significa para a computação do dia a dia

Os autores concluem que memórias com célula de ganho em semicondutores de óxido podem remodelar a forma como chips futuros são construídos. Ao combinar células de memória minúsculas e de baixo vazamento com empilhamento 3D sobre circuitos lógicos, projetistas poderiam colocar muito mais memória rápida ao lado do processador mantendo o consumo de energia sob controle. Isso aliviaria a barreira da memória, ajudando desde aceleradores de IA até servidores em nuvem e dispositivos pessoais a rodarem mais rápido e com maior eficiência. Embora desafios permaneçam em confiabilidade, uniformidade de fabricação e integração em chip completo, o trabalho aqui revisado delineia um caminho claro em direção a sistemas de computação mais compactos, potentes e conscientes em termos energéticos.

Citação: Chung, S.W., Yoon, S.H. & Jeong, J.K. Oxide semiconductor gain cell-embedded memory: materials and integration strategies for next generation on-chip memory. Commun Eng 5, 39 (2026). https://doi.org/10.1038/s44172-026-00616-5

Palavras-chave: memória on-chip, semicondutores de óxido, escalação de DRAM, circuitos integrados 3D, hardware para IA