Clear Sky Science · pt

Mapeando dinâmicas variadas de histerese em FETs de MoS2 escalados usando o método universal derivado de modelagem TCAD

Por que chaves minúsculas precisam de comportamento confiável

A eletrônica moderna avança rumo a transistores cada vez menores, e materiais bidimensionais (2D) como o dissulfeto de molibdênio (MoS2) são candidatos promissores para os chips do futuro. Mas à medida que esses interruptores encolhem, seu comportamento pode se tornar inconsistente: o mesmo dispositivo pode responder de forma diferente dependendo de como foi usado momentos antes. Esse efeito semelhante a memória, chamado histerese, costuma ser tratado como um incômodo menor. Neste trabalho, os autores mostram que a histerese na verdade esconde uma riqueza de informações sobre falhas ocultas dentro de transistores avançados — e introduzem uma maneira universal de ler essas informações.

Como os transistores de próxima geração são construídos

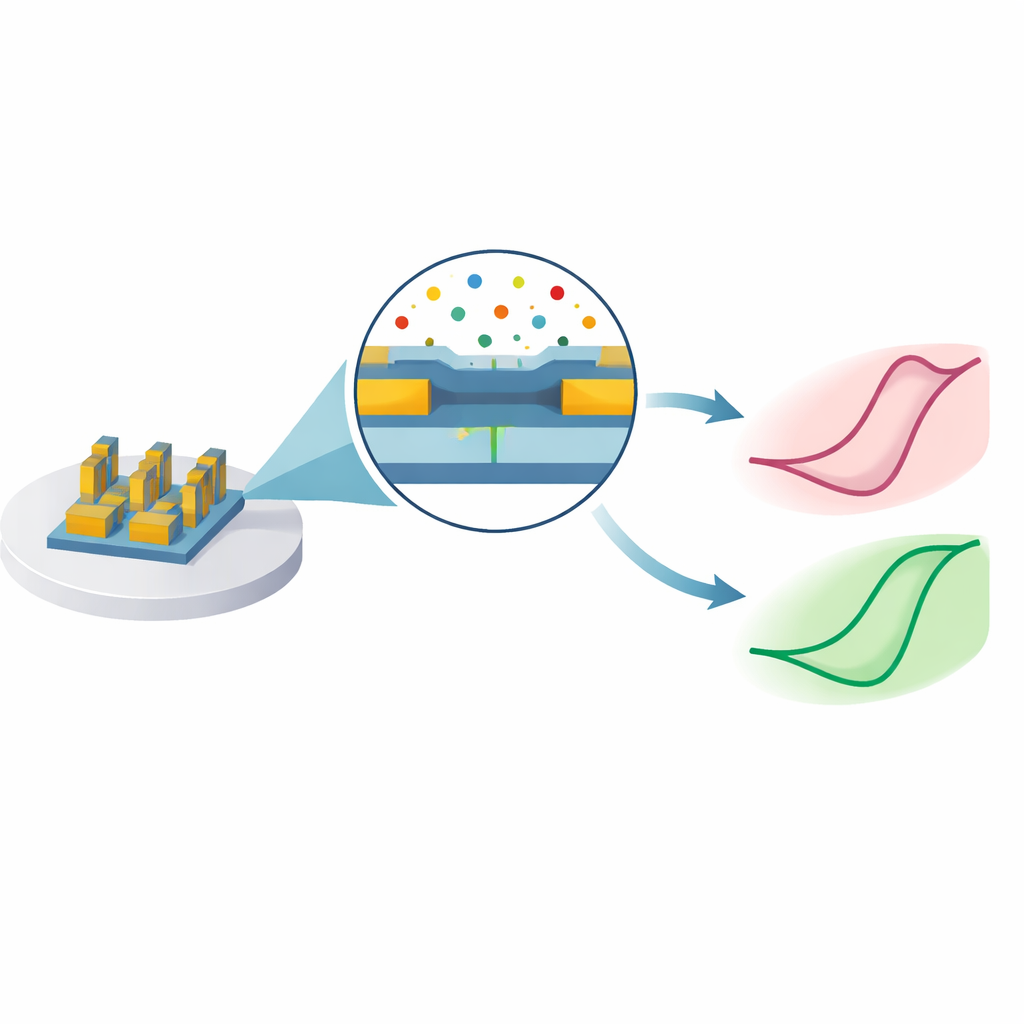

Transistores de efeito de campo 2D futuros usam uma camada ultrafina de MoS2 como o canal por onde flui a corrente, coberta por um óxido isolante muito fino, como o óxido de háfnio (HfO2), e um eletrodo de gate metálico por cima. Para continuar reduzindo o tamanho dos dispositivos, esse óxido deve ter espessura elétrica da ordem de um nanômetro, o que significa que qualquer defeito individual dentro dele pode perturbar fortemente o canal. Esses defeitos agem como armadilhas diminutas que podem prender ou liberar carga elétrica temporariamente. Como os defeitos podem residir em diferentes profundidades dentro do óxido e interagir tanto com o canal quanto com o gate, seu comportamento coletivo pode estabilizar ou desestabilizar o transistor de maneiras sutis. Entender esse panorama de defeitos é crucial se os transistores 2D quiserem competir com a tecnologia de silício atual.

Por que o transistor lembra seu passado

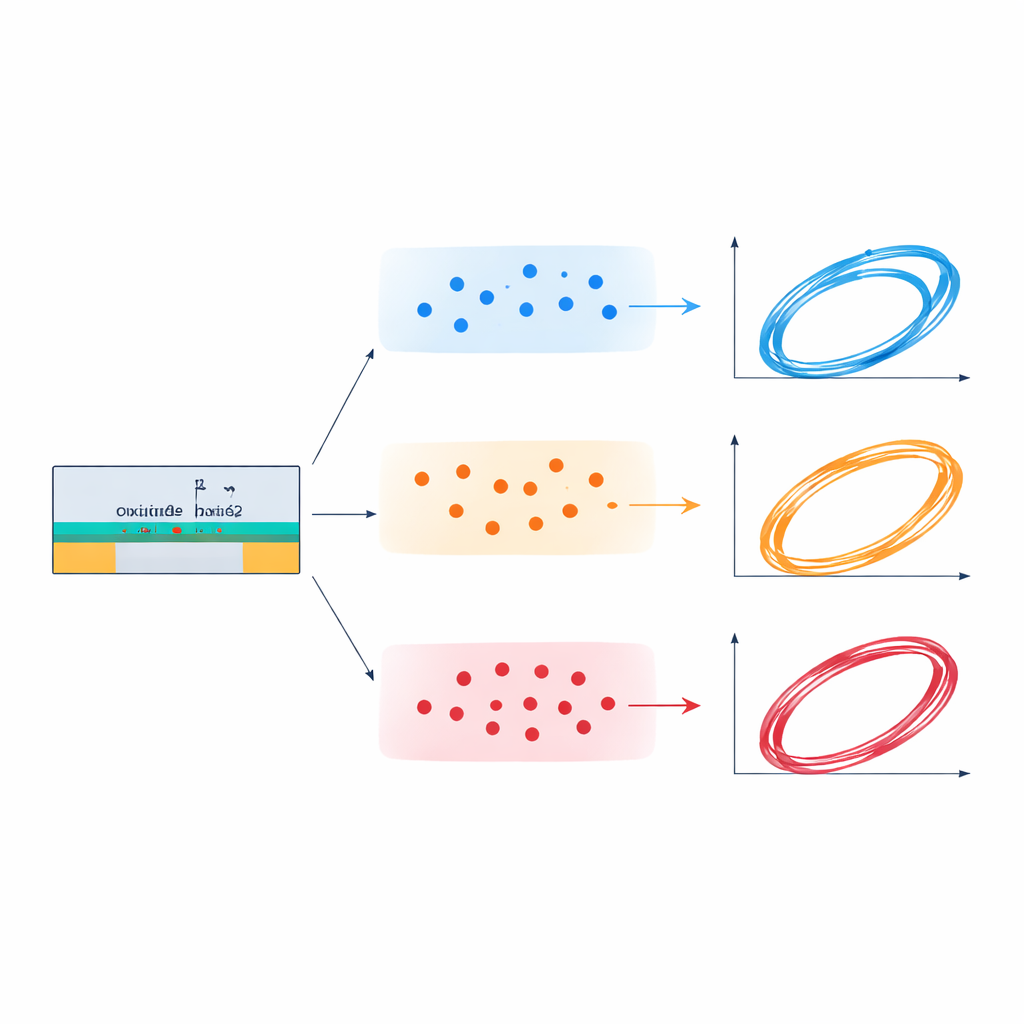

Quando engenheiros varrem a tensão do gate para cima e para baixo e registram a corrente, frequentemente observam que as curvas de subida e descida não coincidem. Esse laço é a histerese. Tradicionalmente, pesquisadores medem a distância entre as duas curvas em um único ponto de operação e chamam isso de largura da histerese, muitas vezes concluindo que é “pequena” ou “neglegenciável”. Os autores argumentam que essa prática é enganosa, especialmente para dispositivos escalados nos quais diferentes grupos de defeitos podem contribuir de maneiras opostas. Dependendo da velocidade de medição e da corrente de operação, o mesmo transistor pode mostrar laços convencionais no sentido horário, laços invertidos no sentido anti-horário, alternância entre os dois, ou mesmo quase nenhuma histerese quando efeitos opostos se cancelam.

Um mapa universal escondido nas curvas

Para desembaraçar essa complexidade, a equipe usa simulações detalhadas por computador (TCAD) de transistores de MoS2 em escala nanométrica com populações de defeitos cuidadosamente controladas em diferentes profundidades do óxido. Em seguida, propõem um método universal de mapeamento de histerese. Em vez de extrair um único número, eles escaneiam a largura da histerese ao longo de uma ampla faixa de correntes — desde um pouco acima do estado desligado até próximo do estado ligado — e para tempos de varredura que abrangem muitas ordens de grandeza. Isso produz milhares de curvas mostrando como a histerese muda com a velocidade de medição em cada corrente. A partir dessas curvas, definem funções universais de histerese superior e inferior que delimitam todos os comportamentos possíveis. Esses invólucros revelam de forma clara quais tipos de defeitos estão ativos, se eles interagem principalmente com o canal ou com o gate superior, e se favorecem laços no sentido horário ou anti-horário.

Ligando laços rápidos ao desvio de longo prazo

Os mesmos defeitos que causam histerese também impulsionam desvios lentos no comportamento do transistor sob estresse prolongado, um problema conhecido como instabilidade térmica por polarização (bias temperature instability, BTI). Ao simular experimentos padrão de estresse e recuperação, os autores conectam características em seus mapas de histerese a assinaturas atípicas de BTI, como um deslocamento negativo aparente que só depois relaxa em direção a um deslocamento positivo. Eles mostram que armadilhas próximas ao canal tendem a provocar deslocamentos lentos e em sua maior parte permanentes, enquanto armadilhas mais próximas ao gate causam mudanças mais rápidas, porém em grande parte reversíveis. O método pode ser aplicado não só a dispositivos de MoS2 simulados, mas também a dados medidos de transistores reais de MoS2 e WSe2 fabricados em salas limpas de pesquisa e linhas piloto de fabricação, incluindo casos nos quais íons em deriva dentro do óxido também participam do jogo de captura de carga.

De dados complexos a orientações práticas

Ao transformar laços de histerese confusos em mapas padronizados, este trabalho oferece um diagnóstico poderoso para tecnologias emergentes de transistores. O método funciona diretamente em conjuntos de dados experimentais e não requer acesso a ferramentas avançadas de simulação, tornando-o amplamente utilizável em diversos laboratórios. Para engenheiros, a mensagem-chave é que a histerese não é apenas um defeito a ser minimizado, mas uma impressão digital de problemas de confiabilidade subjacentes. Decodificar essa impressão digital com o método de mapeamento proposto pode orientar escolhas melhores de materiais, interfaces mais limpas e processos mais inteligentes, ajudando os transistores 2D a evoluir de protótipos promissores para blocos de construção realmente confiáveis da eletrônica do futuro.

Citação: Lv, Y.Z., Wu, Y.H., Cai, H.H. et al. Mapping diverse hysteresis dynamics in scaled MoS2 FETs using the universal method derived from TCAD modeling. npj 2D Mater Appl 10, 35 (2026). https://doi.org/10.1038/s41699-026-00671-8

Palavras-chave: transistores 2D, histerese, defeitos em óxido, confiabilidade de dispositivo, FETs de MoS2