Clear Sky Science · pt

Rumo à transformação de modelos MATLAB em aceleradores de hardware baseados em FPGA

Transformando algoritmos de laboratório em dispositivos do mundo real

Muitas das descobertas modernas na medicina e na engenharia começam como software escrito por pesquisadores, frequentemente em ferramentas acessíveis como o MATLAB. Mas quando esses mesmos algoritmos precisam operar em tempo real — por exemplo, detectar ritmos cardíacos perigosos a partir de um eletrocardiograma (ECG) — eles exigem a velocidade e a eficiência de hardware dedicado. Este artigo mostra como migrar de forma confiável uma rede neural complexa que detecta batimentos cardíacos do MATLAB para um chip especializado chamado FPGA, sem perder a precisão da qual médicos e engenheiros dependem.

Por que reescrever código para chips é tão difícil

FPGAs (Field-Programmable Gate Arrays) são chips reconfiguráveis valorizados por sua velocidade e baixo consumo de energia. Tradicionalmente, programá-los exigia linguagens voltadas para hardware, como VHDL ou Verilog, muito distantes do código matemático e de processamento de sinais de alto nível que cientistas escrevem no MATLAB. Ferramentas mais recentes podem converter algoritmos automaticamente para descrições de hardware, mas frequentemente demandam ajustes manuais e se concentram principalmente no desempenho: quão rápido o chip roda, quantos recursos consome. O que faltava era um método claro para provar que o hardware faz exatamente o que o software original fazia, camada por camada, número por número.

Uma verificação passo a passo para cada camada da rede

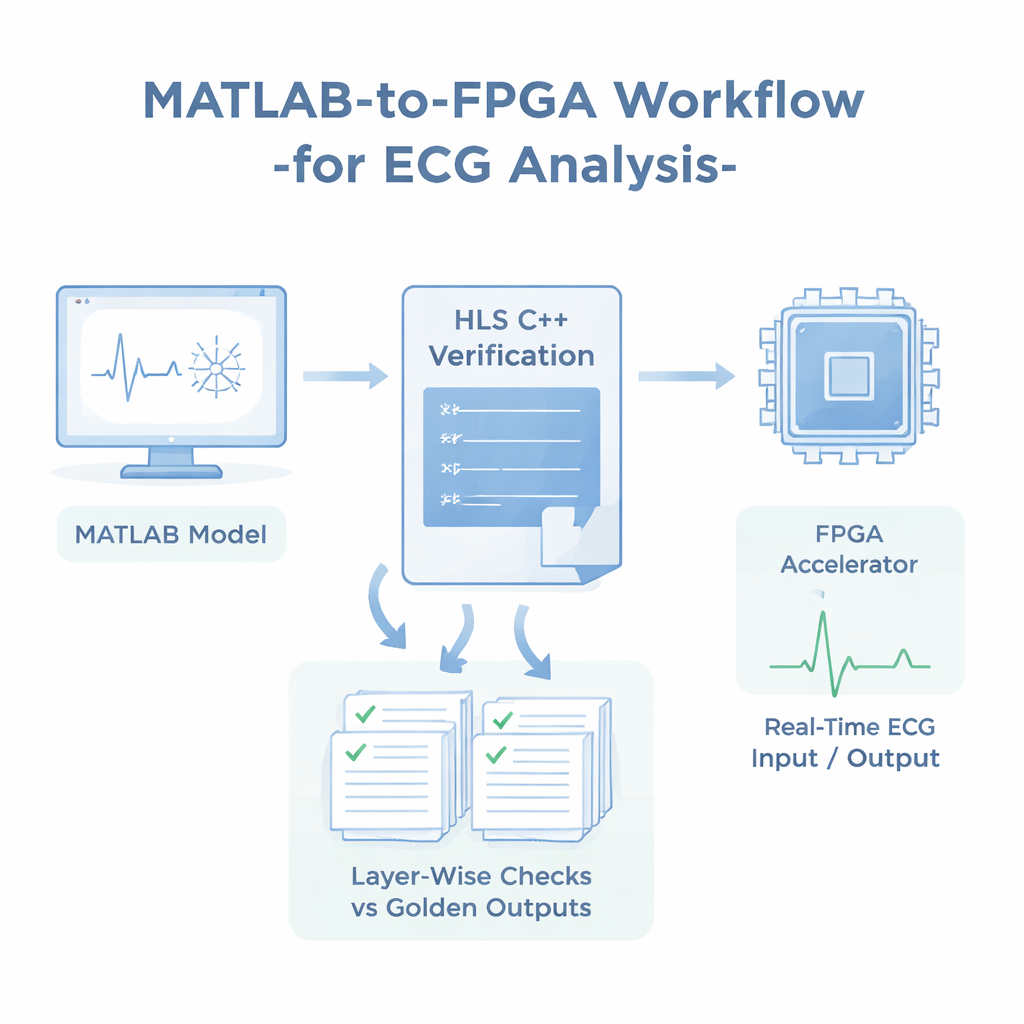

O autor aborda essa lacuna propondo um fluxo de trabalho focado em verificação para uma rede neural convolucional unidimensional que classifica batimentos cardíacos usando o conhecido Banco de Dados de Arritmias MIT-BIH. A rede, construída no MATLAB, examina pequenos trechos de dados de ECG e os classifica em cinco tipos de batimento, incluindo normal e vários ritmos anormais. Três versões da rede, com profundidades diferentes, são treinadas nos mesmos dados. Após o treinamento, os pesos, os vieses e as saídas de cada camada para sinais de teste são salvos como "saídas douradas" — um registro numérico preciso de como o modelo MATLAB se comporta.

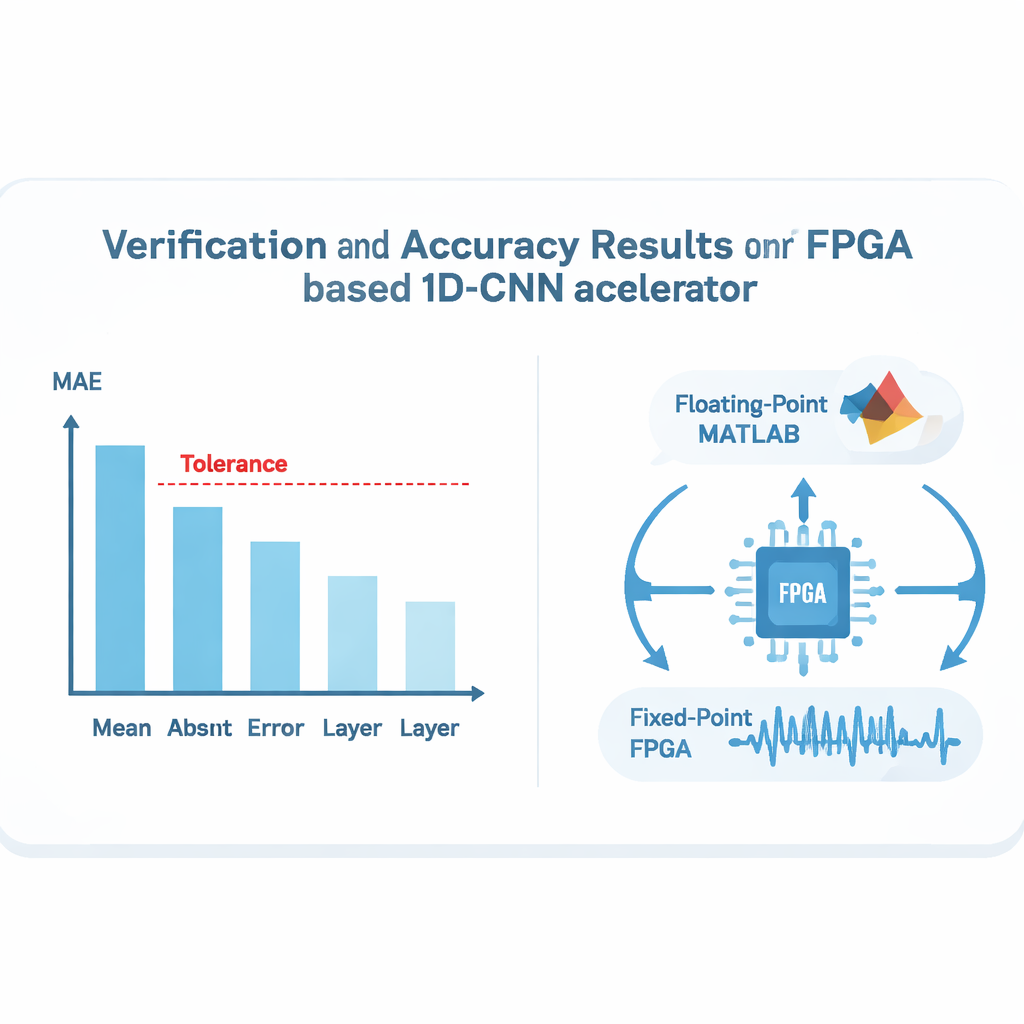

Do MATLAB ao C++ ao FPGA, com os números rastreados

Em vez de acionar um botão automático de "converter", a rede é reimplementada manualmente em C++, seguindo o mesmo layout de dados e as mesmas operações matemáticas do MATLAB. Esse código C++ é então usado com uma ferramenta de síntese em alto nível para gerar hardware que roda em uma placa FPGA PYNQ-Z1. Em cada etapa — MATLAB, C++ e FPGA — as saídas de camada são comparadas com as saídas douradas armazenadas usando uma métrica simples: erro absoluto médio, que mede a diferença numérica média entre dois conjuntos de resultados. O estudo define uma tolerância rígida: todas as camadas devem permanecer abaixo de um erro de 1,5×10⁻³. Ao longo de milhares de amostras de ECG, todas as camadas testadas atingem esse alvo, e a acurácia final de classificação permanece quase inalterada: cerca de 98,3–98,4% no MATLAB e no C++, e apenas cerca de 0,2 ponto percentual a menos no FPGA, uma diferença consistente com os efeitos esperados do uso de números fixos com representação mais curta no hardware.

Tornando o hardware rápido sem quebrar a matemática

Com a correção assegurada, o projeto é ajustado para velocidade. As partes mais exigentes da rede — as camadas convolucionais — são mapeadas na lógica programável do FPGA, usando aritmética em ponto fixo para eficiência, enquanto tarefas mais leves, como o cálculo final do softmax, rodam no processador embutido do chip com números em ponto flutuante tradicionais. Técnicas como pipeline de laços, desenrolamento de laços e divisão cuidadosa da memória em bancos paralelos permitem que diferentes partes da computação e das transferências de dados ocorram simultaneamente. Uma versão otimizada do hardware processa uma janela de batimento em cerca de 1,7 milissegundos e se encaixa confortavelmente nos limites de recursos e consumo do FPGA, preservando ao mesmo tempo o comportamento numérico por camada do modelo MATLAB original.

O que isso significa para dispositivos inteligentes futuros

Para não especialistas, a mensagem principal é que agora é possível não só acelerar um sofisticado classificador de ritmos cardíacos baseado em MATLAB em um chip de baixo consumo, mas também provar que o funcionamento interno do chip corresponde de perto ao modelo de software confiável em cada camada. Em vez de perseguir velocidade em detrimento da confiabilidade, essa abordagem constrói uma trilha de auditoria clara do código MATLAB em ponto flutuante até o hardware FPGA em ponto fixo. A mesma receita de verificação — salvar saídas douradas, comparar erros por camada com um limite rígido e checar a acurácia final — pode ser aplicada a outras redes neurais unidimensionais em áreas como monitores de saúde vestíveis, sensores industriais e veículos inteligentes, ajudando a garantir que, quando os algoritmos saem do laboratório e chegam aos dispositivos, suas decisões permaneçam confiáveis.

Citação: Bal, S. Towards the transformation of MATLAB models into FPGA-Based hardware accelerators. Sci Rep 16, 5027 (2026). https://doi.org/10.1038/s41598-026-36033-z

Palavras-chave: aceleradores FPGA, redes neurais MATLAB, classificação de arritmia por ECG, verificação de hardware, deep learning em ponto fixo