Clear Sky Science · pt

Otimização de desempenho de InSe-FETs usando materiais dielétricos high-k para aplicações analógicas/RF

Eletrônica mais rápida e inteligente em uma folha minúscula

Gadgets modernos — de celulares 5G a radares e scanners médicos — dependem de transistores capazes tanto de amplificar sinais fracos quanto de operar em velocidades muito altas. Este artigo investiga como um material ultrafino promissor, o seleneto de índio (InSe), pode ser ajustado para oferecer maior ganho de sinal em futuros circuitos analógicos e de radiofrequência (RF), do tipo usado em comunicação sem fio e sensoriamento. Ao escolher cuidadosamente a camada isolante que fica ao lado do canal ativo no transistor, os autores mostram como aumentar o desempenho enquanto navegam por um trade‑off inevitável entre potência e velocidade.

Novos materiais além do silício cotidiano

Por décadas, o silício foi o cavalo de batalha da eletrônica, mas os engenheiros agora miram materiais atomicamente finos que podem ser descascados em camadas de apenas alguns átomos de espessura. Esses materiais “2D” podem ser flexíveis, transparentes e altamente eficientes no transporte de carga elétrica. O grafeno foi a primeira estrela dessa classe, mas, por não ter uma lacuna de energia, ele tem dificuldades em comutação convencional liga–desliga. Materiais como o seleneto de índio oferecem um meio termo: mantêm os benefícios das camadas 2D ao mesmo tempo em que têm uma bandgap que permite que os dispositivos comutem de forma limpa e operem com baixo consumo. Estudos anteriores focaram principalmente o InSe para lógica digital e detecção de luz; este trabalho desloca a atenção para seu papel em circuitos analógicos e RF, onde a amplificação suave e o comportamento em altas frequências importam mais do que a simples comutação binária.

Como mudar a camada invisível altera o comportamento do dispositivo

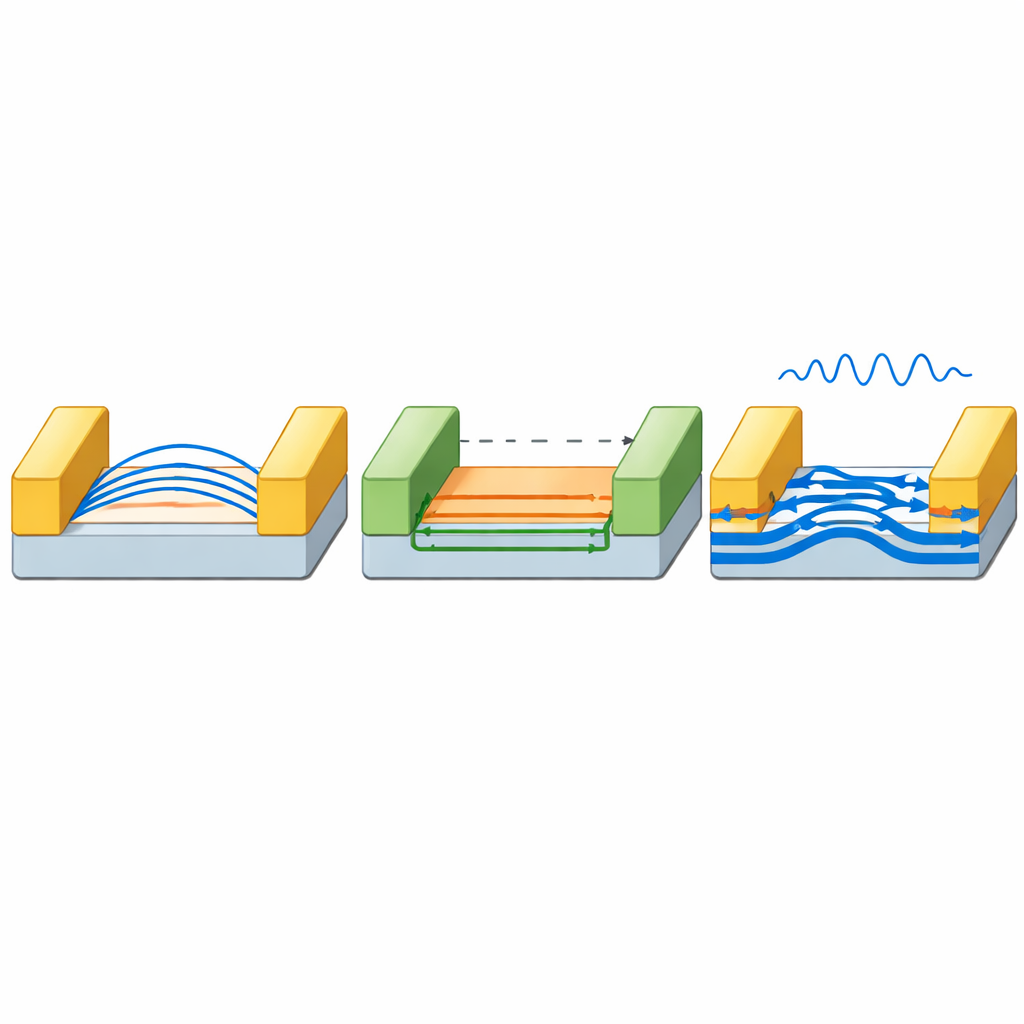

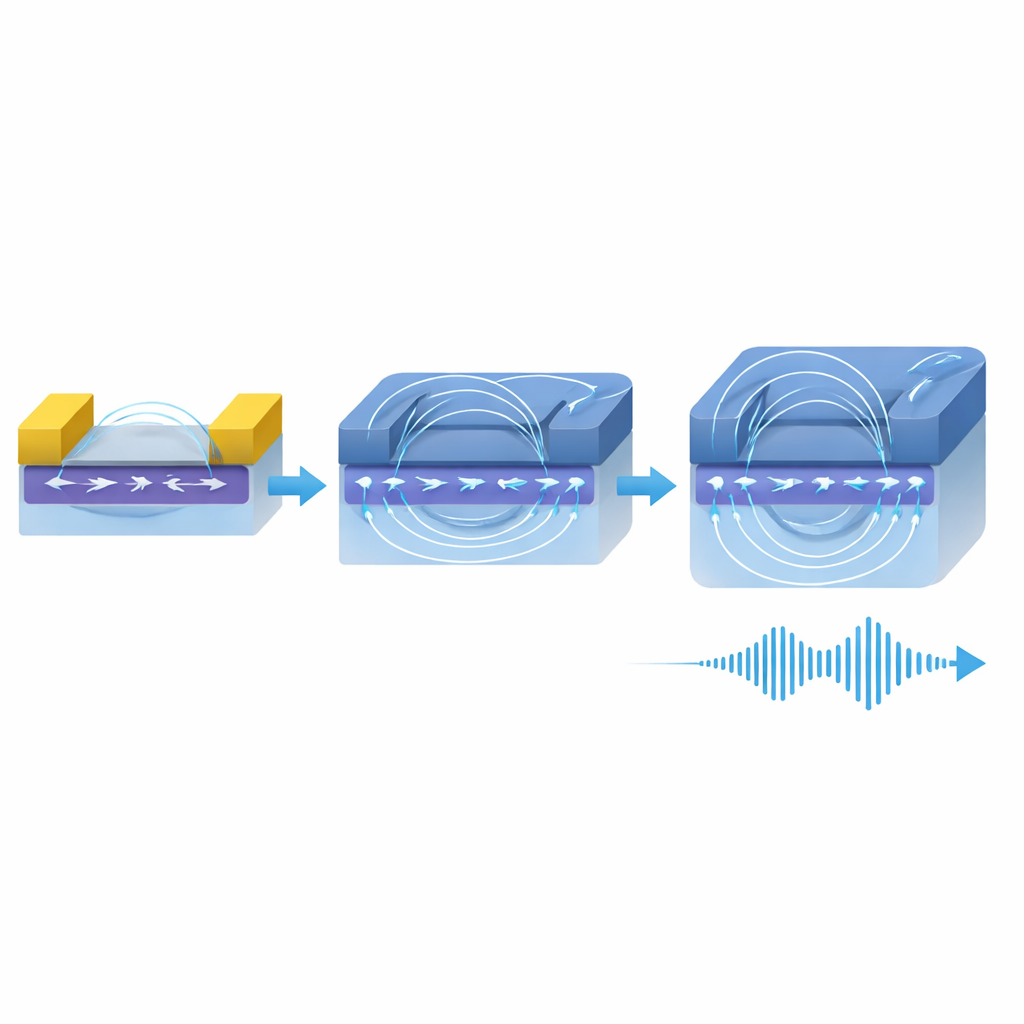

Todo transistor de efeito de campo depende de um gate que controla um canal fino de carga usando uma camada isolante, ou dielétrico, entre eles. Aqui, os autores simulam transistores de InSe com diferentes materiais dielétricos, desde um óxido padrão semelhante aos usados em chips de silício até os chamados dielétricos high‑k que armazenam carga elétrica de forma mais eficaz. Usando modelos computacionais detalhados em nível quântico, eles calculam como os elétrons viajam por uma fita de InSe de escala nanométrica quando a tensão de gate é variada. À medida que a constante dielétrica aumenta, o campo elétrico do gate ‘‘agarra’’ o canal mais fortemente, puxando mais carga em movimento e reduzindo a barreira de energia que os elétrons devem superar. Isso leva a uma corrente maior quando o dispositivo está ligado e a uma separação mais nítida entre os estados ligado e desligado, o que é uma boa notícia tanto para uso digital quanto analógico.

Transformando melhor controle em ganho de sinal mais forte

O foco real do estudo são as figuras de mérito analógicas e RF — quantidades que descrevem quão bem um transistor pode amplificar sinais e a que custo em potência ou largura de banda. Com materiais high‑k, os dispositivos de InSe simulados mostram quase o dobro da transcondutância, uma medida de quão efetivamente variações na tensão de entrada se transformam em variações na corrente de saída. Isso, por sua vez, eleva o ganho intrínseco, que combina a transcondutância com a firmeza com que o dispositivo sustenta sua tensão de saída. Os autores também examinam medidas compostas que misturam ganho, velocidade e eficiência — como quanto ganho pode ser alcançado a uma dada frequência de operação ou quão efetivamente cada unidade de corrente é usada para obter amplificação. Em todas essas métricas, os dielétricos de k mais alto oferecem vantagens claras, às vezes melhorando os indicadores de desempenho em 70 a mais de 150 por cento.

O custo do reforço: um golpe na velocidade máxima

Não há, no entanto, almoço grátis. O mesmo dielétrico high‑k que fortalece o controle do gate sobre o canal também aumenta a capacitância do dispositivo, ou seja, armazena mais carga que precisa ser movimentada toda vez que o transistor comuta. Embora a corrente de condução e o ganho melhorem, essa carga extra desacelera o ritmo final de operação do transistor, reduzindo ligeiramente a frequência de corte — o ponto em que ele deixa de fornecer amplificação útil. Nas simulações, essa métrica de velocidade cai cerca de 10 por cento no caso de k mais alto em comparação com o óxido convencional. Os autores destacam isso como um trade‑off de projeto: engenheiros podem ajustar a escolha do dielétrico dependendo se o objetivo é ganho forte, frequência máxima ou um equilíbrio ideal entre os dois.

O que isso significa para chips futuros de comunicação e sensoriamento

Em termos simples, o estudo mostra que, ao trocar a fina camada isolante em um transistor de InSe por um material que ‘‘segura’’ melhor a carga, os engenheiros podem construir chaves minúsculas que amplificam sinais muito mais efetivamente, embora com uma modesta redução na velocidade máxima. Isso torna dispositivos InSe com dielétricos high‑k especialmente atraentes para circuitos analógicos e RF de baixa tensão, onde ganho limpo e eficiência energética importam mais do que alcançar as frequências absolutas mais altas. À medida que a modelagem se torna mais realista — incorporando efeitos como espalhamento e defeitos — e as técnicas de fabricação melhoram, tais transistores com materiais 2D ajustados podem sustentar uma nova geração de tecnologias de comunicação e sensoriamento flexíveis e econômicas em energia.

Citação: Ahmad, M.A., Imam, M., Mech, B.C. et al. Performance optimization of InSe-FETs using high-k dielectric materials for analog/RF applications. Sci Rep 16, 9573 (2026). https://doi.org/10.1038/s41598-025-21242-9

Palavras-chave: transistores de seleneto de índio, dielétricos high-k, eletrônica analógica RF, dispositivos semicondutores 2D, simulação em nanoeletrônica