Clear Sky Science · pl

Układy pamięci z komórkami wzmocnienia na bazie półprzewodników tlenkowych: materiały i strategie integracji dla następnej generacji pamięci na chipie

Dlaczego szybsza, mądrzejsza pamięć ma znaczenie

Nasze telefony, laptopy i centra danych stają się coraz wydajniejsze, ale istnieje ukryty limit prędkości: przesyłanie danych między procesorem a pamięcią. Ten artykuł opisuje nowy rodzaj pamięci na chipie, który mógłby złagodzić tę „ścianę pamięci”, sprawiając, że przyszłe komputery będą szybsze i bardziej energooszczędne w zadaniach takich jak sztuczna inteligencja, chmura obliczeniowa i codzienne aplikacje. Przemyślawszy sposób budowy komórek pamięci i dobór materiałów, badacze dążą do upakowania znacznie większej ilości danych blisko procesora przy jednoczesnym ograniczeniu zużycia energii i wydzielania ciepła.

Wąskie gardło we wnętrzu współczesnych komputerów

Przez dekady wydajność procesorów rosła znacznie szybciej niż pamięć główna dostarczająca im dane. Ta niespójność, znana jako ściana pamięci, oznacza, że szybkie układy często czekają bezczynnie na informacje. Projektanci próbowali łagodzić to ograniczenie, stosując wielowarstwowe pamięci podręczne umieszczone bezpośrednio na procesorze. Obecne pamięci podręczne opierają się na pamięci SRAM, która jest bardzo szybka, ale zajmuje dużo miejsca i pobiera dużo energii, ponieważ każdy bit wymaga sześciu tranzystorów. Aby uzyskać większą pojemność, firmy układają układy SRAM w trzecim wymiarze lub dodają osadzony DRAM na chipie, ale konwencjonalny DRAM wciąż zależy od małych kondensatorów, które są trudne do wykonania na ekstremalnych skalach i ciężkie do zintegrowania ze standardową logiką.

Inny rodzaj komórki pamięci

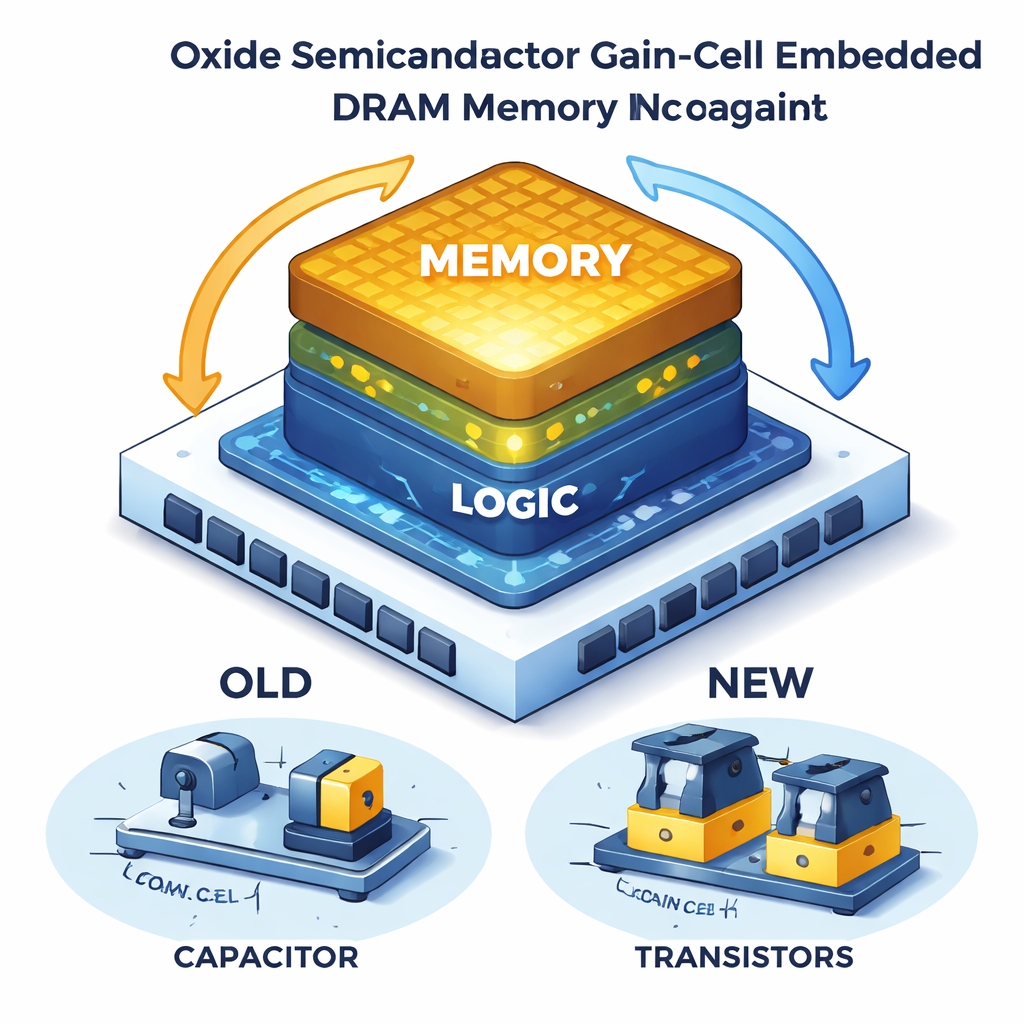

Artykuł koncentruje się na alternatywie zwanej DRAM osadzonym z komórką wzmocnienia, czyli GC-eDRAM. Zamiast używać oddzielnego kondensatora do przechowywania ładunku, komórka wzmocnienia wykorzystuje tylko tranzystory do utrzymania danych, upraszczając strukturę i ułatwiając zgodność z standardowymi procesami produkcji chipów. Ten projekt naturalnie pasuje do trójwymiarowego układania nad obwodami logicznymi, obiecując wysoką gęstość układów „pamięć-na-logice”. Kolejną zaletą jest „odczyt bez destrukcji”: odczytanie zapisanego stanu nie wyczerpuje go natychmiast, co może zmniejszyć częstotliwość odświeżania pamięci. Jednak w tradycyjnych krzemowych wersjach przechowywany ładunek ulatnia się w czasie krótszym niż milisekunda, więc częste operacje odświeżania wciąż marnują energię i ograniczają użyteczność.

Półprzewodniki tlenkowe: cichsze, chłodniejsze przełączniki

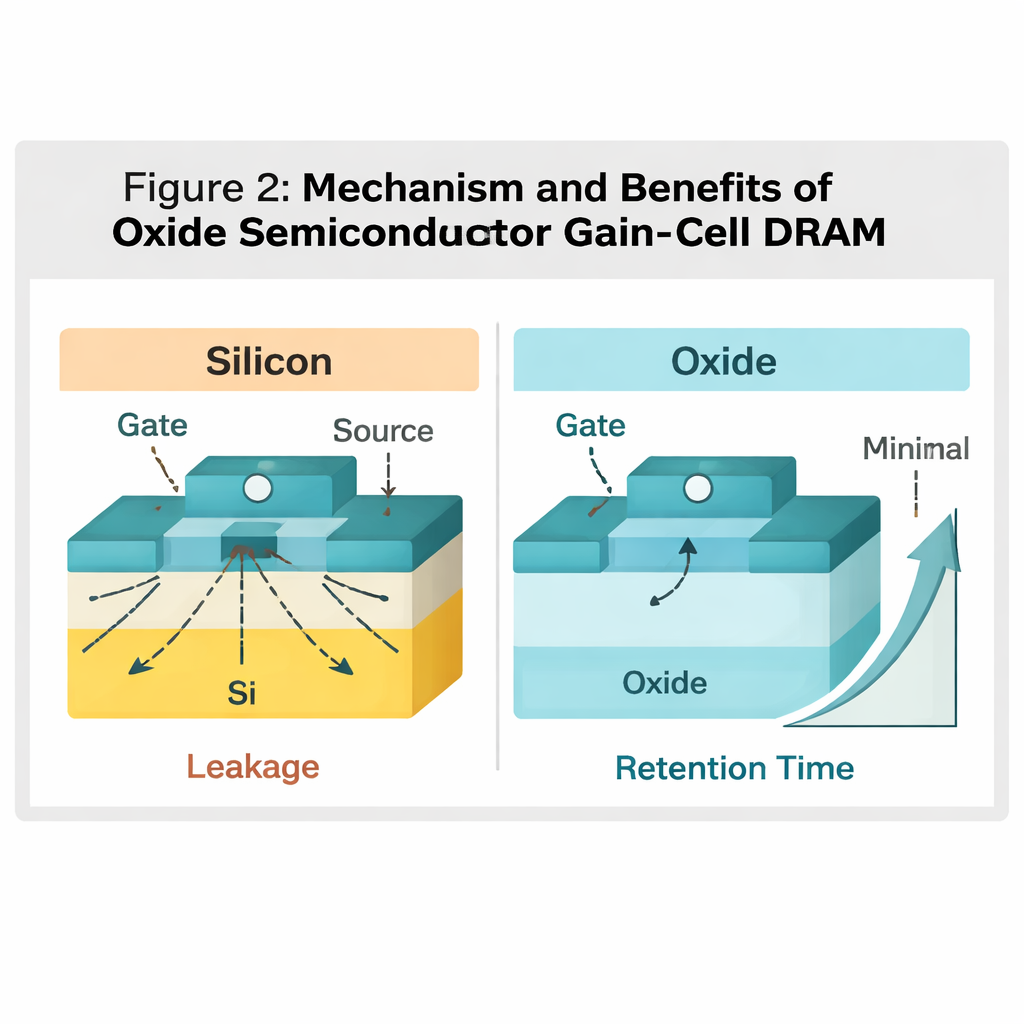

Aby przezwyciężyć przecieki w komórkach wzmocnienia, autorzy wskazują na półprzewodniki tlenkowe — materiały takie jak tlenek indu-galu-cynku (IGZO) i pokrewne związki — jako nowe materiały kanałowe dla tranzystorów. Te tlenki mają szeroką przerwę energetyczną, co silnie tłumi niepożądane prądy, gdy tranzystor ma być wyłączony. Pomiary wykazały prądy wyłączenia tak niewielkie, że zbliżają się do granic aparatury pomiarowej, a prototypowe komórki wzmocnienia przechowują dane przez wiele sekund, godzin, a nawet ponad dobę, w porównaniu z tysięcznymi części sekundy w konstrukcjach krzemowych. Co istotne, tlenki te można osadzać w stosunkowo niskich temperaturach zgodnych z „tylnymi” etapami produkcji chipów, co pozwala inżynierom budować gęste warstwy pamięci bezpośrednio na istniejącej logice krzemowej bez jej uszkadzania.

Budowanie w górę: stosy 3D i mikroskopijne tranzystory

W miarę jak układy nadal się zmniejszają, samo pomniejszanie tranzystorów wprowadza nowe problemy, takie jak słaba kontrola nad kanałem i rosnące przecieki. Artykuł przegląda zaawansowane kształty tranzystorów, które oplatają bramkę wokół kanału (rozwiązania gate-all-around i channel-all-around), aby utrzymać ścisłą kontrolę nawet przy nanometrowych rozmiarach. Wykorzystując półprzewodniki tlenkowe w tych wielobramkowych strukturach, badacze wykazali bardzo krótkie kanały, ekstremalnie niskie przecieki i silne zatrzymywanie danych przy jednoczesnym pionowym układaniu wielu warstw pamięci. Niektóre eksperymentalne projekty już osiągają lub przewyższają efektywność powierzchniową najlepszych dzisiejszych komórek DRAM, sugerując, że przyszłe układy mogą pomieścić ogromne pojemności pamięci na bardzo małej powierzchni tuż nad rdzeniami procesora.

Od materiałów laboratoryjnych do niezawodnych produktów

Przekształcenie tych obiecujących urządzeń w praktyczną pamięć wymaga starannego inżynierskiego podejścia do materiałów. Artykuł opisuje, jak zmiana składu metali w tlenku, kontrola zawartości tlenu i krystalizacja warstw mogą zbalansować dużą prędkość z długoterminową stabilnością. Omawia także metody zarządzania defektami, zanieczyszczeniami wodorem oraz delikatnymi interfejsami między tlenkami a warstwami izolującymi, tak aby urządzenia pozostały stabilne przy działaniu w wysokich temperaturach i długotrwałej eksploatacji. Na koniec porusza kwestie projektowania połączeń metalicznych tak, by rezystancja styku nie niwelowała zalet nowych materiałów. Razem te strategie mają na celu dostarczenie pamięci zarówno gęstej, jak i wystarczająco niezawodnej do produkcji na dużą skalę.

Co to oznacza dla codziennego użytkowania komputerów

Autorzy konkludują, że pamięci z komórkami wzmocnienia na bazie półprzewodników tlenkowych mogą przekształcić sposób projektowania przyszłych układów. Łącząc drobne, o niskich przeciekach komórki pamięci z układaniem 3D nad obwodami logicznymi, projektanci mogliby umieścić znacznie więcej szybkiej pamięci obok procesora przy zachowaniu kontrolowanego zużycia energii. To złagodziłoby ścianę pamięci, pomagając akceleratorom AI, serwerom chmurowym i urządzeniom osobistym działać szybciej i efektywniej. Chociaż istnieją wyzwania związane z niezawodnością, jednorodnością produkcji i integracją całego układu, przeglądany tutaj materiał wyznacza jasną ścieżkę ku bardziej zwartej, wydajnej i energooszczędnej architekturze komputerowej.

Cytowanie: Chung, S.W., Yoon, S.H. & Jeong, J.K. Oxide semiconductor gain cell-embedded memory: materials and integration strategies for next generation on-chip memory. Commun Eng 5, 39 (2026). https://doi.org/10.1038/s44172-026-00616-5

Słowa kluczowe: pamięć na chipie, półprzewodniki tlenkowe, skalowanie DRAM, układy 3D, sprzęt AI