Clear Sky Science · pl

W kierunku przekształcania modeli MATLAB w akceleratory sprzętowe oparte na FPGA

Przekształcanie algorytmów laboratoryjnych w urządzenia świata rzeczywistego

Wiele współczesnych przełomów medycznych i inżynierskich zaczyna życie jako oprogramowanie napisane przez badaczy, często w narzędziach przyjaznych użytkownikowi, takich jak MATLAB. Gdy te same algorytmy muszą jednak działać w czasie rzeczywistym — na przykład wykrywać niebezpieczne zaburzenia rytmu serca na podstawie elektrokardiogramu (EKG) — potrzebna jest szybkość i efektywność niestandardowego sprzętu. Artykuł pokazuje, jak wiarygodnie przenieść złożoną sieć neuronową wykrywającą uderzenia serca z MATLAB-a na specjalizowany układ zwany FPGA, nie tracąc przy tym dokładności, na której polegają lekarze i inżynierowie.

Dlaczego przepisywanie kodu na układy jest tak trudne

FPGA (Field-Programmable Gate Arrays) to rekonfigurowalne układy cenione za szybkość i niskie zużycie energii. Tradycyjnie ich programowanie wymagało języków bliskich sprzętowi, takich jak VHDL czy Verilog, które są dalekie od wysokopoziomowego kodu matematycznego i przetwarzania sygnałów, jaki piszą naukowcy w MATLAB-ie. Nowe narzędzia potrafią automatycznie przekształcać algorytmy na opisy sprzętowe, ale często wymagają ręcznych poprawek i koncentrują się głównie na wydajności: jak szybko działa układ, ile zasobów zużywa. Brakowało jasnego sposobu na udowodnienie, że sprzęt robi dokładnie to samo, co oryginalne oprogramowanie, warstwa po warstwie, liczba po liczbie.

Krok po kroku — weryfikacja każdej warstwy sieci

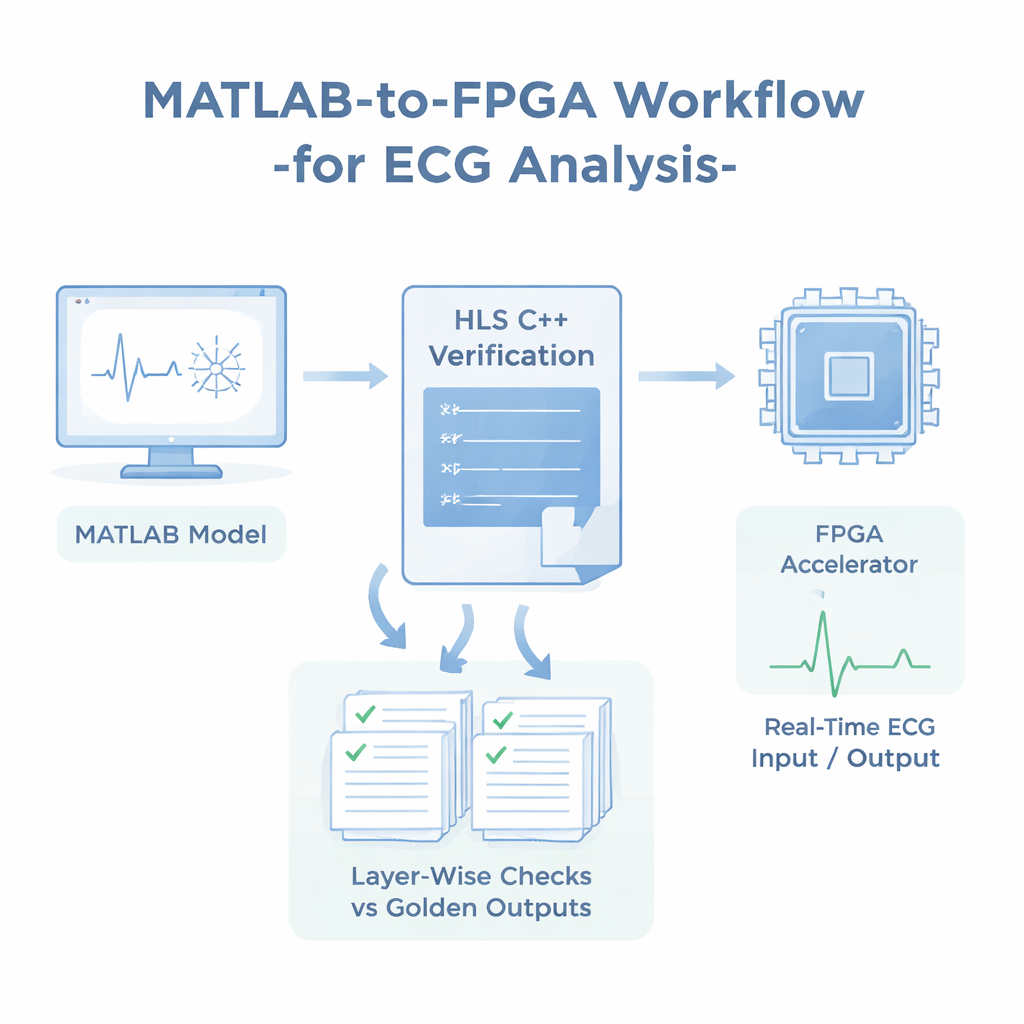

Autor wypełnia tę lukę, proponując proces weryfikacji dla jednowymiarowej sieci konwolucyjnej klasyfikującej uderzenia serca na podstawie dobrze znanej bazy MIT-BIH Arrhythmia Database. Sieć, zbudowana w MATLAB-ie, analizuje krótkie fragmenty sygnału EKG i przypisuje je do jednego z pięciu typów uderzeń, w tym normalnych i kilku nieprawidłowych rytmów. Trzy wersje sieci o różnej głębokości są trenowane na tych samych danych. Po treningu wagi, przesunięcia (biasy) oraz wyjścia każdej warstwy na sygnałach testowych są zapisywane jako „złote wyjścia” — precyzyjny zapis liczbowy zachowania modelu MATLAB.

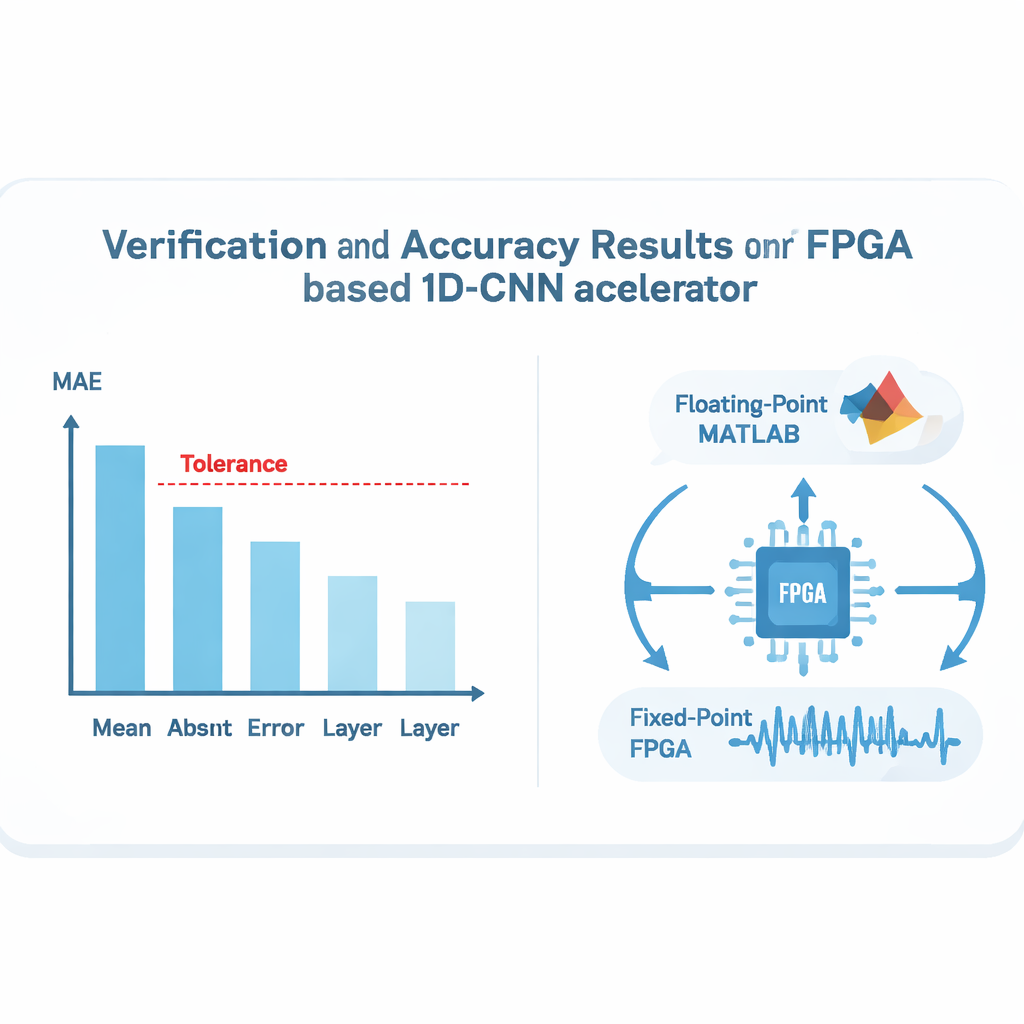

Z MATLAB-a do C++ na FPGA, z kontrolą liczb

Zamiast naciskać automatyczny przycisk „konwertuj”, sieć jest ręcznie implementowana w C++, zachowując ten sam układ danych i kroki matematyczne jak w MATLAB-ie. Ten kod C++ jest następnie używany z narzędziem wysokopoziomowej syntezy, aby wygenerować sprzęt działający na płytce FPGA PYNQ-Z1. Na każdym etapie — MATLAB, C++ i FPGA — wyjścia warstw porównuje się ze zapisanymi złotymi wyjściami za pomocą prostego miernika: średniego błędu bezwzględnego, który mierzy średnią różnicę liczbową między dwoma zestawami wyników. Badanie przyjmuje rygorystyczną tolerancję: wszystkie warstwy muszą mieścić się poniżej błędu 1.5×10⁻³. Na tysiącach próbek EKG każda testowana warstwa spełnia ten cel, a końcowa dokładność klasyfikacji pozostaje praktycznie niezmieniona: około 98.3–98.4% w MATLAB-ie i C++, a na FPGA spada tylko o około 0.2 punktu procentowego, różnica zgodna z oczekiwanymi efektami stosowania krótszych, stałoprzecinkowych reprezentacji w sprzęcie.

Przyspieszanie sprzętu bez naruszania matematyki

Gdy poprawność zostanie potwierdzona, projekt jest dopracowywany pod kątem prędkości. Najbardziej wymagające elementy sieci — warstwy konwolucyjne — są mapowane na programowalną logikę FPGA, używając arytmetyki stałoprzecinkowej dla efektywności, podczas gdy lżejsze zadania, takie jak końcowe obliczenie softmax, wykonuje wbudowany procesor układu z normalnymi liczbami zmiennoprzecinkowymi. Techniki takie jak potokowanie pętli (loop pipelining), rozwijanie pętli (loop unrolling) oraz ostrożne dzielenie pamięci na równoległe banki pozwalają na równoległe wykonywanie różnych części obliczeń i transferów danych. Zoptymalizowana wersja sprzętu przetwarza okno z uderzeniem serca w około 1.7 milisekundy i mieści się komfortowo w limitach zasobów i mocy FPGA, zachowując jednocześnie numeryczne zachowanie warstw oryginalnego modelu MATLAB.

Co to oznacza dla przyszłych inteligentnych urządzeń

Dla osób niebędących specjalistami kluczowy przekaz jest taki, że dziś możliwe jest nie tylko przyspieszenie zaawansowanego klasyfikatora rytmu serca opartego na MATLAB-ie na energooszczędnym układzie, lecz także udowodnienie, że wewnętrzne działanie układu sprzętowego odpowiada zaufanemu modelowi programowemu na każdej warstwie. Zamiast gonić za szybkością kosztem niezawodności, podejście to buduje czytelny ślad audytu od obliczeń zmiennoprzecinkowych w MATLAB-ie do stałoprzecinkowego sprzętu FPGA. Ta sama recepta weryfikacyjna — zapisywanie złotych wyjść, porównywanie błędów warstwa po warstwie z surowym progiem i sprawdzanie końcowej dokładności — może być stosowana do innych jednowymiarowych sieci neuronowych w obszarach takich jak opaski zdrowotne, czujniki przemysłowe czy inteligentne pojazdy, pomagając zapewnić, że gdy algorytmy opuszczają laboratorium i trafiają do urządzeń, ich decyzje pozostają wiarygodne.

Cytowanie: Bal, S. Towards the transformation of MATLAB models into FPGA-Based hardware accelerators. Sci Rep 16, 5027 (2026). https://doi.org/10.1038/s41598-026-36033-z

Słowa kluczowe: akceleratory FPGA, sieci neuronowe MATLAB, klasyfikacja arytmii z EKG, weryfikacja sprzętu, uczenie głębokie stałoprzecinkowe