Clear Sky Science · nl

Oxide halfgeleider gaincel-embedded geheugen: materialen en integratiestrategieën voor de volgende generatie on-chip geheugen

Waarom sneller, slimmer geheugen er toe doet

Onze telefoons, laptops en datacenters worden steeds krachtiger, maar er blijft een verborgen snelheidsgrens: het verplaatsen van data tussen de processor en het geheugen. Dit artikel onderzoekt een nieuw type on-chip geheugen dat deze “memory wall” kan verlichten, waardoor toekomstige computers sneller en energiezuiniger worden voor taken zoals kunstmatige intelligentie, cloudcomputing en alledaagse apps. Door opnieuw na te denken over hoe geheugencellen zijn opgebouwd en welke materialen ze gebruiken, proberen onderzoekers veel meer data dicht bij de processor te plaatsen terwijl het energiegebruik en de warmteafgifte verminderen.

De bottleneck binnen moderne computers

Decennialang is de prestatie van processors veel sneller verbeterd dan het hoofdgeheugen dat de processor van data voorziet. Deze mismatch, bekend als de memory wall, betekent dat snelle chips vaak stil zitten te wachten op informatie. Ontwerpers hebben geprobeerd deze bottleneck te verzachten met meerdere lagen cachegeheugen direct op de processor. De caches van vandaag vertrouwen op een geheugenstype genaamd SRAM, dat erg snel maar ruimtelijk en energie-intensief is omdat elke bit zes transistors vereist. Om meer capaciteit te krijgen stapelen bedrijven SRAM-chips in drie dimensies of voegen ze embedded DRAM op de chip toe, maar conventionele DRAM is nog steeds afhankelijk van kleine condensatoren die moeilijk te vervaardigen zijn op extreme schalen en lastig te integreren met standaard logica-circuits.

Een ander soort geheugencel

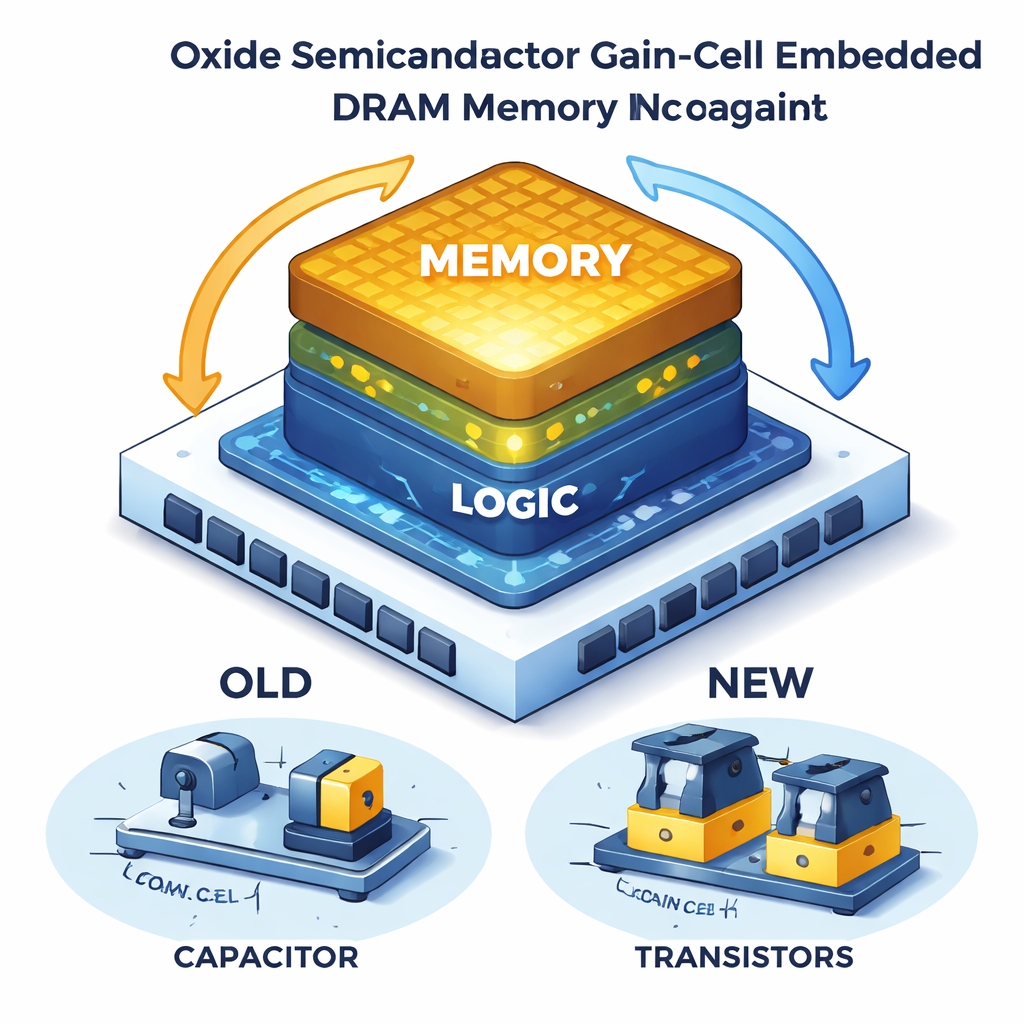

Het artikel richt zich op een alternatief genaamd gain-cell embedded DRAM, of GC-eDRAM. In plaats van een aparte condensator te gebruiken om lading op te slaan, gebruikt een gaincel alleen transistors om data vast te houden, waardoor de structuur wordt vereenvoudigd en deze vriendelijker wordt voor standaard chipfabricage. Dit ontwerp past van nature in driedimensionale stapeling bovenop logica-circuits en belooft hoge-dichtheid “memory-on-logic”-lay-outs. Een ander voordeel is het ‘niet-destructief lezen’: het uitlezen van een opgeslagen waarde put deze niet direct uit, wat kan verminderen hoe vaak het geheugen moet worden ververst. In traditionele siliciumvarianten lekt de opgeslagen lading echter weg in minder dan een milliseconde, waardoor frequente refresh-operaties nog steeds energie verspillen en het nut beperken.

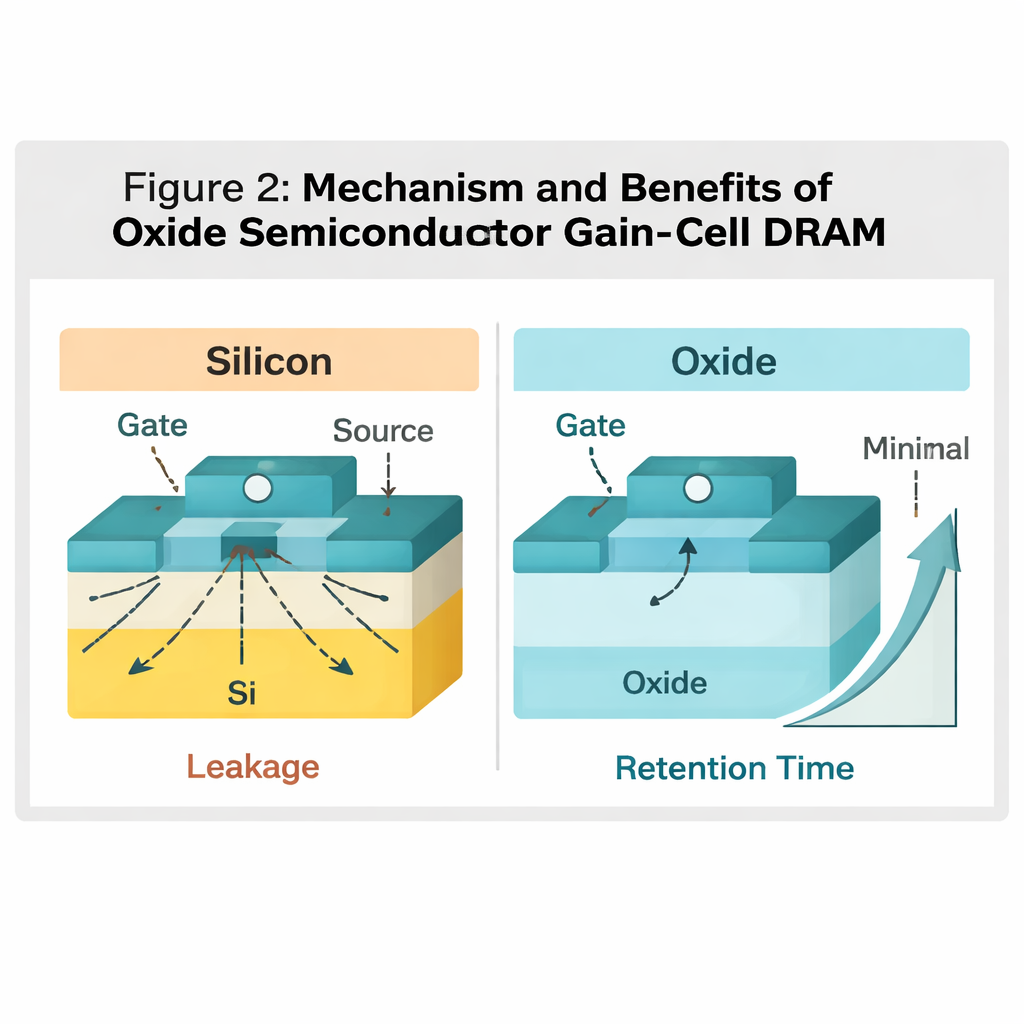

Oxide halfgeleiders: stillere, koelere schakelaars

Om lekverlies in gaincellen te overwinnen, benadrukken de auteurs oxide halfgeleiders — materialen zoals indium-gallium-zwaveloxide (IGZO) en verwante verbindingen — als nieuwe kanaalmaterialen voor de transistors. Deze oxiden hebben een brede bandopening, wat ongewenste stroom wanneer een transistor uitgeschakeld hoort te zijn sterk onderdrukt. Experimenten hebben uit- stromen gemeten die zo klein zijn dat ze nabij de meetgrenzen van de apparatuur liggen, en prototype-gaincellen bewaren nu data voor vele seconden, uren of zelfs meer dan een dag, vergeleken met duizendsten van een seconde in siliciumontwerpen. Cruciaal is dat deze oxiden kunnen worden afgezet bij relatief lage temperaturen die compatibel zijn met de “back-end” van chipfabricage, waardoor ingenieurs dichte geheugenniveaus direct boven bestaande siliciumlogica kunnen bouwen zonder deze te beschadigen.

Opbouwen naar boven: 3D-stapels en kleine transistors

Terwijl chips blijven krimpen, veroorzaakt het simpelweg kleiner maken van transistors nieuwe problemen, zoals slechtere beheersing van het kanaal en toenemende lekstromen. Het artikel bespreekt geavanceerde transistorvormen die het gate-gebied rondom het kanaal wikkelen (gate-all-around en channel-all-around ontwerpen) om strakke controle te behouden, zelfs op nanometerschaal. Door oxide halfgeleiders in deze multi-gate structuren te gebruiken, hebben onderzoekers zeer korte kanalen, extreem lage lekstromen en sterke databehoudswaarden aangetoond, terwijl ze meerdere geheugenniveaus verticaal stapelen. Sommige experimentele ontwerpen bereiken al of overtreffen de arealefficiëntie van de beste DRAM-cellen van vandaag, wat suggereert dat toekomstige chips enorme geheugencapaciteit in een zeer klein oppervlak direct boven de processorkernen kunnen huisvesten.

Van labmaterialen naar betrouwbare producten

Het omzetten van deze veelbelovende apparaten naar praktisch toepasbaar geheugen vereist zorgvuldige materiaaltechniek. Het artikel beschrijft hoe het afstemmen van de metalenmix in het oxide, het beheersen van het zuurstofgehalte en het kristalliseren van de films snelheid en langetermijnstabiliteit in balans kunnen brengen. Het behandelt ook manieren om defecten, waterstofverontreiniging en de delicate interfaces tussen oxiden en isolerende lagen te beheren, zodat apparaten stabiel blijven onder warmte en langdurige werking. Tot slot bespreekt het de engineering van de metalen verbindingen zodat contactweerstand de voordelen van de nieuwe materialen niet tenietdoet. Samen mikken deze strategieën op geheugen dat zowel dicht als betrouwbaar genoeg is voor grootschalige productie.

Wat dit betekent voor alledaags computergebruik

De auteurs concluderen dat oxide halfgeleider gain-cell geheugen kan herdefiniëren hoe toekomstige chips worden opgebouwd. Door kleine, laag-lek geheugencellen te combineren met 3D-stapeling boven logica-circuits, zouden ontwerpers veel meer snel geheugen naast de processor kunnen plaatsen terwijl het energieverbruik onder controle blijft. Dit zou de memory wall verzachten en alles helpen, van AI-accelerators tot cloudservers en persoonlijke apparaten, sneller en efficiënter te draaien. Hoewel er uitdagingen blijven op het gebied van betrouwbaarheid, uniformiteit in fabricage en volledige chipintegratie, schetst het hier besproken werk een duidelijke route naar compactere, krachtigere en energiebewustere computersystemen.

Bronvermelding: Chung, S.W., Yoon, S.H. & Jeong, J.K. Oxide semiconductor gain cell-embedded memory: materials and integration strategies for next generation on-chip memory. Commun Eng 5, 39 (2026). https://doi.org/10.1038/s44172-026-00616-5

Trefwoorden: on-chip geheugen, oxide halfgeleiders, DRAM-scaling, 3D geïntegreerde schakelingen, AI-hardware