Clear Sky Science · nl

Het in kaart brengen van diverse hysteresedynamica in geschaalde MoS2-FETs met behulp van de universele methode afgeleid van TCAD-modellering

Waarom kleine schakelaars betrouwbaar gedrag nodig hebben

Moderne elektronica gaat steeds kleiner en tweedimensionale (2D) materialen zoals molybdeendisulfide (MoS2) behoren tot de belangrijkste kandidaten voor toekomstige chips. Maar naarmate die schakelaars krimpen, kan hun gedrag inconsistent worden: hetzelfde apparaat kan anders reageren, afhankelijk van hoe het net daarvoor is gebruikt. Dit geheugenachtige effect, hysteresie genoemd, wordt vaak afgedaan als een klein ongemak. In dit werk laten de auteurs zien dat hysteresie juist een schat aan informatie verbergt over verborgen gebreken in geavanceerde transistoren — en ze introduceren een universele manier om die informatie uit te lezen.

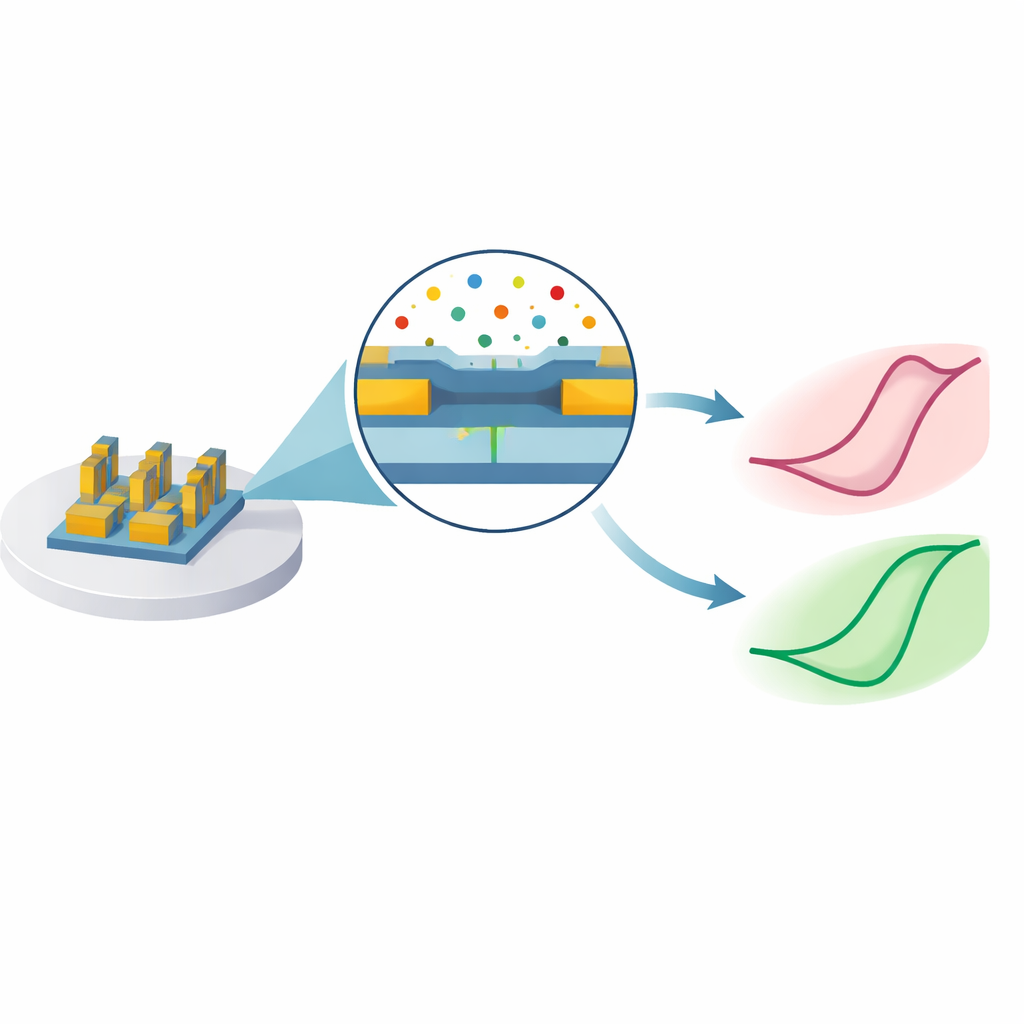

Hoe transistors van de volgende generatie zijn opgebouwd

Toekomstige 2D-veld-effecttransistoren gebruiken een ultradunne MoS2-laag als kanaal waar stroom doorheen loopt, bedekt door een zeer dun isolerend oxide zoals hafniumoxide (HfO2), met een metalen gate erboven. Om apparaten verder te verkleinen, moet dit oxide in elektrische termen ongeveer één nanometer dik zijn, wat betekent dat elk individueel defect daarin het kanaal sterk kan verstoren. Deze defecten werken als kleine vallen die tijdelijk elektrische lading kunnen vasthouden of loslaten. Omdat defecten op verschillende dieptes in het oxide kunnen zitten en kunnen interageren met zowel het kanaal als de gate, kan hun collectieve gedrag de transistor op subtiele wijze stabiliseren of destabiliseren. Het begrijpen van dit defectlandschap is cruciaal als 2D-transistoren willen concurreren met de huidige siliciumtechnologie.

Waarom de transistor zijn verleden onthoudt

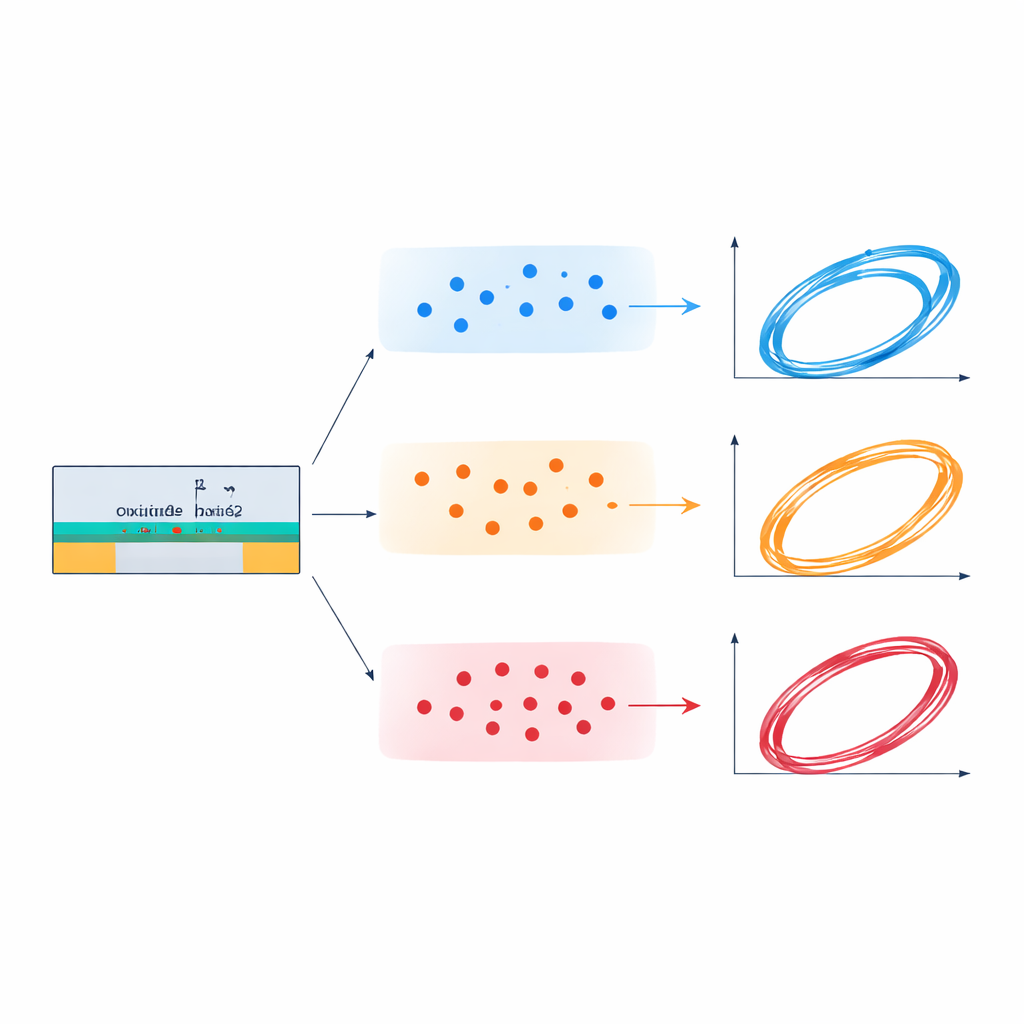

Wanneer ingenieurs de gate-spanning omhoog en omlaag laten lopen en de stroom registreren, constateren ze vaak dat de opwaartse en neerwaartse metingen niet samenvallen. Deze lus is de hysteresie. Traditioneel meten onderzoekers de afstand tussen de twee krommen op één werkpunt en noemen dat de hysteresisbreedte, vaak concluderend dat die "klein" of "verwaarloosbaar" is. De auteurs stellen dat die praktijk misleidend is, vooral voor geschaalde apparaten waarin verschillende groepen defecten tegengesteld kunnen bijdragen. Afhankelijk van de meetsnelheid en de bedrijfstroom kan dezelfde transistor conventionele met de klok mee lopende lussen, omgekeerde tegen de klok in lopende lussen, wisseling tussen beide, of zelfs bijna geen hysteresie vertonen wanneer tegengestelde effecten elkaar opheffen.

Een universele kaart verborgen in de krommen

Om deze complexiteit te ontwarren, gebruikt het team gedetailleerde computersimulaties (TCAD) van nanoschaal MoS2-transistoren met zorgvuldig gecontroleerde defectpopulaties op verschillende dieptes in het oxide. Ze stellen vervolgens een universele methode voor het in kaart brengen van hysteresie voor. In plaats van één getal te extraheren, scannen ze de hysteresisbreedte over een breed stroombereik — van net boven de uit-toestand tot bijna de aan-toestand — en voor sweeptijden die vele ordes van grootte beslaan. Dit levert duizenden krommen op die laten zien hoe hysteresie verandert met meetsnelheid bij elke stroom. Daaruit definiëren ze boven- en ondergrenzen als "universele hysteresisfuncties" die al het mogelijke gedrag omsluiten. Deze enveloppen tonen duidelijk welke soorten defecten actief zijn, of ze voornamelijk met het kanaal of met de bovenste gate interageren, en of ze lussen met de klok mee of ertegen in prefereren.

Het koppelen van snelle lussen aan langzame drift

Dezelfde defecten die hysteresie veroorzaken, drijven ook langzame driften in transistorgedrag onder langdurige stress aan, een probleem bekend als bias temperature instability (BTI). Door standaard stress‑en‑herstel experimenten te simuleren, leggen de auteurs verbanden tussen kenmerken in hun hysterieschema’s en ongebruikelijke BTI-signaturen, zoals een schijnbare negatieve verschuiving die pas later terugveert naar een positieve. Ze laten zien dat vallen nabij het kanaal de neiging hebben tot langzame, grotendeels permanente verschuivingen, terwijl vallen dichter bij de gate snellere maar grotendeels omkeerbare veranderingen veroorzaken. Hun methode is toepasbaar niet alleen op gesimuleerde MoS2‑apparaten maar ook op gemeten data van echte MoS2‑ en WSe2‑transistoren uit onderzoekscleanrooms en pilotfabricagelijnen, inclusief gevallen waar bewegende ionen in het oxide meedoen aan het ladingsvangstspel.

Van complexe data naar praktische richtlijnen

Door rommelige hysteresislussen om te zetten in gestandaardiseerde kaarten, biedt dit werk een krachtig diagnostisch instrument voor opkomende transistorstechnologieën. De methode werkt direct op experimentele datasets en vereist geen toegang tot geavanceerde simulatietools, waardoor hij breed inzetbaar is in verschillende laboratoria. Voor ingenieurs is de kernboodschap dat hysteresie niet alleen een fout is die geminimaliseerd moet worden, maar een vingerafdruk van onderliggende betrouwbaarheidproblemen. Het ontcijferen van die vingerafdruk met de voorgestelde kaartaaanpak kan leiden tot betere materialen, schonere interfaces en slimmere processen, waardoor 2D-transistoren vooruitgang kunnen boeken van veelbelovende prototypes naar echt betrouwbare bouwstenen voor toekomstige elektronica.

Bronvermelding: Lv, Y.Z., Wu, Y.H., Cai, H.H. et al. Mapping diverse hysteresis dynamics in scaled MoS2 FETs using the universal method derived from TCAD modeling. npj 2D Mater Appl 10, 35 (2026). https://doi.org/10.1038/s41699-026-00671-8

Trefwoorden: 2D-transistoren, hysteresie, oxidefouten, apparaatstabiliteit, MoS2 FETs