Clear Sky Science · nl

3D LineExplore: een 3D-lijnverkenningsmethode voor geometrische routering op meerlaagse PCB's

Slimmere bedrading voor de printplaten in alles

In elke smartphone, laptop en auto verbergen zich tegenwoordig kleine koperen snelwegen die signalen tussen chips vervoeren. Nu elektronica meer onderdelen in minder ruimte propt, is het tekenen van deze microscopische “wegen” op printplaten (PCB's) een van de moeilijkste stappen in hardwareontwerp geworden. Dit artikel presenteert een nieuwe manier om die routes automatisch in drie dimensies te plannen, met belofte van snellere ontwerpen, minder fouten en betere prestaties voor de apparaten die we dagelijks gebruiken.

Waarom traditionele routering tegen grenzen aanloopt

De meeste automatische PCB-routers werken vandaag de dag met een schaakbordachtig raster: de plaat wordt opgedeeld in kleine vakjes en algoritmen zoals A* zoeken naar het goedkoopste pad van één pin naar een andere. Dat werkt, maar kent nadelen. Is het raster grof, dan zijn paden onnauwkeurig en kunnen ze ontwerprichtlijnen schenden. Is het raster heel fijn, dan explodeert de zoekruimte en wordt het pijnlijk langzaam, vooral bij meerlaagse bordontwerpen waarbij sporen via kleine doorgangen, zogenaamde via's, tussen lagen kunnen springen. Gridloze methoden vermijden het kunstmatige raster en werken direct met vormen, maar zijn tot nu toe grotendeels beperkt gebleven tot vlakke, tweedimensionale lay-outs en hebben moeite om echte 3D- en meerlaagse routering efficiënt aan te pakken.

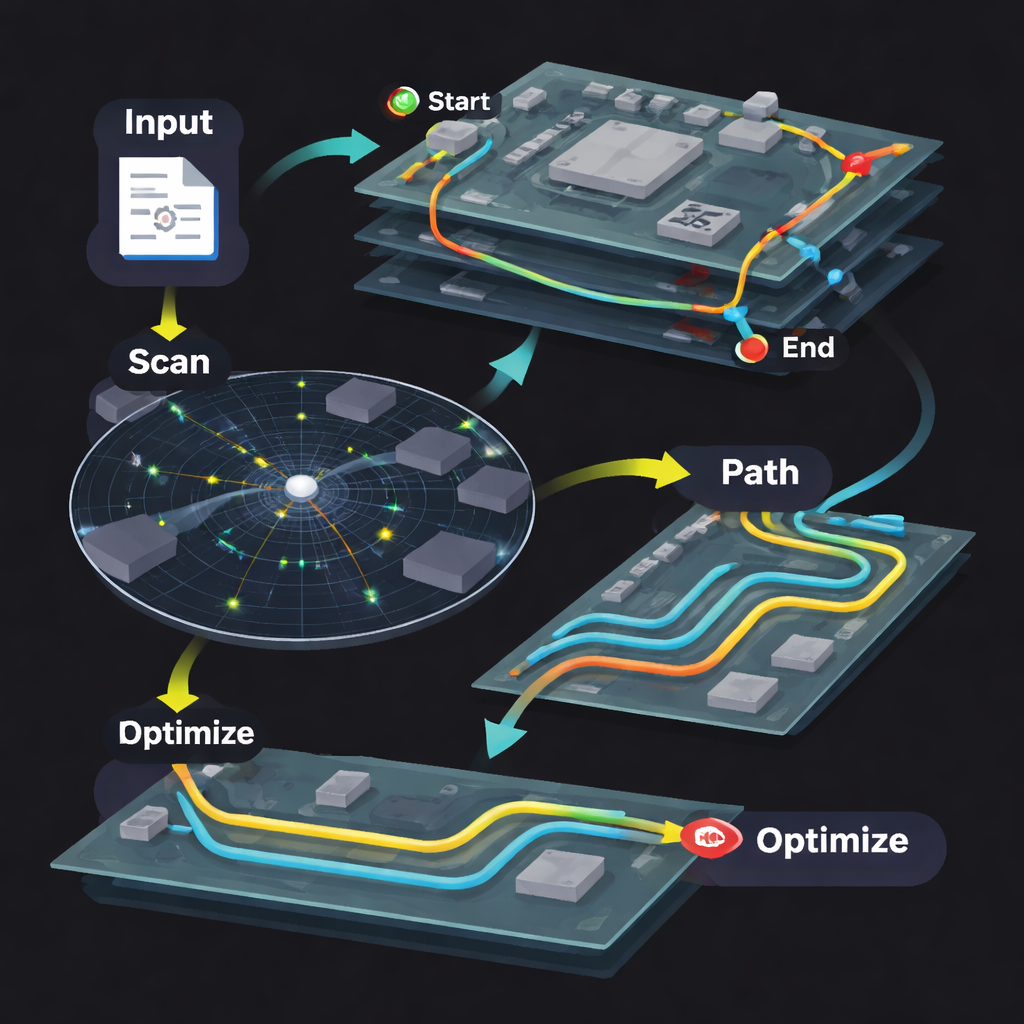

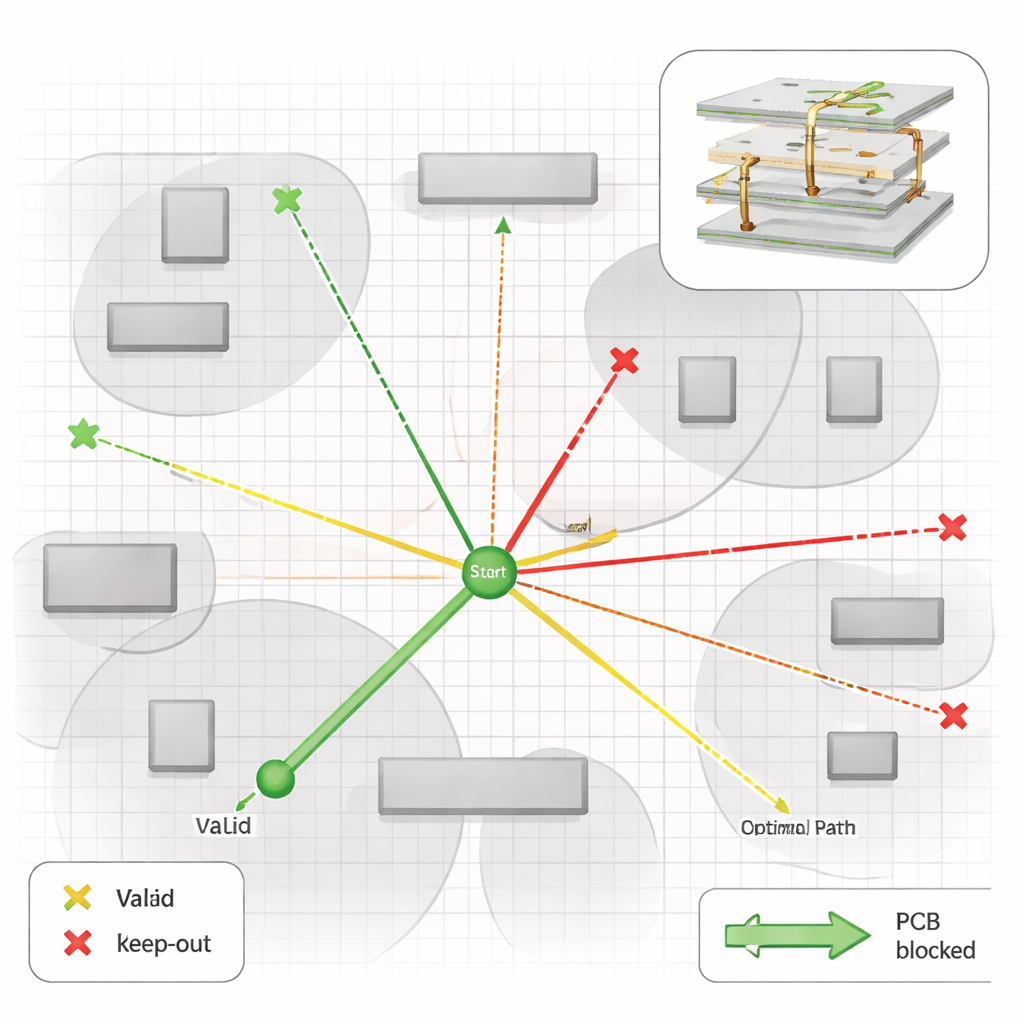

Een 3D-“radar” om veilige paden te vinden

De auteurs introduceren 3D LineExplore, een gridloze routeringsmethode die direct in continue ruimte over meerdere lagen werkt. De kern is een door “radar” geïnspireerd scan-algoritme. In plaats van elk rastervakje te controleren, kijkt de methode rond het huidige punt in een lokale omgeving, identificeert nabijgelegen obstakels zoals componenten en reeds geplaatste draden, en verzamelt belangrijke hoekpunten uit die vormen. Vanuit deze punten stelt het een compact aantal veelbelovende “verkenningspunten” voor waar een draad veilig langs zou kunnen lopen. Als de directe omgeving geen route biedt, wordt de scanradius vergroot, maar alleen wanneer dat nodig is. Deze selectieve verkenning houdt de zoekactie gefocust, voorkomt overbodige controles en breidt zich op natuurlijke wijze uit naar meerdere lagen door doelpunten tussen lagen te projecteren en speciale verkenningspunten toe te voegen die potentiële via-locaties vertegenwoordigen.

Kosten laten het beste pad bepalen

Zodra de verkenningspunten bekend zijn, kiest een tweede module het daadwerkelijke pad. Dit obstakel-ontwijkende heuristische padalgoritme werkt als een begeleide zoekactie: het weegt de reeds afgelegde afstand, de afstand naar elk volgend kandidaatpunt, de extra kosten van het boren van een via naar een andere laag en een rechtlijnige schatting van de resterende afstand naar de bestemming. Door deze factoren in één kostenfunctie en een prioriteitswachtrij te combineren, breidt het algoritme altijd de meest veelbelovende volgende stap uit. Achter de schermen bouwt dit een spaarzaam graafmodel van mogelijke bewegingen zonder ooit een volledig raster aan te leggen. Wanneer de doellijn bereikt is, wordt het pad gereconstrueerd door de opgeslagen voorgangerlinks terug naar het begin te volgen, resulterend in een complete 3D-route die om obstakels heen weeft en van laag wisselt alleen wanneer de extra kosten dat rechtvaardigen.

Complexe netten opruimen en lijnen verscherpen

In de praktijk verbinden PCB's zelden slechts één paar pinnen tegelijk. Veel netten koppelen drie of meer pinnen, wat gemakkelijk tot doodlopende wegen of verwarde routes leidt. 3D LineExplore pakt deze gevallen aan door een multi-pin net op te delen in een reeks dichtstbijzijnde-neighbour pinparen, deze één voor één te routeren en daarna eventuele mislukkingen te herstellen. Als een verbinding niet kan worden voltooid zoals gepland, zoekt het algoritme naar een alternatieve aansluiting op een nabijgelegen reeds verbonden pin, waardoor het net met minimale extra draad wordt hersteld. Nadat alle connectiviteit veilig is gesteld, verbetert een nabehandelingsstap de fysieke vorm van de draden. Veel hogesnelheidsontwerpen geven de voorkeur aan hoeken van ongeveer 135 graden in plaats van scherpe rechte hoeken, om fabricage te vergemakkelijken en elektrische reflecties te verminderen. De auteurs introduceren een geometrische “parallellogram”-aanpassing die polyline-segmenten hervormt tot soepelere paden met 135-graden beperkingen, terwijl alle verbindingen behouden blijven en nieuwe botsingen worden vermeden.

De nieuwe methode aan de tand voelen

Het team evalueerde 3D LineExplore op elf openbare benchmarkborden variërend van eenvoudig tot complex, en vergeleek het met zowel commerciële als academische tools, waaronder FreeRouting, ELECTRA, DeepPCB en een geoptimaliseerd 3D A*-algoritme. Over deze gevallen wist de nieuwe methode ongeveer 98% van de vereiste pinparen succesvol te verbinden, waarmee hij gelijke tred hield met of beter presteerde dan gevestigde routers. Opvallender was dat de totale draadlengte gemiddeld korter was — ongeveer 15% minder dan één toonaangevend commercieel gereedschap — wat helpt signaalvertraging en vermogensverlies te verminderen. Hoewel het soms meer via's gebruikte om congestie te omzeilen, verbeterde deze afweging het ruimtegebruik en verminderde de druk op individuele lagen. Qua snelheid maakte het eenmalige ontwerp, gecombineerd met adaptieve lokale scanning, het mogelijk om de meeste ontwerpen in seconden te voltooien, en in sommige gevallen verkortte de adaptieve zoekactie de routeringstijd met meer dan 90% vergeleken met een brute-force zoektocht over het hele bord, terwijl de draadlengte slechts licht toenam.

Wat dit betekent voor toekomstige elektronica

In eenvoudige bewoordingen biedt 3D LineExplore PCB-ontwerpers een manier om dichtbevolkte, meerlaagse borden te routeren zoals een ervaren mens dat zou doen: door lokaal rond te kijken, alleen de nuttigste kandidaatroutes te kiezen en korte paden af te wegen tegen de kosten van laagwissels. Het vermijdt de zware overhead van fijne rasters terwijl het toch strikte ontwerprichtlijnen respecteert en gladde, maakbare sporen oplevert. Naarmate elektronica in complexiteit toeneemt en in omvang krimpt, kunnen benaderingen als deze — vooral in combinatie met toekomstige machine-learning-gestuurde aanwijzingen — automatisch routeren zowel sneller als betrouwbaarder maken, waardoor nieuwe generaties apparaten eerder op de markt komen en efficiënter werken.

Bronvermelding: Sun, N., Zhang, J., Xu, N. et al. 3D LineExplore: a 3D line exploration method for multi-layer PCB geometric routing. Sci Rep 16, 6588 (2026). https://doi.org/10.1038/s41598-026-36925-0

Trefwoorden: PCB-routering, meerlaagse printplaten, gridloos algoritme, elektronische ontwerpautomatisering, 3D-padplanning