Clear Sky Science · nl

Richting de transformatie van MATLAB-modellen naar op FPGA gebaseerde hardwareversnellers

Labalgoritmen omzetten naar echte apparaten

Veel moderne medische en technische doorbraken beginnen als software geschreven door onderzoekers, vaak in gebruiksvriendelijke tools zoals MATLAB. Maar wanneer diezelfde algoritmen in realtime moeten draaien—bijvoorbeeld om gevaarlijke hartritmestoornissen op een elektrocardiogram (ECG) te detecteren—hebben ze de snelheid en efficiëntie van speciale hardware nodig. Dit artikel toont hoe je op betrouwbare wijze een complex neurale-netwerk voor hartslagdetectie van MATLAB naar een gespecialiseerd chiptype, een FPGA, brengt zonder de nauwkeurigheid te verliezen waarop artsen en ingenieurs vertrouwen.

Waarom code herschrijven voor chips zo lastig is

FPGAs (Field-Programmable Gate Arrays) zijn configureerbare chips die gewaardeerd worden om hun snelheid en lage energieverbruik. Traditioneel vereiste het programmeren ervan hardwaregerichte talen zoals VHDL of Verilog, die ver afstaan van de wiskunde en signaalverwerkingscode op hoog niveau die wetenschappers in MATLAB schrijven. Nieuwe tools kunnen algoritmen automatisch naar hardwarebeschrijvingen omzetten, maar ze vragen vaak handmatige aanpassingen en richten zich vooral op prestaties: hoe snel de chip draait en hoeveel middelen hij gebruikt. Wat ontbrak, is een duidelijke manier om te bewijzen dat de hardware precies hetzelfde doet als de originele software—laag voor laag, getal voor getal.

Een stapsgewijze check voor elke netwerklayer

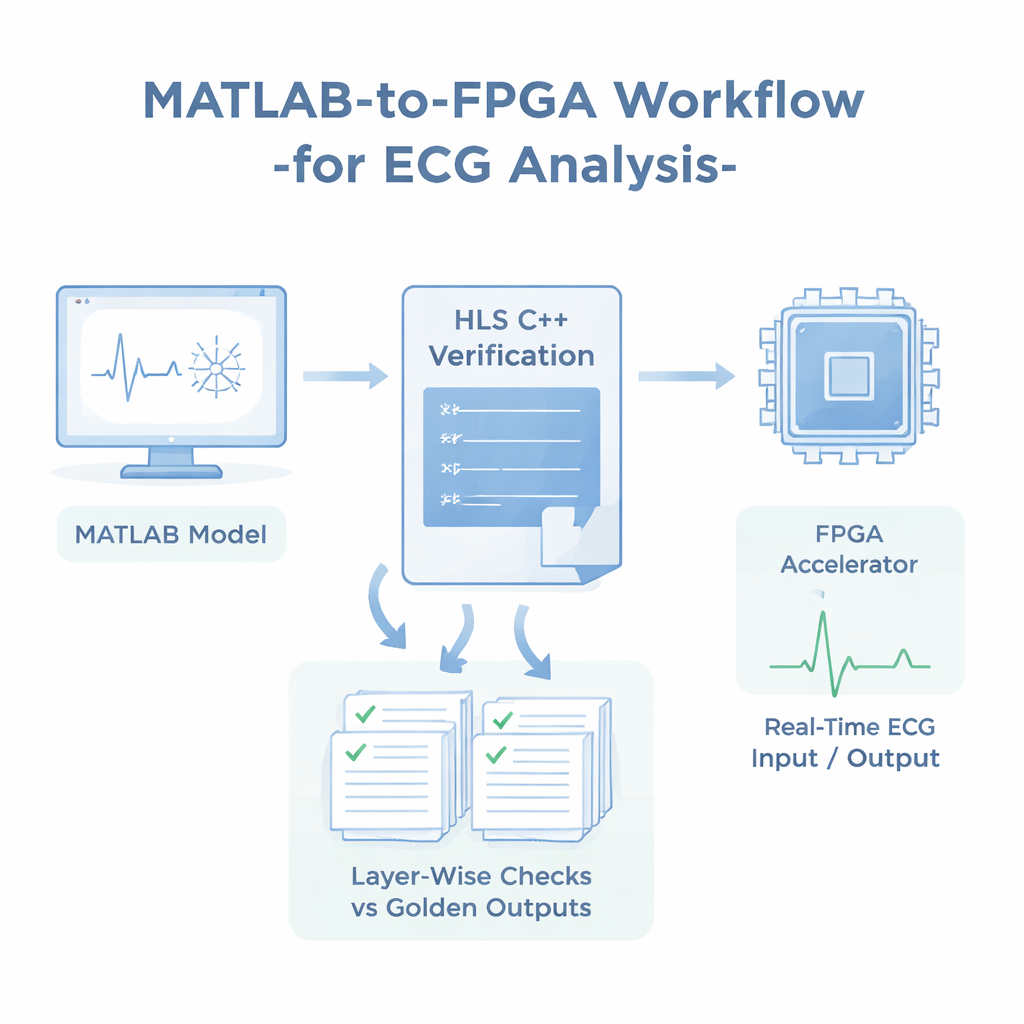

De auteur vult deze leemte door een verificatiegericht werkproces voor te stellen voor een eendimensionaal convolutioneel neuraal netwerk dat hartslagen classificeert uit de bekende MIT-BIH Arrhythmia Database. Het netwerk, gebouwd in MATLAB, bekijkt korte fragmenten van ECG-data en plaatst ze in één van vijf hartslagtypen, inclusief normale en verschillende abnormale ritmes. Drie versies van het netwerk, met verschillende dieptes, worden op dezelfde data getraind. Na het trainen worden de gewichten, biases en de outputs van elke laag op testsignalen bewaard als "golden outputs"—een nauwkeurig numeriek verslag van hoe het MATLAB-model zich gedraagt.

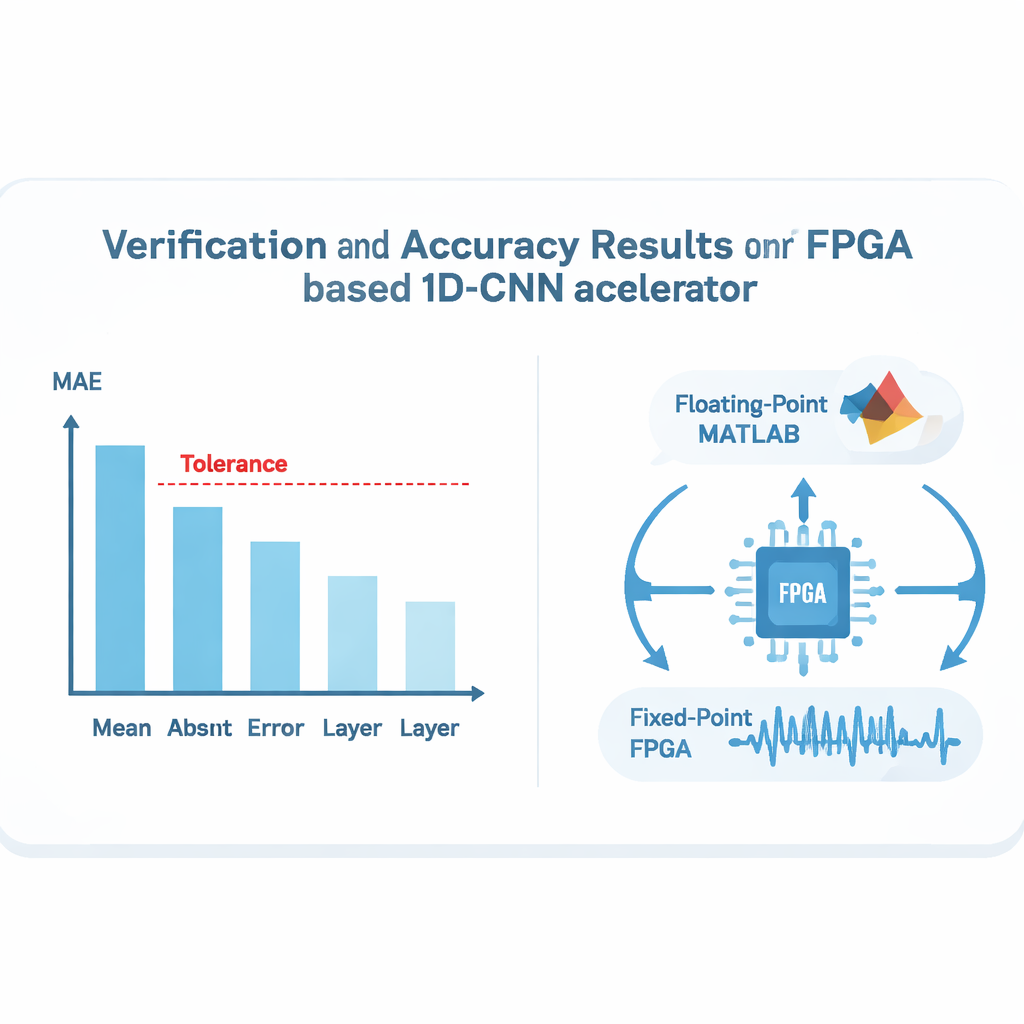

Van MATLAB naar C++ naar FPGA, met getallen gevolgd

In plaats van op een automatische "converteer"-knop te drukken, wordt het netwerk handmatig opnieuw geïmplementeerd in C++, volgens dezelfde data-indeling en wiskundige stappen als in MATLAB. Deze C++-code wordt vervolgens met een high-level synthesis-tool gebruikt om hardware te genereren die draait op een PYNQ-Z1 FPGA-bord. In elke fase—MATLAB, C++ en FPGA—worden de laagoutputs vergeleken met de opgeslagen golden outputs met een eenvoudige meetlat: de mean absolute error, die het gemiddelde numerieke verschil tussen twee resultaatsets meet. De studie hanteert een strikte tolerantiedrempel: alle lagen moeten onder een fout van 1,5×10⁻³ blijven. Over duizenden ECG-monsters haalt iedere geteste laag dit doel, en de uiteindelijke classificatienauwkeurigheid blijft vrijwel onveranderd: ongeveer 98,3–98,4% in MATLAB en C++, en slechts circa 0,2 procentpunt lager op de FPGA, een verschil dat overeenkomt met de verwachte effecten van het gebruik van kortere, fixed-point getallen in hardware.

De hardware versnellen zonder de wiskunde te breken

Zodra de correctheid is gegarandeerd, wordt het ontwerp voor snelheid geoptimaliseerd. De meest veeleisende delen van het netwerk—de convolutionele lagen—worden op de programmeerbare logica van de FPGA gezet, waarbij fixed-point rekenkunde voor efficiëntie wordt gebruikt, terwijl lichtere taken zoals de laatste softmax-berekening op de ingebouwde processor van de chip met normale floating-point getallen blijven draaien. Technieken zoals loop-pipelining, loop-unrolling en zorgvuldig opsplitsen van geheugen in parallelle banken maken het mogelijk dat verschillende delen van de berekening en datatransfers gelijktijdig verlopen. Een geoptimaliseerde versie van de hardware verwerkt een hartslagvenster in ongeveer 1,7 milliseconde en past comfortabel binnen de middelen- en vermogensgrenzen van de FPGA, terwijl de laaggewijze numerieke werking van het oorspronkelijke MATLAB-model behouden blijft.

Wat dit betekent voor toekomstige slimme apparaten

Voor niet-specialisten is de kernboodschap dat het nu mogelijk is niet alleen een geavanceerde op MATLAB gebaseerde hartritmclassifier op een laagvermogen chip te versnellen, maar ook te bewijzen dat de interne werking van de chip nauw overeenkomt met het vertrouwde softwaremodel in elke laag. In plaats van snelheid na te jagen ten koste van betrouwbaarheid, bouwt deze aanpak een duidelijke audittrail van floating-point MATLAB-code naar fixed-point FPGA-hardware. Hetzelfde verificatierecept—golden outputs opslaan, laaggewijze fouten vergelijken met een strikte drempel en de uiteindelijke nauwkeurigheid controleren—kan worden toegepast op andere eendimensionale neurale netwerken in domeinen zoals draagbare gezondheidsmonitors, industriële sensoren en slimme voertuigen, en helpt zo te waarborgen dat wanneer algoritmen het lab verlaten en in apparaten worden ingebouwd, hun beslissingen betrouwbaar blijven.

Bronvermelding: Bal, S. Towards the transformation of MATLAB models into FPGA-Based hardware accelerators. Sci Rep 16, 5027 (2026). https://doi.org/10.1038/s41598-026-36033-z

Trefwoorden: FPGA-versnellers, MATLAB neurale netwerken, ECG aritmieclassificatie, hardwareverificatie, fixed-point deep learning