Clear Sky Science · ja

アナログ・インメモリ演算のためのスケーラブルで堅牢なマルチビット・スピントロニクス・シナプス

日常のAIにとって「賢い」メモリが重要な理由

音声アシスタントから写真アプリまで、現代の人工知能はディープニューラルネットワークに大きく依存しており、意思決定のために数百万もの小さな数値「重み」を扱います。これらの重みをメモリとプロセッサ間で往復させるコストは、演算自体よりはるかに大きなエネルギーを消費します。本論文では、これらの重みを格納するだけでなく、データのある場所で直接計算の一部を実行できる新しいタイプの磁気メモリセルを検討し、より高速で効率的なAIハードウェアを実現する可能性を示します。

脳に似た計算をメモリチップに取り込む

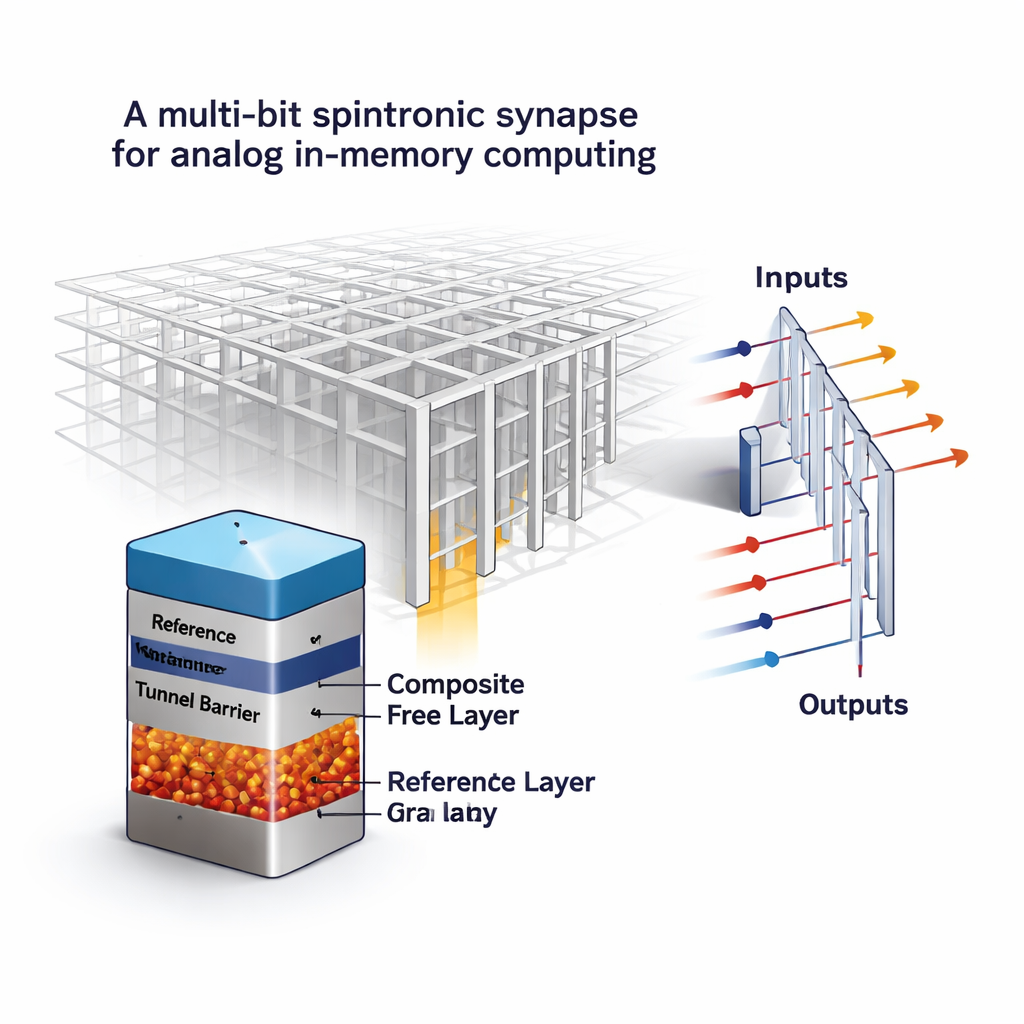

今日のコンピュータは、データがメモリと別のプロセッサの間を絶えず行き交う古典的な「フォン・ノイマン」構成に従います。行列–ベクトル積という大量の演算を要するニューラルネットワークは、このボトルネックの影響を強く受けます。有望な代替策はインメモリ演算で、クロスバー配列と呼ばれる大きな格子状のメモリセル群がネットワークの重みを保持し、同時に入力電圧を出力電流に変換して演算を実行します。この役割のために多くの実験的メモリデバイスが試されてきましたが、多くはノイズの多さや値のドリフトに悩まされ、各セルが単に0か1以上の情報を表す必要がある場合には問題となります。

磁気メモリをオン/オフから「アナログ」へ変える

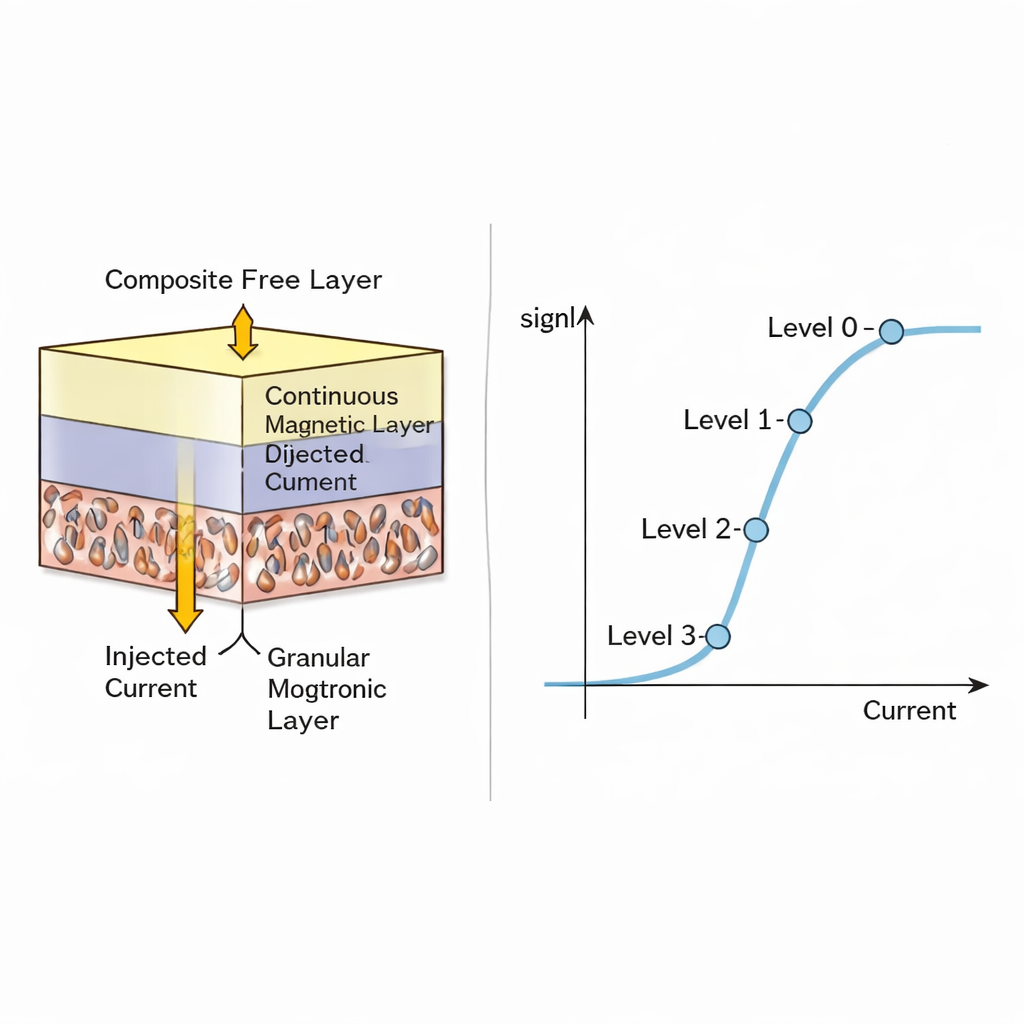

著者らは、速度、耐久性、標準的なチッププロセスとの互換性で評価される不揮発性技術である磁気ランダムアクセスメモリ(MRAM)を基盤にしています。従来のMRAMセルは磁気トンネル接合で、絶縁バリアを挟んで並ぶ2つの磁性層からなります。層が同方向か逆方向かに応じて電気抵抗が低いか高いかになり、単一ビットを符号化します。ここでの重要な工夫は、「自由」磁性層を一度に全体が反転する均一な塊ではなく設計することです。代わりに、新しい設計は非常に薄い連続膜を、より厚く多くの微小な磁性粒子から成る粒状磁性層の上に組み合わせます。各粒子はわずかに異なる電流で反転できるため、全体の抵抗は「低」と「高」のみに限られず、いくつかの中間で安定したレベルに落ち着くことができます。

磁性の「階調」はどれだけ有用か?

磁気ダイナミクスの詳細なコンピュータモデルを用いて、研究チームはこの複合層にスピン偏極電流を注入すると、粒子ごとに段階的にスイッチングが進むことを示します。電流を掃引すると、平均磁化とそれに伴う抵抗は滑らかなS字型の曲線を描き、ほぼ連続的なアナログ状態を可能にします。次に著者らは、セル間の製造ばらつきや書き込みごとの熱ゆらぎがこれらのレベルに与える影響を検討します。中間状態はややノイジーになるものの、極端な状態(完全に一方向または他方向にスイッチした状態)は非常に確実で堅牢であることがわかりました。現実的なサイズのデバイス(辺長約50〜75ナノメートル)では、過剰な誤差なしに4つの確実に識別できる抵抗レベル、すなわちセルあたり2ビットが実用的であると結論づけています。

単一セルからAIアクセラレータ全体へ

実用的にするには、このマルチレベルMRAMを正確に読み取り、完全な計算システムに統合する必要があります。著者らは、各セルの4つの抵抗レベルを区別するために高速の「フラッシュ」型アナログ–デジタル変換器を用いるセンサ回路を設計・シミュレートしています。最高と最低の導電状態のコントラストが読み出し速度、エネルギー消費、センサ回路の大きさにどのように影響するかを調べ、コントラストが良いほど読み出しが速くエネルギー効率が高くなることを示しました。次に、セルあたり2ビットのMRAMモデルを、CIFAR-10画像データセット上でResNet-18ニューラルネットワークを動かすインメモリアクセラレータのシミュレーションに組み込みます。標準的な1ビットMRAMセルを用いるベースラインと比べて、マルチビット版はおおむね記憶密度を倍増させ、必要なクロスバータイル数を半分に削減します。これによりチップ面積、エネルギー、レイテンシが最大で約1.8倍削減され、エネルギー–遅延の複合指標では3倍以上の改善が見られ、ネットワークの認識精度はほぼ維持されます。

他のメモリ案との比較

本研究は、抵抗変化メモリ(ReRAM)や相変化メモリ(PCM)、ドメイン壁やスキルミオンの移動に依拠する他の磁気概念などの競合技術とも比較しています。それらの代替案もアナログに近い挙動を示すことがありますが、より大きなデバイスや特殊な形状を必要としたり、予測しにくい傾向があります。対照的に、粒状MRAMセルは主流MRAMの製造のしやすさや耐久性を保ちつつ、追加の記憶レベルを得られます。システムレベルのテストでは、現実的な変動下でもMRAMベースのシナプスは、よりばらつきの大きい抵抗性メモリを用いた設計よりニューラルネットワークの精度を高く維持できることが示唆されており、特にネットワークを疎にしてさらなるエネルギー節約を図る場合に有利です。

将来の日常的なAIにとっての意味

端的に言えば、著者らは実績ある磁気メモリ技術に対し、ゼロと一だけでなく小さなアナログ重み値をコンパクトなセル内に直接格納させる方法を示しました。多くの微小な粒子に磁気挙動を分散させる層状構造を精密に設計することで、実世界のAIタスクに耐えうる複数の安定した抵抗レベルを得ています。これらのセルが大規模な配列に並べられ、適切な検出回路と組み合わされれば、ディープラーニングのコア演算を実行しつつデータ移動を劇的に削減できます。ハードウェアとして実現されれば、このようなマルチビットのスピントロニクス・シナプスは、データセンター、スマートフォン、組み込みセンサーなど将来のAIシステムを、精度を損なうことなくより高速でエネルギー効率の高いものにする可能性があります。

引用: Gupte, K.K., Mugdho, S.S., Huang, C. et al. Scalable and robust multi-bit spintronic synapses for analog in-memory computing. npj Unconv. Comput. 3, 8 (2026). https://doi.org/10.1038/s44335-026-00055-7

キーワード: インメモリ演算, スピントロニクスメモリ, MRAM, ニューロモルフィック・ハードウェア, ディープニューラルネットワーク