Clear Sky Science · ja

酸化物半導体ゲインセル埋め込みメモリ:次世代オンチップメモリのための材料と統合戦略

なぜより高速で賢いメモリが重要か

スマートフォン、ノートパソコン、データセンターはますます高性能になっていますが、隠れた速度の制約が残っています。それはプロセッサとメモリ間でデータを移動することです。本稿は、この「メモリの壁」を緩和し、人工知能、クラウドコンピューティング、日常アプリなどの処理をより高速かつ省エネルギーにできる可能性のある新しい種類のオンチップメモリを探ります。メモリセルの構造や材料を再考することで、研究者たちはプロセッサ近傍により多くのデータを詰め込みつつ、消費電力と発熱を抑えることを目指しています。

現代コンピュータ内部のボトルネック

何十年にもわたり、プロセッサの性能はデータを供給する主記憶装置よりもはるかに速く向上してきました。この不均衡は「メモリの壁」として知られ、高速チップが情報を待ってアイドル状態になる原因となります。設計者はプロセッサ上に複数層のキャッシュメモリを配置してこのボトルネックを和らげようとしてきました。現在のキャッシュはSRAMというメモリを使っていますが、これは非常に高速である一方、1ビットあたり6つのトランジスタが必要なため面積と消費電力が大きくなります。容量を増やすためにSRAMチップを立体的に積み重ねたり、チップ上に組み込みDRAMを追加したりしますが、従来のDRAMは極微小化に際して製造が難しい小さなコンデンサに依存しており、標準のロジック回路と統合するのも困難です。

異なるタイプのメモリセル

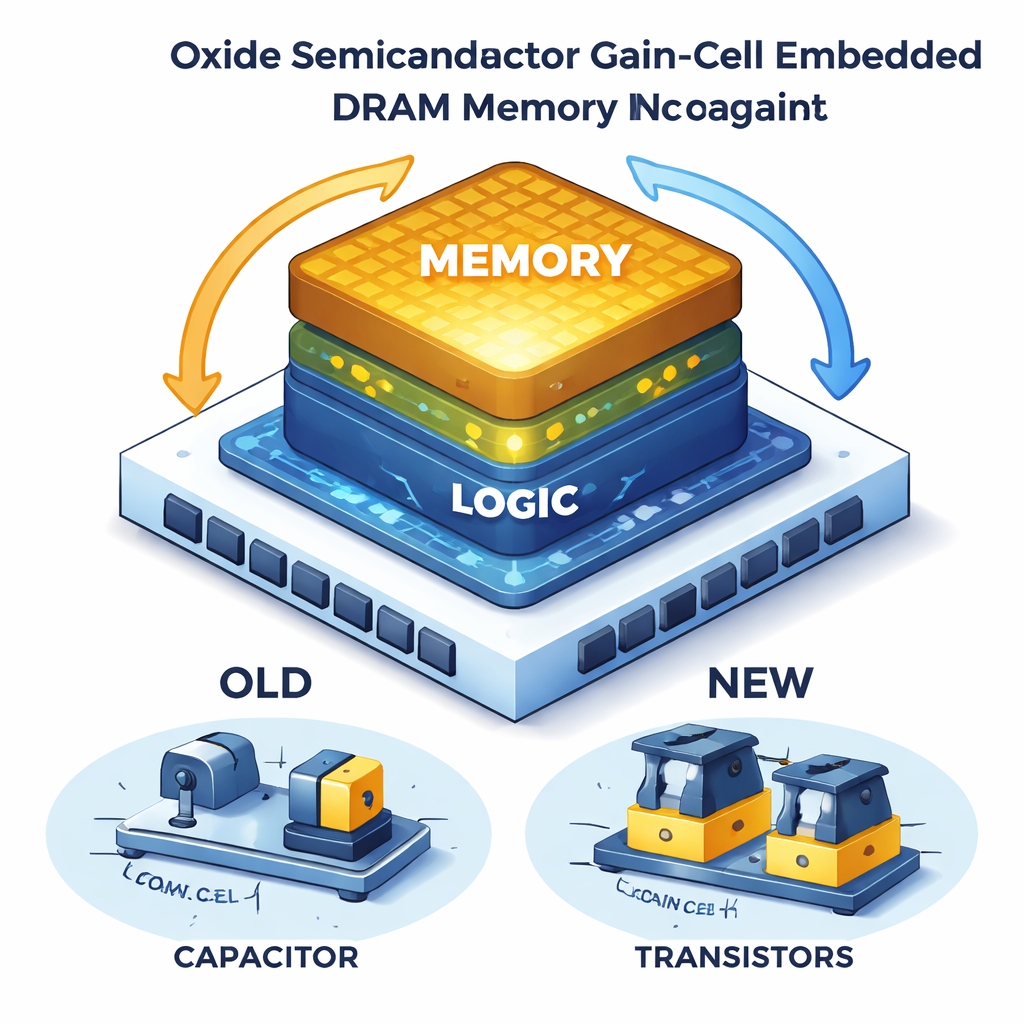

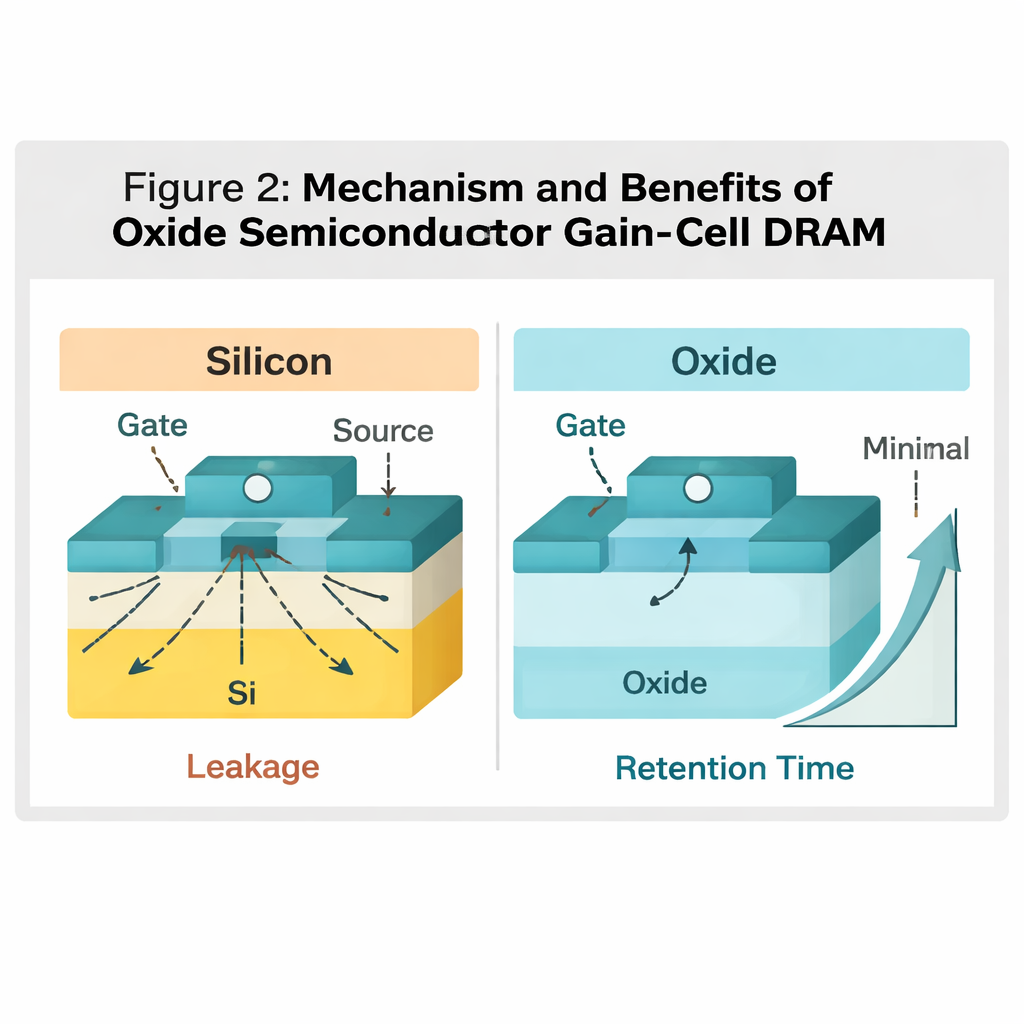

この論文はゲインセル埋め込みDRAM(GC-eDRAM)と呼ばれる代替手法に焦点を当てています。電荷を保持するために別個のコンデンサを使う代わりに、ゲインセルはトランジスタのみでデータを保持し、構造を簡素化して標準的なチップ製造プロセスとの相性を良くします。この設計はロジック回路の上に立体的に積み上げる「メモリ・オン・ロジック」配置に自然に適合し、高密度を実現する可能性があります。もう一つの利点は「非破壊読み出し」特性で、読み出しが直ちに値を消耗しないためリフレッシュ頻度を下げられる点です。ただし、従来のシリコン版では保持電荷がミリ秒未満で漏れてしまうため、頻繁なリフレッシュがエネルギーを浪費し、実用性を制限していました。

酸化物半導体:静かで冷たいスイッチ

ゲインセルのリークを克服するために、著者らは酸化物半導体——インジウム・ガリウム・亜鉛酸化物(IGZO)などの化合物——をトランジスタのチャネル材料として注目しています。これらの酸化物は広いバンドギャップを有し、トランジスタがオフのときの不要電流を強く抑制します。実験では測定器の限界に近い極めて微小なオフ電流が報告されており、プロトタイプのゲインセルはシリコン設計の千分の一秒に比べて数秒、数時間、あるいはそれ以上の一日単位でデータを保持するものもあります。重要な点は、これらの酸化物が比較的低温で堆積可能であり、チップ製造のバックエンド工程と互換性があるため、既存のシリコンロジックを損なうことなくその上に高密度のメモリ層を直接構築できることです。

上方向への構築:3Dスタックと微小トランジスタ

チップがさらに微細化するにつれて、単にトランジスタを小さくすることはチャネル制御の悪化やリーク増加といった新たな問題を引き起こします。論文はゲートをチャネルの周囲に巻き付ける(ゲート・オール・アラウンドやチャネル・オール・アラウンド)先進的なトランジスタ形状をレビューしており、これによりナノメートルサイズでも厳密な制御が維持されます。これらのマルチゲート構造に酸化物半導体を用いることで、研究者は非常に短いチャネル、極めて低いリーク、強いデータ保持性を示しつつ複数のメモリ層を垂直に積み重ねることに成功しています。いくつかの実験的設計はすでに今日の最良DRAMセルの面積効率に達するか、それを上回っており、将来のチップがプロセッサコアの直上に非常に小さなフットプリントで膨大なメモリ容量を搭載できることを示唆しています。

実験室の材料から信頼できる製品へ

これら有望なデバイスを実用的なメモリに転換するには、綿密な材料工学が必要です。記事では酸化物中の金属組成の調整、酸素含有量の制御、膜の結晶化によって高速性と長期安定性を両立させる方法を説明しています。また、欠陥、芳香(注:原文の“hydrogen contamination”は水素汚染)、および酸化物と絶縁層の繊細な界面を管理して、デバイスが加熱や長時間動作の下でも安定に保たれる方法についても扱います。最後に、接触抵抗が新材料の利点を相殺しないように金属接続を設計する工程についても論じています。これらの戦略を組み合わせることで、大規模製造に耐えるだけの高密度で信頼性のあるメモリを実現することを目指しています。

日常のコンピューティングにとっての意義

著者らは、酸化物半導体ゲインセルメモリが将来のチップ設計を変える可能性があると結論づけています。小さくリークの少ないメモリセルとロジック回路上の3Dスタッキングを組み合わせることで、プロセッサの隣接により多くの高速メモリを配置しつつ消費電力を抑えられるようになります。これによりメモリの壁が緩和され、AIアクセラレータからクラウドサーバ、個人用デバイスに至るまで、すべての処理がより高速かつ効率的に動作することが期待されます。信頼性、製造均一性、チップ全体の統合といった課題は残りますが、本稿で概説された研究は、よりコンパクトで高性能かつ省エネルギーなコンピューティングシステムへの明確な道筋を示しています。

引用: Chung, S.W., Yoon, S.H. & Jeong, J.K. Oxide semiconductor gain cell-embedded memory: materials and integration strategies for next generation on-chip memory. Commun Eng 5, 39 (2026). https://doi.org/10.1038/s44172-026-00616-5

キーワード: オンチップメモリ, 酸化物半導体, DRAMのスケーリング, 3D集積回路, AIハードウェア