Clear Sky Science · ja

TCADモデリングから導かれた普遍的手法を用いたスケール化MoS2 FETにおける多様なヒステリシス挙動のマッピング

なぜ小さなスイッチに信頼性が必要なのか

現代のエレクトロニクスはますます微細なトランジスタへと向かっており、二次元(2D)材料としての二硫化モリブデン(MoS2)は将来のチップの有力候補です。しかし、これらのスイッチが小さくなるにつれて挙動が不安定になりやすく、同じデバイスでも直前の使用状況によって応答が変わることがあります。この記憶のような効果はヒステリシスと呼ばれ、多くの場合は小さな厄介事として片付けられます。本研究では、ヒステリシスが実は先端トランジスタ内部の隠れた欠陥に関する豊富な情報を隠しており、それを読み取るための普遍的な方法を提示していることを示します。

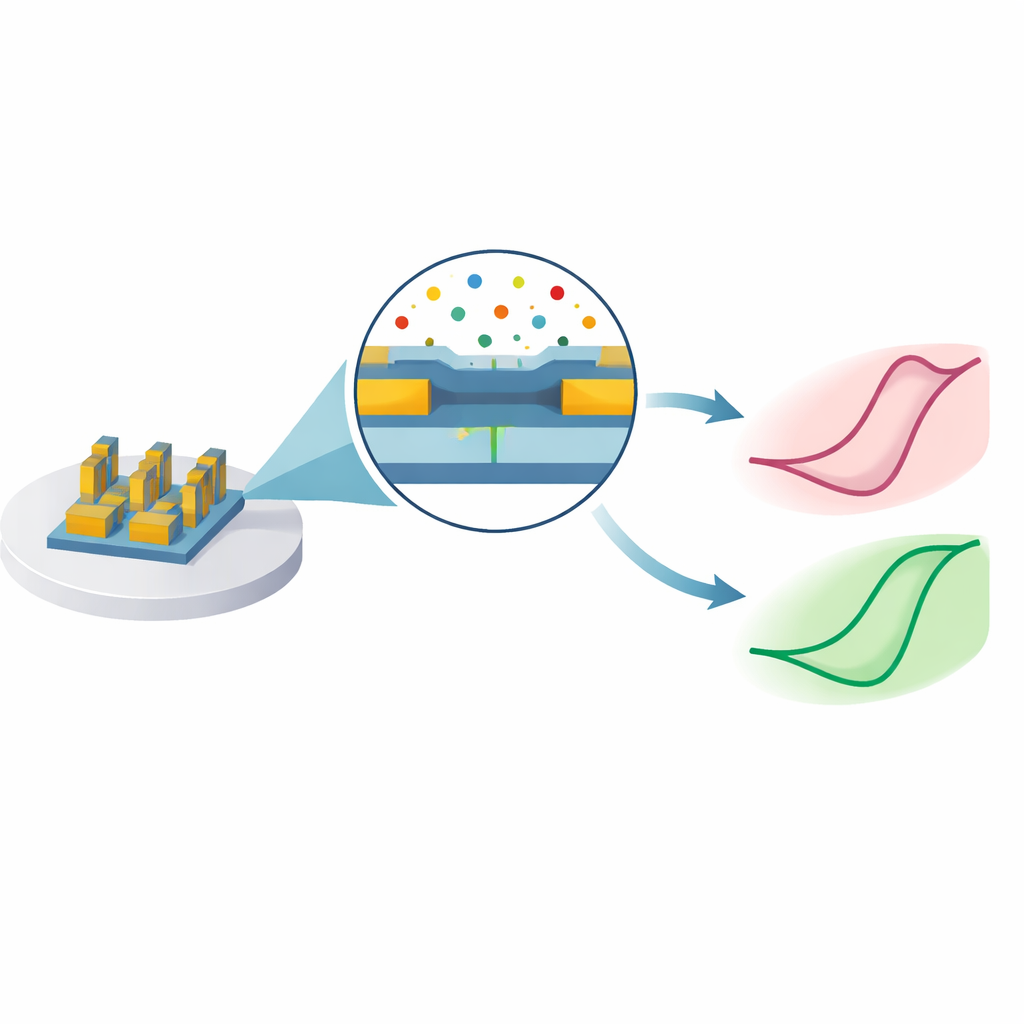

次世代トランジスタの構造

将来の2D電界効果トランジスタは、電流が流れるチャネルとして超薄膜のMoS2層を用い、その上にハフニウム酸化物(HfO2)などの非常に薄い絶縁酸化膜を被せ、さらに金属ゲートを配置します。デバイスを小型化し続けるためには、この酸化膜が電気的にはほぼ1ナノメートル級である必要があり、酸化膜内の個々の欠陥がチャネルに強く影響を与え得ます。これらの欠陥は一時的に電荷を捕獲・放出する小さなトラップとして振る舞います。欠陥は酸化膜の異なる深さに存在しチャネルやゲートと相互作用するため、欠陥群の集合的な挙動はトランジスタを微妙に安定化または不安定化させます。2Dトランジスタが現在のシリコン技術と競合するためには、この欠陥分布を理解することが不可欠です。

なぜトランジスタは過去を記憶するのか

エンジニアがゲート電圧を上げ下げして電流を記録すると、しばしば前進スイープと後退スイープが一致しないことが見られます。これがヒステリシスです。従来、研究者は単一の動作点で二つの曲線間の距離を測りそれをヒステリシス幅と呼び、「小さい」または「無視できる」と結論づけることが多いです。著者らは、この慣習は特にスケール化されたデバイスでは誤解を招くと主張します。異なる欠陥群が逆の影響を与えることがあるためです。測定速度や動作電流によって、同じトランジスタが通常の時計回りのループ、逆向きの反時計回りループ、その間を切り替える挙動、あるいは相反する効果が打ち消し合ってほとんどヒステリシスが見えなくなる場合さえあります。

曲線に隠れた普遍的マップ

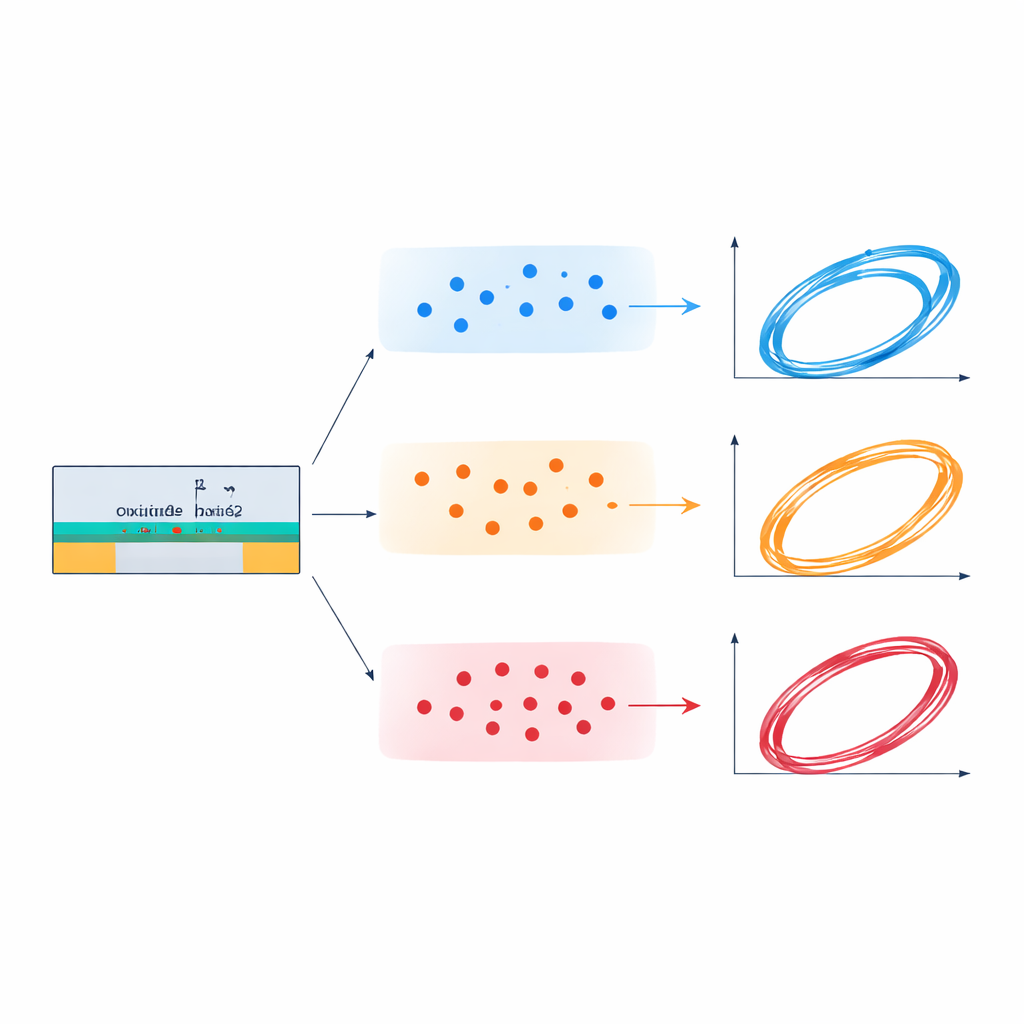

この複雑さを解きほぐすため、研究チームは酸化膜内の異なる深さに慎重に制御された欠陥群を持つナノスケールMoS2トランジスタの詳細なコンピュータシミュレーション(TCAD)を用います。次に彼らは普遍的なヒステリシスマッピング手法を提案します。単一の数値を抽出する代わりに、オフ状態の直上からオン状態近傍までの広い電流範囲と、非常に広いオーダーにわたるスイープ時間を横断してヒステリシス幅を走査します。これにより、各電流で測定速度に対するヒステリシスの変化を示す何千もの曲線が得られます。そこから、すべての可能な挙動を包む上限および下限の「普遍的ヒステリシス関数」を定義します。これらの包絡線は、どの種類の欠陥が活性化しているか、主にチャネルと相互作用するかトップゲートと相互作用するか、そして時計回りか反時計回りかを明確に示します。

高速ループと長期ドリフトの関連付け

ヒステリシスを引き起こす同じ欠陥は、長時間のストレス下でトランジスタ挙動に緩慢なドリフトを生じさせる、バイアス温度不安定性(BTI)として知られる問題も駆動します。標準的なストレス・回復実験をシミュレートすることで、著者らはヒステリシスマップの特徴と、最初に負のシフトを示し後に正の方向へ緩和するような異常なBTI署名とを結び付けます。チャネル近傍のトラップは遅くほぼ永続的なシフトを引き起こし、ゲート寄りのトラップはより速く主に可逆的な変化をもたらす傾向があることを示しています。この手法はシミュレーションしたMoS2デバイスだけでなく、研究用クリーンルームや試作ラインで作製された実測のMoS2やWSe2トランジスタのデータにも適用でき、酸化膜中のイオン移動が電荷捕獲に関与するケースも扱えます。

複雑なデータから実践的な指針へ

乱雑なヒステリシスループを標準化されたマップに変換することで、本研究は新興トランジスタ技術の強力な診断手法を提供します。この方法は実験データセットに直接適用でき、高度なシミュレーションツールへのアクセスを必ずしも必要としないため、広範なラボで利用可能です。エンジニアへの重要なメッセージは、ヒステリシスは単に最小化すべき欠陥ではなく、潜在的な信頼性問題の指紋であるということです。提案されたマッピング法でその指紋を解読することが、より良い材料、クリーンな界面、賢いプロセス設計を導き、2Dトランジスタが有望な試作段階から将来のエレクトロニクスの真に信頼できる構成要素へと進展する手助けになります。

引用: Lv, Y.Z., Wu, Y.H., Cai, H.H. et al. Mapping diverse hysteresis dynamics in scaled MoS2 FETs using the universal method derived from TCAD modeling. npj 2D Mater Appl 10, 35 (2026). https://doi.org/10.1038/s41699-026-00671-8

キーワード: 2次元トランジスタ, ヒステリシス, 酸化膜欠陥, デバイス信頼性, MoS2 FET