Clear Sky Science · ja

MATLABモデルをFPGAベースのハードウェアアクセラレータへ変換するために

研究室のアルゴリズムを現実の機器へ

多くの現代の医療や工学のブレイクスルーは、研究者がMATLABのような扱いやすいツールで書いたソフトウェアとして始まります。しかし、心電図(ECG)から危険な心拍リズムの異常をリアルタイムに検出するような用途では、同じアルゴリズムにカスタムハードウェアの速度と効率が求められます。本稿は、医師やエンジニアが頼りにする精度を損なうことなく、複雑な心拍検出ニューラルネットワークをMATLABからFPGAと呼ばれる専用チップへ確実に移行する方法を示します。

チップ向けにコードを書き直すのが難しい理由

FPGA(Field-Programmable Gate Array)は再構成可能なチップで、高速性と低消費電力が評価されています。従来はVHDLやVerilogのようなハードウェア寄りの言語での記述が必要で、科学者がMATLABで書く高水準の数学や信号処理コードとは大きく隔たっています。最近のツールはアルゴリズムを自動でハードウェア記述に変換できますが、手作業での調整が必要になりがちで、主に性能(チップの動作速度や資源使用量)に注目しがちです。欠けていたのは、ハードウェアが元のソフトウェアと「まさに同じ」動作を層ごと、数値ごとに証明する明確な方法でした。

各層ごとのステップバイステップ検証

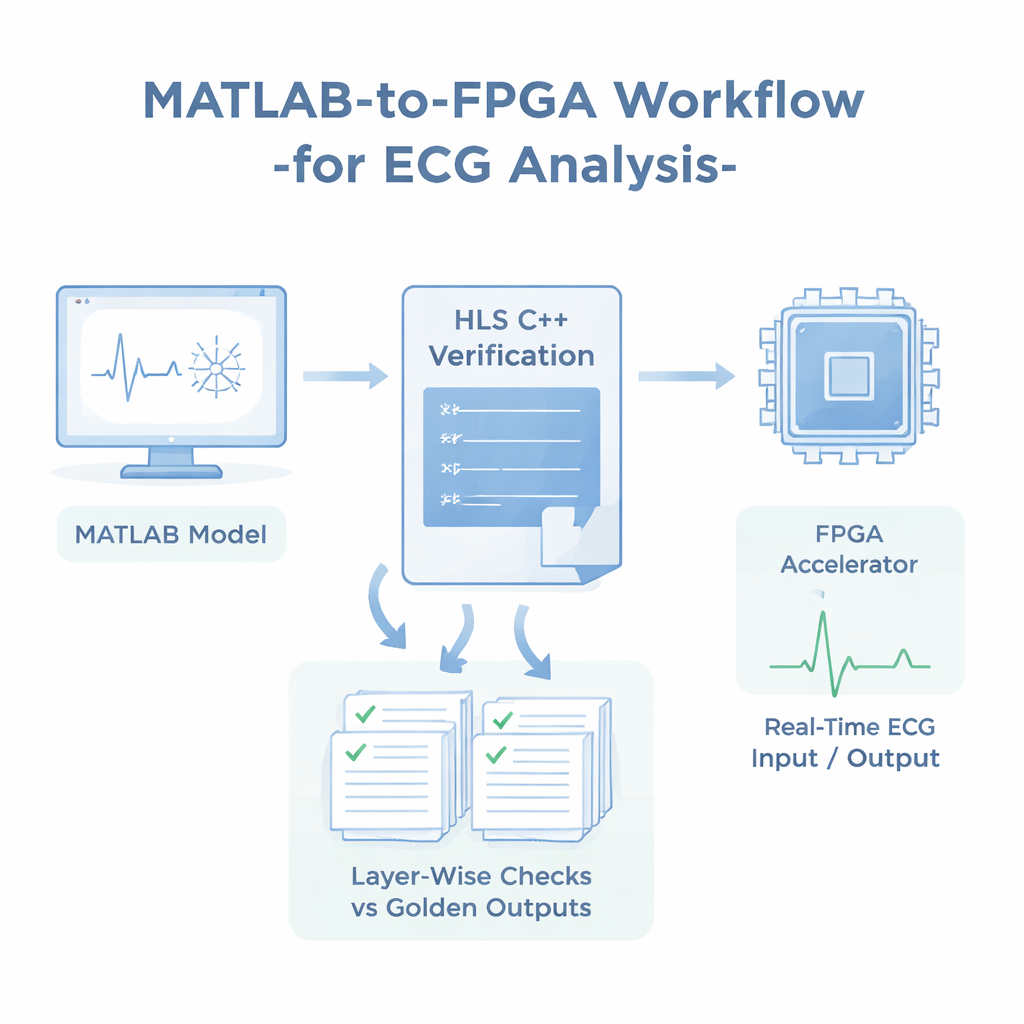

筆者はこのギャップに対処するため、MIT-BIH不整脈データベースからの心拍を分類する1次元畳み込みニューラルネットワークに対し、検証重視のワークフローを提案します。MATLABで構築されたこのネットワークは短いECG断片を調べ、正常やいくつかの異常リズムを含む5つの心拍タイプのいずれかに分類します。同一データで深さの異なる3種類のネットワークを訓練し、訓練後に重み、バイアス、テスト信号に対する各層の出力を「ゴールデン出力」として保存します。これはMATLABモデルがどのように振る舞うかの厳密な数値記録です。

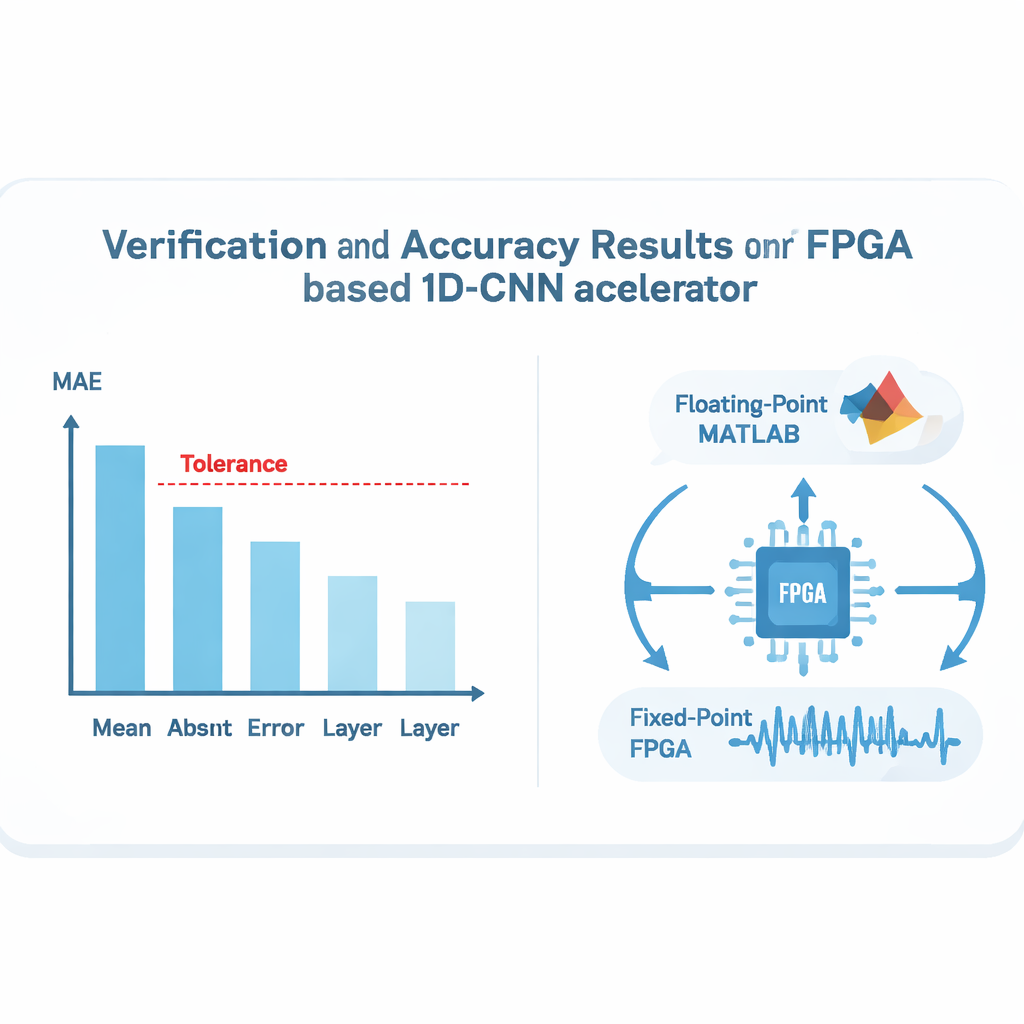

MATLABからC++、そしてFPGAへ—数値を追跡する

自動の「変換」ボタンを押す代わりに、ネットワークはMATLABと同じデータ配置と数式手順に従ってC++で手作業で再実装されます。このC++コードを高位合成ツールで用いてPYNQ-Z1 FPGAボード上で動作するハードウェアを生成します。各段階(MATLAB、C++、FPGA)で、層ごとの出力を保存済みのゴールデン出力と比較し、平均絶対誤差という単純な尺度で数値差の平均を測ります。研究では厳格な許容値を設定しており、すべての層が1.5×10⁻³未満の誤差にとどまる必要があります。何千ものECGサンプルにわたって試験した結果、すべての層がこの目標を満たし、最終的な分類精度もほとんど変わりませんでした:MATLABとC++で約98.3~98.4%で、FPGAでは固定小数点数を使うことによる予想される影響に一致して約0.2ポイント低下するにとどまりました。

数学を壊さずにハードウェアを高速化する

正しさが確保された後、設計は速度向上のためにチューニングされます。ネットワークで最も負荷の高い部分である畳み込み層は効率化のために固定小数点演算でFPGAのプログラマブルロジックに割り当てられ、最終的なソフトマックス計算のような軽い処理はチップ内蔵プロセッサ上で浮動小数点により実行されます。ループパイプライン化、ループアンローリング、メモリを並列バンクに分割するなどの手法により、計算とデータ転送の異なる部分を並行して実行できます。最適化されたハードウェアは心拍ウィンドウを約1.7ミリ秒で処理し、FPGAの資源と消費電力の範囲内に余裕を持って収まりつつ、元のMATLABモデルの層ごとの数値挙動を保持します。

今後のスマート機器にとっての意味

専門外の読者にとっての要点は、洗練されたMATLABベースの心拍分類器を低消費電力チップ上で高速化するだけでなく、チップ内部の挙動が各層ごとに信頼されるソフトウェアモデルと密接に一致していることを証明できるようになった点です。信頼性を犠牲にして速度を追うのではなく、このアプローチは浮動小数点MATLABコードから固定小数点FPGAハードウェアへの明確な監査トレイルを築きます。同じ検証手順—ゴールデン出力の保存、層ごとの誤差を厳格な閾値と比較、最終精度の確認—は、ウェアラブルヘルスモニタ、産業用センサー、自動運転車などの分野における他の1次元ニューラルネットワークにも適用でき、アルゴリズムが研究室を出てデバイスに移行するときにもその判断が信頼できることを助けます。

引用: Bal, S. Towards the transformation of MATLAB models into FPGA-Based hardware accelerators. Sci Rep 16, 5027 (2026). https://doi.org/10.1038/s41598-026-36033-z

キーワード: FPGAアクセラレータ, MATLABニューラルネットワーク, 心電図不整脈分類, ハードウェア検証, 固定小数点ディープラーニング