Clear Sky Science · it

Sinapsi spintroniche multi-bit scalabili e robuste per il calcolo analogico in memoria

Perché una memoria più intelligente conta per l’IA quotidiana

Dagli assistenti vocali alle app fotografiche, l’intelligenza artificiale moderna dipende fortemente dalle reti neurali profonde—programmi che gestiscono milioni di piccoli “pesi” numerici per prendere decisioni. Muovere questi pesi avanti e indietro tra memoria e processore costa molto più in termini di energia rispetto ai calcoli stessi. Questo articolo esplora un nuovo tipo di cella di memoria magnetica che può sia immagazzinare questi pesi sia contribuire a eseguire i calcoli direttamente dove risiedono i dati, promettendo hardware per l’IA più veloce ed efficiente.

Portare il calcolo ispirato al cervello nel chip di memoria

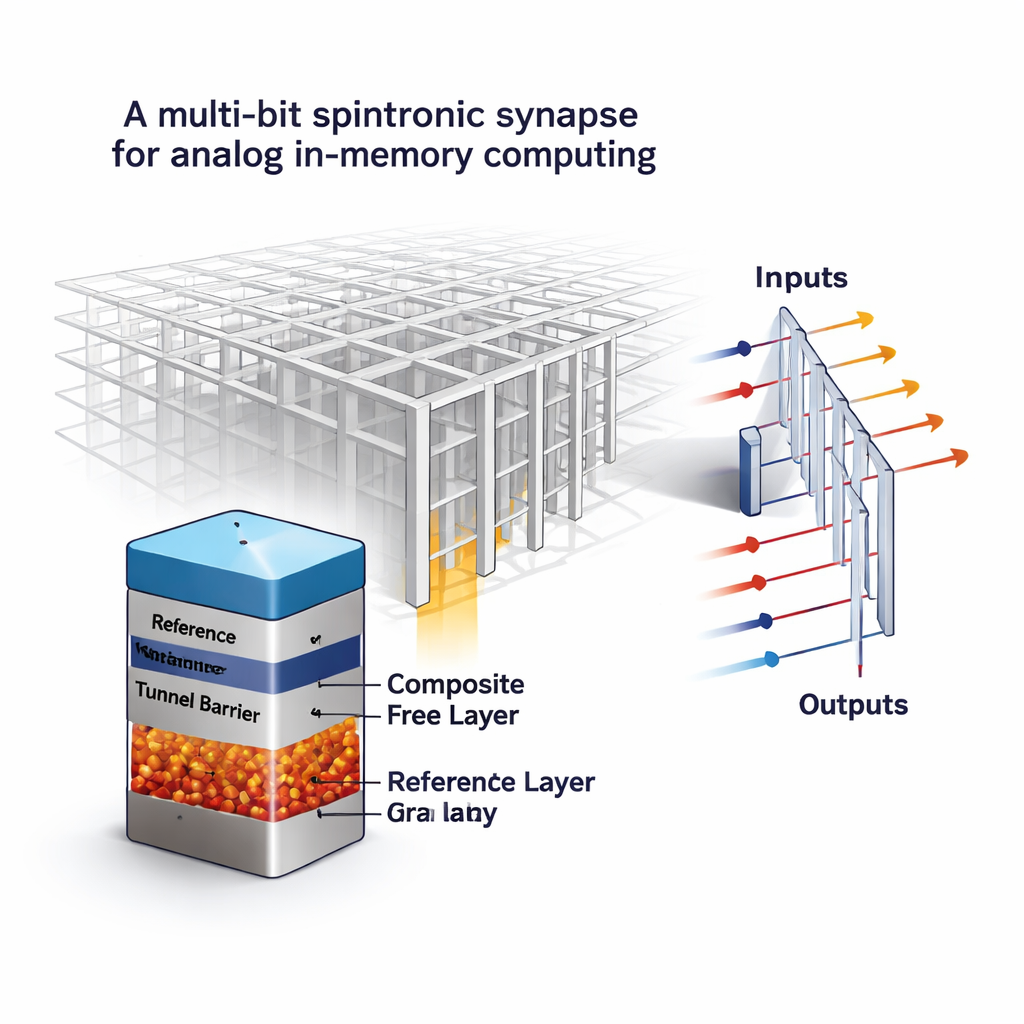

I computer odierni seguono l’architettura classica di von Neumann, in cui i dati vengono continuamente spostati tra memoria e un processore separato. Le reti neurali, riducibili a enormi moltiplicazioni matrice–vettore, si scontrano fortemente con questo collo di bottiglia. Un’alternativa promettente è il calcolo in memoria, dove una grande griglia (una matrice a croce) di celle di memoria conserva i pesi della rete e simultaneamente converte le tensioni in ingresso in correnti in uscita che rappresentano i calcoli. Molti dispositivi di memoria sperimentali sono stati testati per questo ruolo, ma spesso soffrono di comportamento rumoroso e valori che derivano nel tempo, cosa rischiosa quando ogni cella deve rappresentare più di un semplice 0 o 1.

Trasformare la memoria magnetica da on–off ad “analogica”

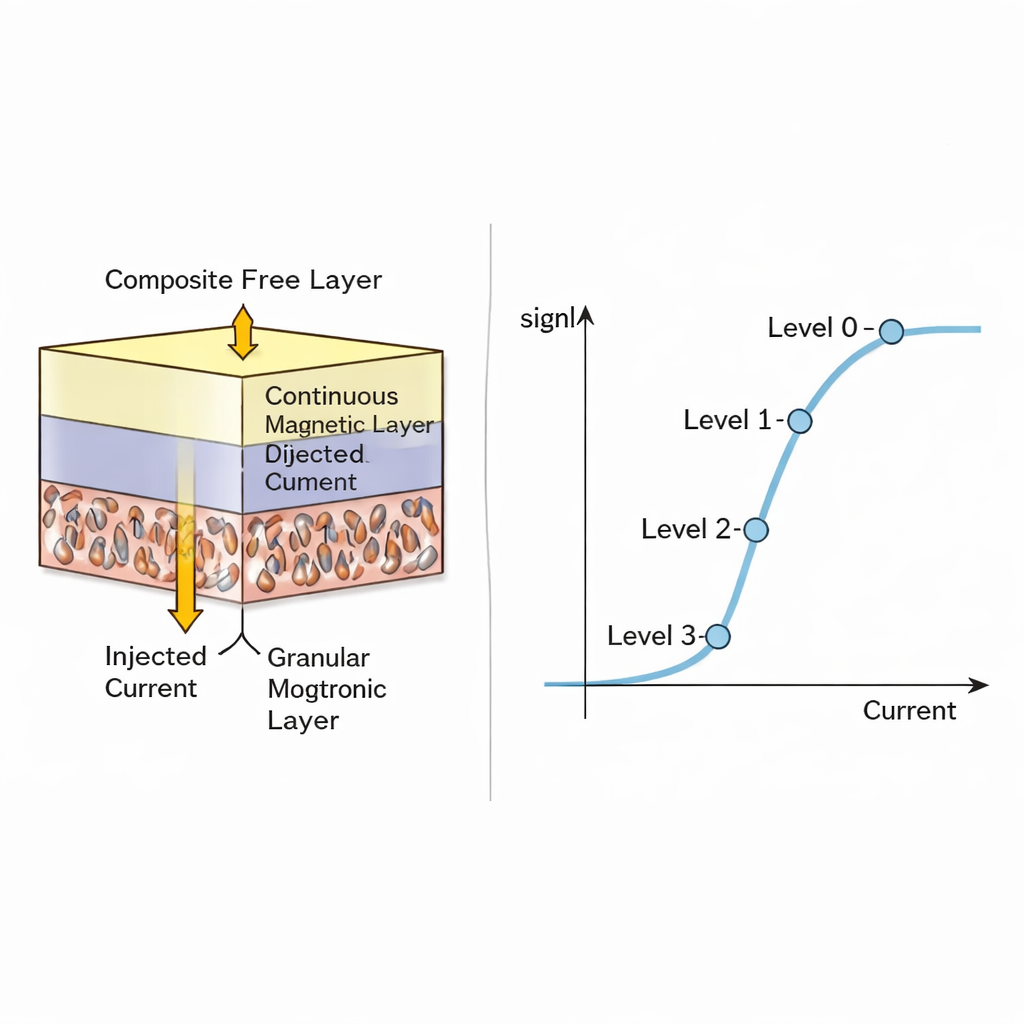

Gli autori si basano sulla memoria magnetica ad accesso casuale (MRAM), una tecnologia non volatile già apprezzata per velocità, durata e compatibilità con i processi standard dei chip. Una cella MRAM convenzionale è una giunzione tunnel magnetica: due strati magnetici separati da una barriera isolante. A seconda che gli strati siano allineati o opposti, la resistenza elettrica della cella è bassa o alta, codificando un singolo bit. La svolta chiave qui è riprogettare lo strato magnetico “libero” in modo che non sia più un blocco uniforme che si capovolge tutto in una volta. Invece, il nuovo progetto combina un film continuo molto sottile posto sopra uno strato magnetico granulare più spesso, composto da molti piccolissimi grani magnetici. Ogni grano può invertire la propria direzione a correnti leggermente diverse, perciò la resistenza complessiva può stabilizzarsi in diversi livelli intermedi stabili anziché solo “basso” e “alto”.

Quante sfumature di magnetismo sono utili?

Usando modelli al computer dettagliati della dinamica magnetica, il gruppo mostra che l’iniezione di una corrente polarizzata di spin in questo strato composito provoca un processo di commutazione graduale, grano dopo grano. Mentre la corrente viene variata, la magnetizzazione media e quindi la resistenza tracciano una curva a S liscia, permettendo stati analogici quasi continui. Gli autori esaminano poi come le differenze di fabbricazione tra le celle e gli effetti termici casuali da un ciclo di scrittura all’altro disturbino questi livelli. Riscontrano che mentre gli stati intermedi sono un po’ più rumorosi, gli stati estremi (completamente commutati in un senso o nell’altro) restano molto stretti e robusti. Per dispositivi di dimensioni realistiche (circa 50–75 nanometri per lato), concludono che quattro livelli di resistenza distinguibili in modo affidabile—equivalenti a 2 bit per cella—sono pratici senza errori eccessivi.

Dalla singola cella all’acceleratore AI completo

Per essere utile, questa MRAM multilevel deve essere letta con precisione e integrata in sistemi di calcolo completi. Gli autori progettano e simulano un circuito di sensing che usa un convertitore analogico-digitale “flash” veloce per distinguere i quattro livelli di resistenza di ciascuna cella. Esplorano come il contrasto tra gli stati di conduttanza più alto e più basso influisca sulla velocità di lettura, sul consumo energetico e sulla dimensione dei circuiti di sensing, mostrando che un contrasto migliore porta direttamente a letture più rapide ed efficienti. Successivamente, integrano il loro modello di MRAM a 2 bit per cella in un acceleratore in memoria simulato che esegue una rete ResNet-18 sul dataset di immagini CIFAR-10. Rispetto a un riferimento che usa celle MRAM standard a 1 bit, la versione multibit raddoppia all’incirca la densità di memoria e dimezza il numero necessario di tile a matrice. Questo si traduce in riduzioni fino a circa 1,8× dell’area del chip, dell’energia e della latenza, e in oltre 3× di miglioramento del metrica combinata energia–ritardo, il tutto preservando sostanzialmente la precisione di riconoscimento della rete.

Come si confronta con altre idee di memoria

Lo studio confronta inoltre questo approccio con tecnologie concorrenti come la resistive RAM e la memoria a cambiamento di fase, oltre ad altri concetti magnetici che sfruttano lo spostamento di pareti di dominio o skyrmion. Pur potendo anch’esse produrre comportamenti analogici, quelle alternative spesso richiedono dispositivi più grandi o forme speciali e tendono a essere più imprevedibili. Invece, le celle MRAM granulari mantengono la facilità di produzione e la resistenza della MRAM mainstream ottenendo livelli di memorizzazione aggiuntivi. I test a livello di sistema suggeriscono che, sotto variazioni realistiche, le sinapsi basate su MRAM mantengono l’accuratezza delle reti neurali molto più alta rispetto a progetti simili basati su memorie resistive più variabili, specialmente quando le reti vengono rese sparse per risparmiare ulteriormente energia.

Cosa significa per l’IA quotidiana del futuro

In termini semplici, gli autori hanno mostrato un modo per insegnare a una tecnologia di memoria magnetica consolidata a immagazzinare non solo zeri e uni, ma piccoli valori di peso analogici direttamente all’interno di una cella compatta. Ingegnerizzando con cura una struttura stratificata che distribuisce il comportamento magnetico su molti piccoli grani, ottengono molteplici livelli di resistenza stabili e sufficientemente robusti per compiti di IA nel mondo reale. Quando queste celle sono disposte in grandi array e abbinate a circuiti di sensing adeguati, possono eseguire i calcoli fondamentali del deep learning riducendo drasticamente il movimento dei dati. Se realizzate in hardware, tali sinapsi spintroniche multi-bit potrebbero rendere i sistemi IA futuri—nei data center, negli smartphone o nei sensori incorporati—più veloci e più efficienti dal punto di vista energetico senza sacrificare l’accuratezza.

Citazione: Gupte, K.K., Mugdho, S.S., Huang, C. et al. Scalable and robust multi-bit spintronic synapses for analog in-memory computing. npj Unconv. Comput. 3, 8 (2026). https://doi.org/10.1038/s44335-026-00055-7

Parole chiave: calcolo in memoria, memoria spintronica, MRAM, hardware neuromorfico, reti neurali profonde