Clear Sky Science · it

Cella di guadagno con semiconduttore ossido integrata nella memoria: materiali e strategie di integrazione per la prossima generazione di memorie on‑chip

Perché una memoria più veloce e più intelligente è importante

I nostri telefoni, laptop e data center diventano sempre più potenti, ma permane un limite nascosto alla velocità: lo spostamento dei dati tra processore e memoria. Questo articolo esplora un nuovo tipo di memoria on‑chip che potrebbe attenuare questa “wall della memoria”, rendendo i computer futuri più rapidi ed efficienti dal punto di vista energetico per compiti come l’intelligenza artificiale, il cloud computing e le applicazioni di uso quotidiano. Ripensando la costruzione delle celle di memoria e i materiali impiegati, i ricercatori mirano a collocare molta più memoria vicino al processore riducendo al contempo i consumi e il calore prodotto.

Il collo di bottiglia all’interno dei computer moderni

Per decenni le prestazioni dei processori sono migliorate molto più rapidamente rispetto alla memoria principale che li alimenta di dati. Questo disallineamento, noto come memory wall, fa sì che chip veloci spesso rimangano inattivi in attesa delle informazioni. I progettisti hanno provato ad attenuare questo collo di bottiglia con molteplici livelli di cache posizionati sul processore stesso. Le cache odierne si basano su un tipo di memoria chiamata SRAM, molto veloce ma ingombrante e dispendiosa in energia perché ogni bit richiede sei transistor. Per aumentare la capacità, le aziende impilano chip SRAM in tre dimensioni o aggiungono DRAM integrata sul chip, ma la DRAM tradizionale dipende ancora da minuscoli condensatori difficili da produrre a scale estreme e complessi da integrare con la logica standard.

Una diversa tipologia di cella di memoria

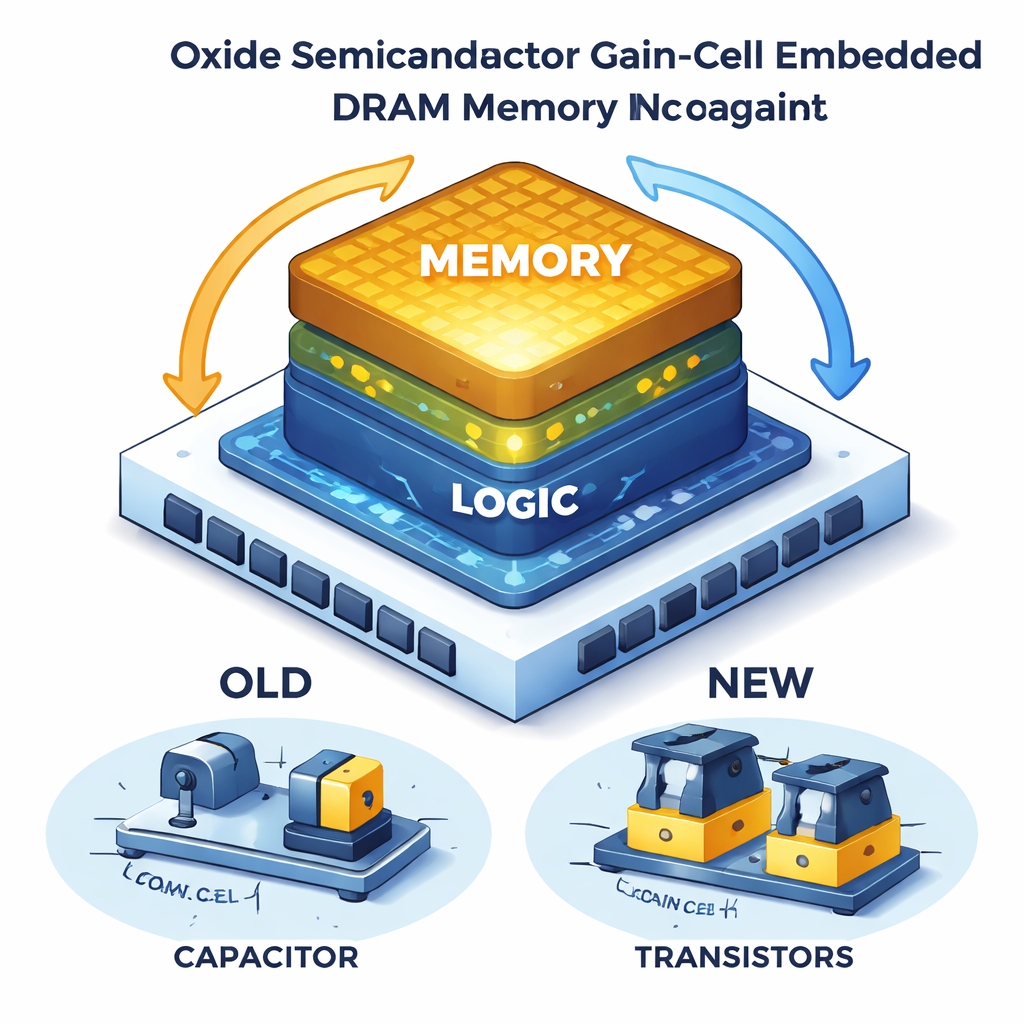

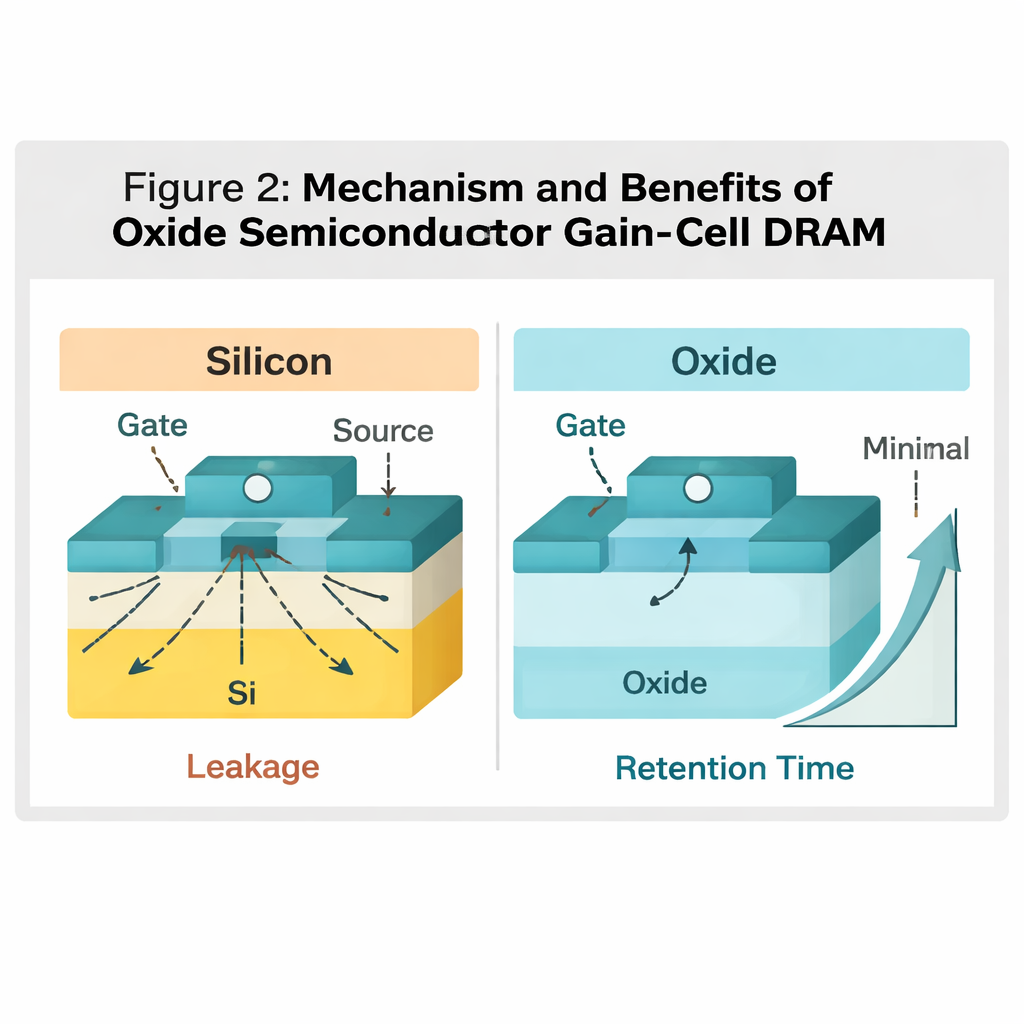

L’articolo si concentra su un’alternativa chiamata gain‑cell embedded DRAM, o GC‑eDRAM. Invece di usare un condensatore separato per immagazzinare carica, una gain cell impiega solo transistor per mantenere i dati, semplificando la struttura e rendendola più compatibile con la produzione standard di chip. Questo progetto si presta naturalmente all’impilamento tridimensionale sopra i circuiti logici, promettendo layout “memory‑on‑logic” ad alta densità. Un altro vantaggio è il comportamento di lettura non distruttiva: leggere un valore memorizzato non lo scarica immediatamente, il che può ridurre la frequenza dei refresh. Tuttavia, nelle versioni tradizionali al silicio la carica immagazzinata si disperde in meno di un millisecondo, quindi i refresh frequenti continuano a sprecare energia e limitare l’utilità.

Semiconduttori a ossido: interruttori più silenziosi e freddi

Per superare le perdite nelle gain cell, gli autori evidenziano i semiconduttori a ossido — materiali come indio‑gallio‑zinco ossido (IGZO) e composti correlati — come nuovi materiali per il canale dei transistor. Questi ossidi hanno un gap energetico ampio, che sopprime fortemente le correnti indesiderate quando un transistor dovrebbe essere spento. Esperimenti hanno misurato correnti di leakage così piccole da avvicinarsi ai limiti degli strumenti di prova, e le celle di guadagno prototipo ora mantengono i dati per molti secondi, ore o persino più di un giorno, rispetto ai millesimi di secondo dei progetti in silicio. Crucialmente, questi ossidi possono essere depositati a temperature relativamente basse compatibili con il “back‑end” della fabbricazione dei chip, permettendo agli ingegneri di costruire strati di memoria densi direttamente sopra la logica in silicio esistente senza danneggiarla.

Costruire verso l’alto: impilamenti 3D e transistor minuscoli

Con il continuo rimpicciolimento dei chip, rendere i transistor più piccoli introduce nuovi problemi, come il controllo difficile del canale e l’aumento delle perdite. L’articolo passa in rassegna forme avanzate di transistor che avvolgono il gate attorno al canale (design gate‑all‑around e channel‑all‑around) per mantenere un controllo stretto anche a dimensioni nanometriche. Usando semiconduttori a ossido in queste strutture multi‑gate, i ricercatori hanno dimostrato canali molto corti, leakage estremamente basso e forte ritenzione dei dati mentre impilano più strati di memoria verticalmente. Alcuni design sperimentali già raggiungono o superano l’efficienza d’area delle migliori celle DRAM odierne, suggerendo che chip futuri potrebbero ospitare capacità di memoria enormi in un ingombro molto piccolo proprio sopra i core del processore.

Dai materiali di laboratorio a prodotti affidabili

Trasformare questi dispositivi promettenti in memorie pratiche richiede una precisa ingegneria dei materiali. L’articolo descrive come modulare la miscela di metalli nell’ossido, controllare il contenuto di ossigeno e cristallizzare i film per bilanciare alta velocità e stabilità a lungo termine. Copre anche modalità per gestire difetti, contaminazione da idrogeno e le interfacce delicate tra ossidi e strati isolanti in modo che i dispositivi rimangano stabili sotto il calore e l’operazione prolungata. Infine, discute l’ingegneria delle connessioni metalliche affinché la resistenza di contatto non vanifichi i vantaggi dei nuovi materiali. Insieme, queste strategie mirano a fornire una memoria densa e sufficientemente affidabile per la produzione su larga scala.

Cosa significa per il computing di tutti i giorni

Gli autori concludono che le memorie a gain‑cell con semiconduttori a ossido potrebbero rimodellare il modo in cui saranno costruiti i chip futuri. Combinando celle di memoria minuscole e a basso leakage con impilamenti 3D sopra i circuiti logici, i progettisti potrebbero collocare molta più memoria veloce vicino al processore mantenendo sotto controllo i consumi. Questo attenuerebbe la memory wall, aiutando tutto, dagli acceleratori AI ai server cloud e ai dispositivi personali a funzionare più velocemente ed efficientemente. Sebbene rimangano sfide in termini di affidabilità, uniformità produttiva e integrazione a livello di chip completo, il lavoro qui recensito delinea un percorso chiaro verso sistemi di calcolo più compatti, potenti e attenti all’energia.

Citazione: Chung, S.W., Yoon, S.H. & Jeong, J.K. Oxide semiconductor gain cell-embedded memory: materials and integration strategies for next generation on-chip memory. Commun Eng 5, 39 (2026). https://doi.org/10.1038/s44172-026-00616-5

Parole chiave: memoria on‑chip, semiconduttori a ossido, scaling della DRAM, circuiti integrati 3D, hardware per AI