Clear Sky Science · it

Gestione termica di microelettronica 3-D eterogeneamente integrata: sfide e direzioni future della ricerca

Perché l’impilamento dei chip cambia i tuoi dispositivi quotidiani

Da telefoni e portatili fino ai data center che alimentano l’intelligenza artificiale, la nostra elettronica continua a ridursi di dimensioni mentre svolge sempre più compiti. Per ottenerlo, gli ingegneri stanno ora impilando diversi tipi di chip uno sopra l’altro, creando package tridimensionali compatti. Questa mossa intelligente aumenta le prestazioni e riduce i ritardi di segnale, ma intrappola anche enormi quantità di calore in uno spazio molto piccolo. L’articolo recensito spiega perché il calore è diventato una delle minacce maggiori per questa nuova generazione di elettronica — e cosa stanno facendo i ricercatori per impedire che questi piccoli grattacieli di silicio si surriscaldino.

Costruire piccoli grattacieli di elettronica

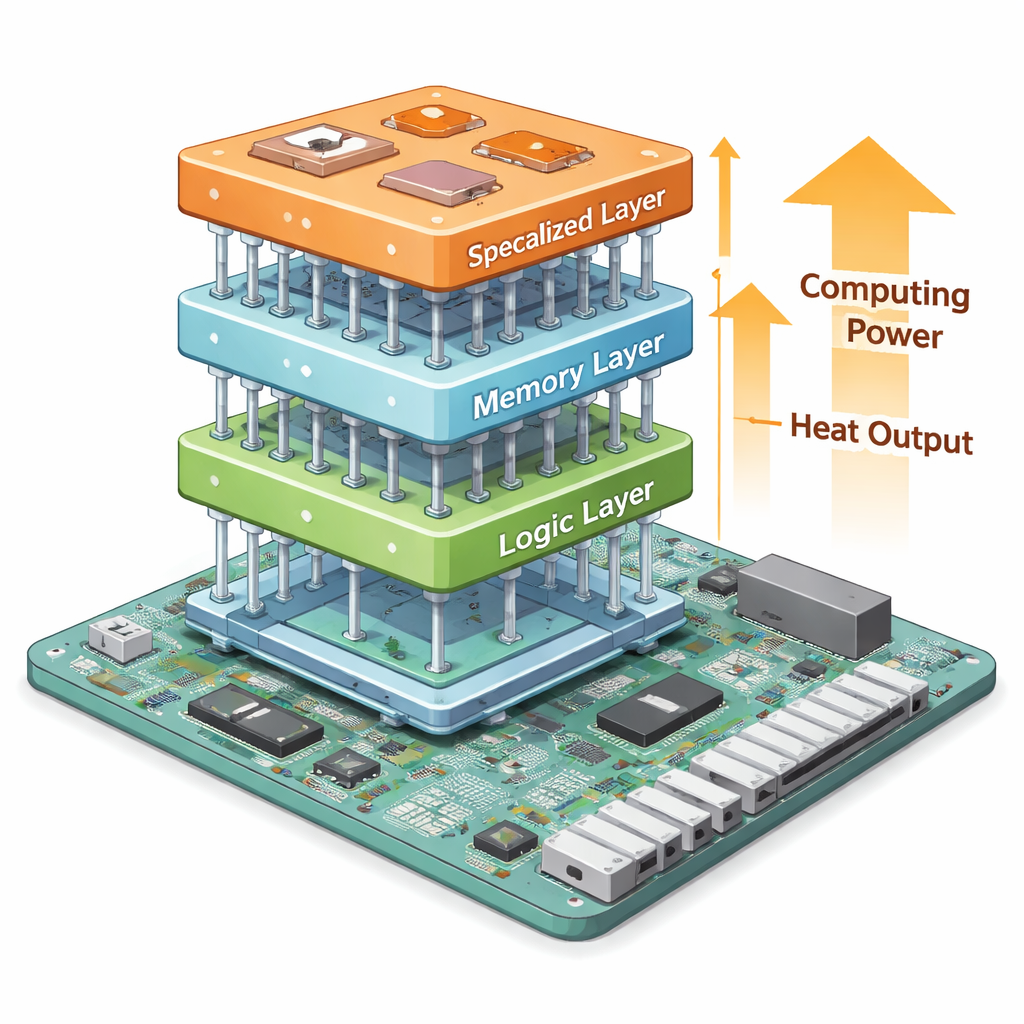

I chip tradizionali sono per lo più piatti: i circuiti si estendono affiancati su una singola fetta di silicio. Quando diventa più difficile continuare a ridurre le caratteristiche in due dimensioni, l’industria si orienta verso l’integrazione eterogenea tridimensionale, in cui diversi strati di chip — logica, memoria, radio, fotonica e altri — sono impilati verticalmente e collegati da pilastri metallici. Questa disposizione accorcia i percorsi di comunicazione e permette ai progettisti di combinare tecnologie prodotte in fabbriche differenti. Il risultato è un’elaborazione più veloce, minori ritardi di comunicazione e un uso energetico migliore, particolarmente preziosi per l’intelligenza artificiale, il cloud computing e i sistemi di comunicazione avanzati.

Il costo nascosto di concentrare più potenza

Impilare i chip così strettamente comporta un serio svantaggio: il calore fatica di più a fuoriuscire. Ogni strato genera calore attraverso le perdite elettriche note — resistenza nei conduttori, commutazione dei dispositivi e piccole correnti di perdita che non si spengono mai del tutto. Negli stack 3-D queste perdite si sommano, e gli strati centrali, più lontani da qualsiasi superficie di raffreddamento, tendono a diventare i più caldi. La temperatura può aumentare in modo non uniforme, creando hotspot che sono solo frazioni di millimetro ma molto più caldi dell’ambiente circostante. Anche pochi gradi oltre l’intervallo operativo previsto possono ridurre drasticamente l’affidabilità, accelerare l’usura e, nei casi estremi, innescare un ciclo auto‑alimentato di aumento della temperatura e della corrente noto come runaway termico.

Quando il calore si diffonde, piega e danneggia

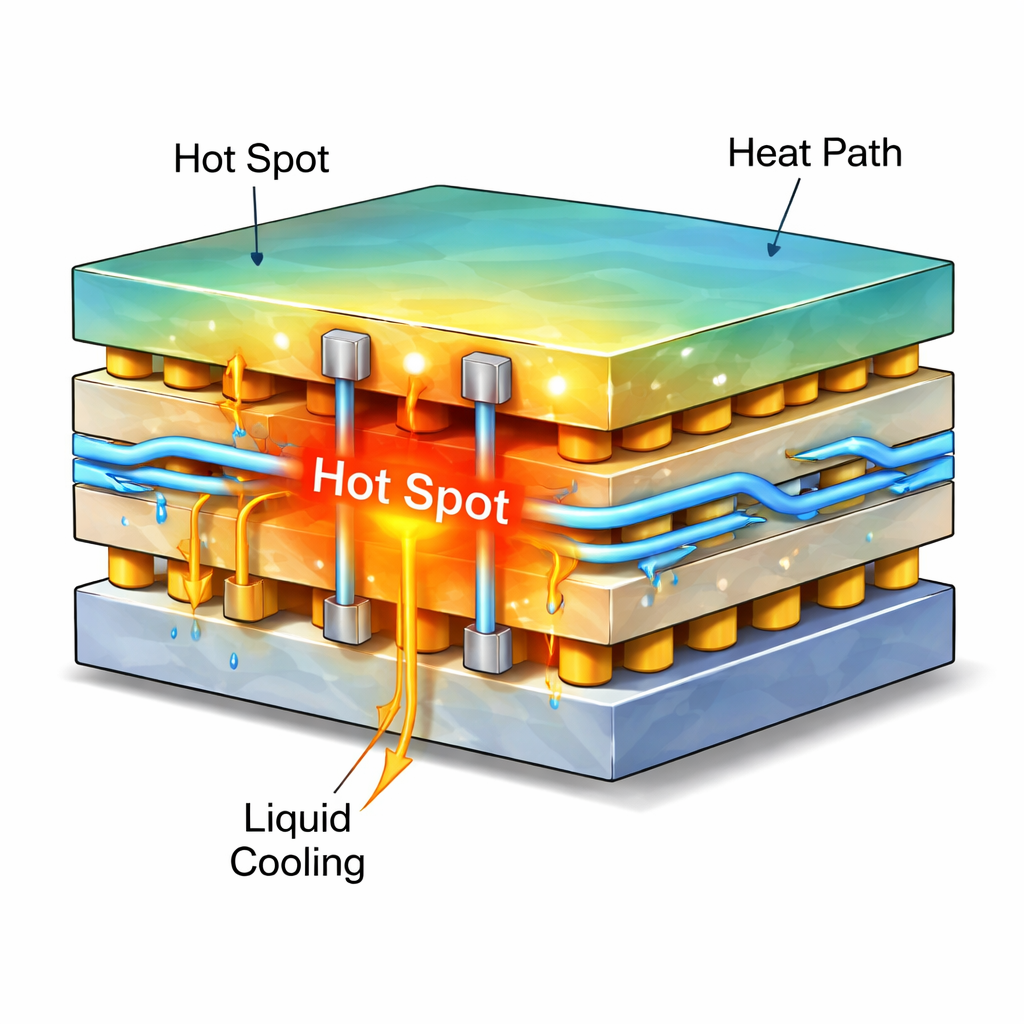

La recensione spiega che i problemi termici non riguardano solo un chip che funziona a temperature elevate; possono danneggiare silenziosamente l’intero package. I diversi materiali nello stack — silicio, metalli, polimeri e ceramiche — si espandono in modo diverso quando riscaldati. Mentre il dispositivo cicla tra inattività e piena potenza, questi disaccoppiamenti generano sollecitazioni meccaniche che possono incrinare le giunzioni di saldatura, aprire gap alle interfacce e danneggiare i collegamenti verticali riempiti di metallo. Allo stesso tempo, il riscaldamento non uniforme causa crosstalk termico: un die logico caldo può riscaldare involontariamente un livello di memoria a bassa potenza o uno strato ottico sovrastante, degradandone le prestazioni. Col tempo, piccole cavità e crepe attorno alle strutture che trasportano il calore crescono, aggiungendo ulteriore resistenza termica e rendendo ancora più difficile rimuovere il calore dove conta di più.

Nuovi stratagemmi per spostare il calore in tre dimensioni

Per affrontare queste sfide, i ricercatori stanno ripensando ogni parte del percorso termico. Alcune strategie mirano a distribuire meglio il calore all’interno dello stack utilizzando underfill e materiali interstrato che conducono bene il calore senza disturbare i segnali elettrici. Altre riutilizzano i pilastri metallici verticali come condotti termici dedicati o aggiungono pilastri aggiuntivi solo per il calore accanto ai percorsi di segnale. La recensione evidenzia anche uno spostamento verso l’avvicinare molto il sistema di raffreddamento alla sorgente di calore. Piccoli canali liquidi e foreste di pin‑fin microscopici possono essere ricavati direttamente dentro o tra gli strati dei chip, permettendo al refrigerante di fluire a poche decine di micrometri dai punti più caldi. Questi raffreddatori incorporati possono rimuovere flussi di calore estremi adattando il flusso alle esigenze di ciascuno strato, ma introducono nuovi problemi di resistenza meccanica, complessità produttiva e affidabilità a lungo termine sotto pressione e umidità.

Dove si dirige il campo

Nel complesso, l’articolo conclude che il controllo del calore determinerà in larga misura fino a che punto potranno progredire l’elettronica impilata 3‑D. Nessuna singola soluzione è sufficiente: layout del chip, materiali, connessioni verticali, strati di interfaccia e canali di raffreddamento devono essere progettati insieme anziché isolatamente. I lavori futuri si concentreranno su modi scalabili per combinare materiali ad alta conduttività e compatibili meccanicamente con processi produttivi a bassa temperatura realizzabili, così come su strumenti di progettazione più intelligenti che trattino il comportamento termico sullo stesso piano di velocità e consumo energetico. Se questi ostacoli verranno superati, gli stack di chip tridimensionali potrebbero continuare a fornire maggiore potenza di calcolo in package sempre più piccoli — senza bruciarsi.

Citazione: Sharma, M.K., Ramos-Alvarado, B. Thermal management of 3-D heterogeneously integrated microelectronics: challenges and future research directions. Commun Eng 5, 28 (2026). https://doi.org/10.1038/s44172-026-00590-y

Parole chiave: impilamento di chip 3D, raffreddamento dell’elettronica, gestione termica, raffreddamento microfluidico, integrazione eterogenea