Clear Sky Science · it

Mappare le dinamiche di isteresi diverse nei FET a MoS2 scalati usando il metodo universale derivato dal modellismo TCAD

Perché gli interruttori minuscoli hanno bisogno di comportamento affidabile

L’elettronica moderna corre verso transistor sempre più piccoli, e materiali bidimensionali (2D) come il disolfuro di molibdeno (MoS2) sono candidati di primo piano per i chip futuri. Ma man mano che questi interruttori si riducono, il loro comportamento può diventare incoerente: lo stesso dispositivo può rispondere in modo diverso a seconda di come è stato utilizzato pochi istanti prima. Questo effetto simile a una memoria, chiamato isteresi, viene spesso liquidato come un fastidio minore. In questo lavoro gli autori mostrano che l’isteresi nasconde in realtà una grande quantità di informazioni sui difetti nascosti all’interno dei transistor avanzati — e introducono un modo universale per leggere queste informazioni.

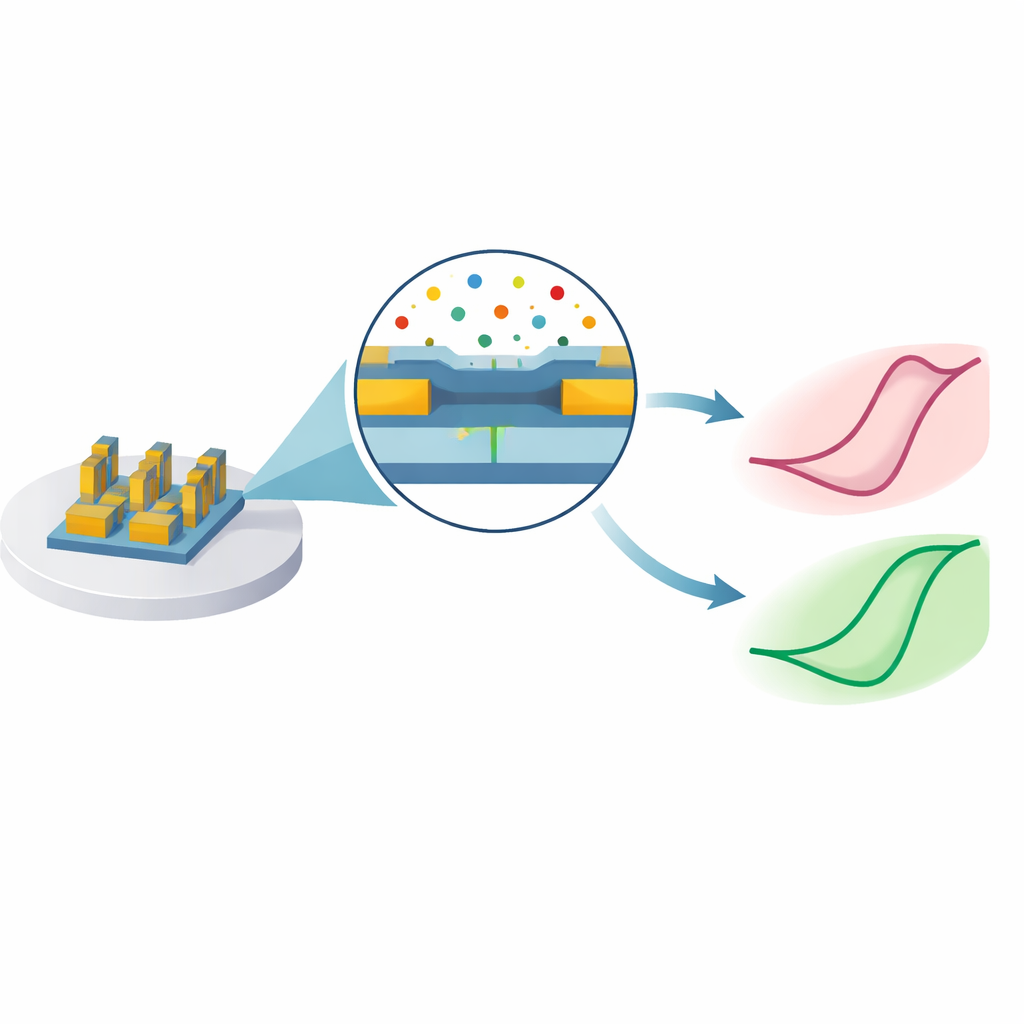

Come sono costruiti i transistor di nuova generazione

I futuri transistor a effetto di campo 2D usano uno strato ultrafine di MoS2 come canale in cui scorre la corrente, ricoperto da un ossido isolante molto sottile come l’ossido di hafnio (HfO2), e con un gate metallico in cima. Per continuare a ridurre le dimensioni, questo ossido deve essere, in termini elettrici, spesso circa un nanometro, il che significa che qualsiasi singolo difetto al suo interno può perturbare fortemente il canale. Questi difetti agiscono come trappole minuscole che possono trattenere o rilasciare temporaneamente carica elettrica. Poiché i difetti possono trovarsi a profondità diverse all’interno dell’ossido e interagire sia con il canale sia con il gate, il loro comportamento collettivo può stabilizzare o destabilizzare il transistor in modi sottili. Comprendere questo paesaggio di difetti è cruciale se i transistor 2D devono competere con la tecnologia al silicio odierna.

Perché il transistor si ricorda del passato

Quando gli ingegneri fanno scorrere la tensione di gate su e giù e registrano la corrente, spesso osservano che le curve di salita e discesa non coincidono. Questo ciclo è l’isteresi. Tradizionalmente i ricercatori misurano la distanza tra le due curve in un singolo punto operativo e la chiamano ampiezza dell’isteresi, concludendo spesso che è “piccola” o “trascurabile”. Gli autori sostengono che questa pratica è fuorviante, soprattutto per dispositivi scalati in cui diversi gruppi di difetti possono contribuire in modo opposto. A seconda della velocità di misura e della corrente operativa, lo stesso transistor può mostrare loop convenzionali in senso orario, loop invertiti in senso antiorario, passaggi tra i due, o perfino quasi nessuna isteresi quando gli effetti opposti si annullano.

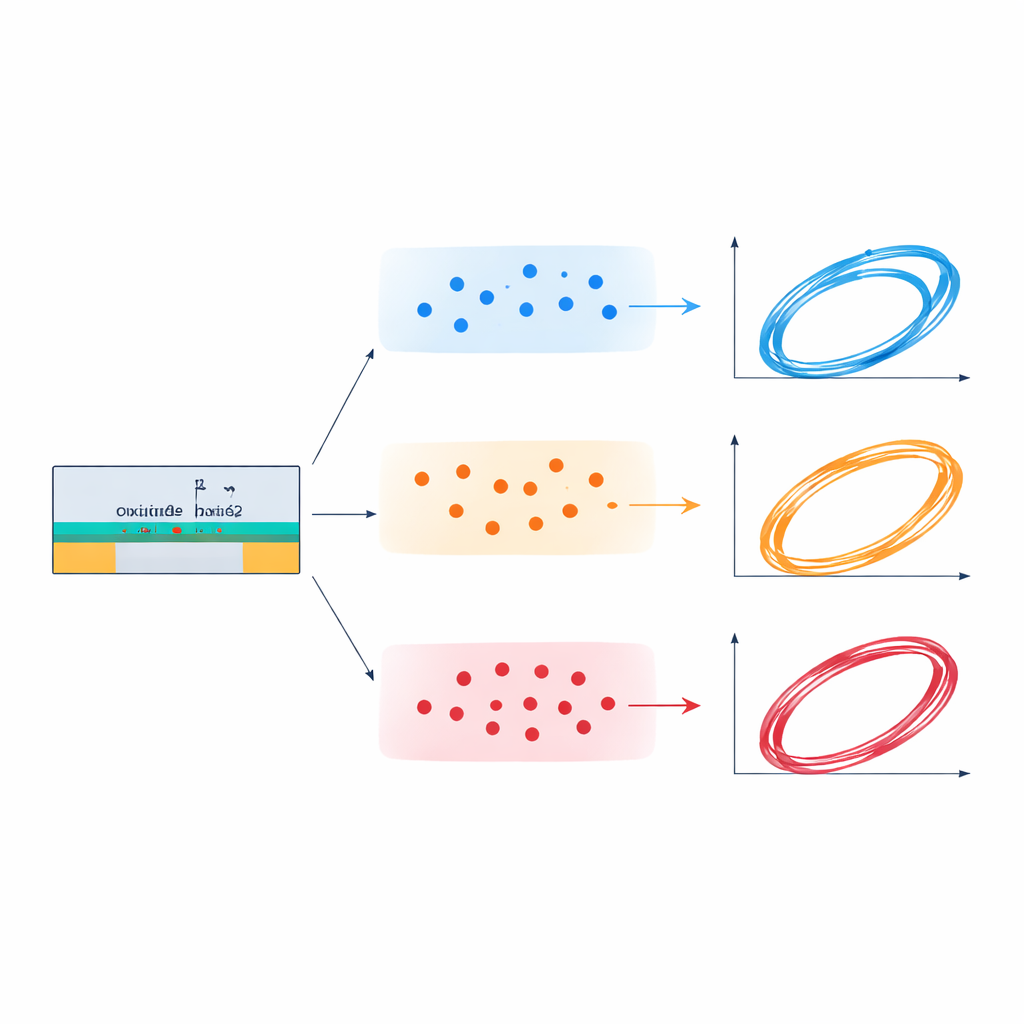

Una mappa universale nascosta nelle curve

Per districare questa complessità, il team usa simulazioni al computer dettagliate (TCAD) di transistor a base di MoS2 a scala nanometrica con popolazioni di difetti controllate a diverse profondità nell’ossido. Propongono quindi un metodo universale di mappatura dell’isteresi. Invece di estrarre un singolo numero, scandagliano l’ampiezza dell’isteresi su un’ampia gamma di correnti — da poco sopra lo stato off fino vicino allo stato on — e per tempi di sweep che coprono molti ordini di grandezza. Questo produce migliaia di curve che mostrano come l’isteresi varia con la velocità di misura a ciascuna corrente. Da queste definiscono due “funzioni universali di isteresi”, superiore e inferiore, che racchiudono tutti i comportamenti possibili. Questi involucri rivelano chiaramente quali tipi di difetti sono attivi, se interagiscono principalmente con il canale o con il gate superiore, e se favoriscono loop in senso orario o antiorario.

Collegare loop veloci a derive a lungo termine

Gli stessi difetti che causano l’isteresi guidano anche derive lente nel comportamento del transistor sotto stress prolungato, un problema noto come bias temperature instability (BTI). Simulando esperimenti standard di stress e recupero, gli autori collegano caratteristiche delle loro mappe di isteresi a firme BTI insolite, come uno spostamento apparente negativo che solo in seguito si rilassa verso uno positivo. Mostrano che le trappole vicine al canale tendono a causare spostamenti lenti e in gran parte permanenti, mentre le trappole più vicine al gate provocano cambiamenti più rapidi ma in larga parte reversibili. Il loro metodo può essere applicato non solo a dispositivi MoS2 simulati ma anche a dati misurati provenienti da transistor reali a base di MoS2 e WSe2 fabbricati in laboratori di ricerca e linee pilota, inclusi casi in cui ioni in deriva nell’ossido partecipano al gioco dell’accumulo di carica.

Da dati complessi a indicazioni pratiche

Trasformando loop di isteresi confusi in mappe standardizzate, questo lavoro offre un potente strumento diagnostico per le tecnologie emergenti di transistor. Il metodo funziona direttamente su insiemi di dati sperimentali e non richiede l’accesso a strumenti di simulazione avanzati, rendendolo ampiamente utilizzabile nei laboratori. Per gli ingegneri, il messaggio chiave è che l’isteresi non è solo un difetto da minimizzare, ma un’impronta digitale dei problemi di affidabilità sottostanti. Decodificare quell’impronta con il metodo di mappatura proposto può guidare la scelta di materiali migliori, interfacce più pulite e processi più intelligenti, aiutando i transistor 2D a passare da prototipi promettenti a mattoni davvero affidabili dell’elettronica futura.

Citazione: Lv, Y.Z., Wu, Y.H., Cai, H.H. et al. Mapping diverse hysteresis dynamics in scaled MoS2 FETs using the universal method derived from TCAD modeling. npj 2D Mater Appl 10, 35 (2026). https://doi.org/10.1038/s41699-026-00671-8

Parole chiave: transistor 2D, isteresi, difetti dell'ossido, affidabilità del dispositivo, FET a MoS2