Clear Sky Science · it

Verso la trasformazione di modelli MATLAB in acceleratori hardware basati su FPGA

Trasformare gli algoritmi da laboratorio in dispositivi reali

Molte delle innovazioni moderne in medicina e ingegneria nascono come software scritto dai ricercatori, spesso con strumenti user‑friendly come MATLAB. Ma quando quegli stessi algoritmi devono funzionare in tempo reale—ad esempio per riconoscere problemi di ritmo cardiaco pericolosi da un elettrocardiogramma (ECG)—servono la velocità e l’efficienza dell’hardware dedicato. Questo articolo mostra come trasferire in modo affidabile una rete neurale complessa per il rilevamento del battito cardiaco da MATLAB su un chip specializzato chiamato FPGA, senza perdere l’accuratezza di cui medici e ingegneri si affidano.

Perché riscrivere il codice per i chip è così difficile

Gli FPGA (Field‑Programmable Gate Arrays) sono chip riconfigurabili apprezzati per la loro velocità e il basso consumo energetico. Tradizionalmente programmarli richiedeva linguaggi orientati all’hardware come VHDL o Verilog, molto distanti dal codice matematico e di elaborazione del segnale di alto livello che gli scienziati scrivono in MATLAB. Nuovi strumenti possono convertire automaticamente gli algoritmi in descrizioni hardware, ma spesso richiedono intervento manuale e si concentrano principalmente sulle prestazioni: quanto è veloce il chip e quante risorse usa. Ciò che mancava era un metodo chiaro per dimostrare che l’hardware fa esattamente ciò che faceva il software originale, strato dopo strato, numero dopo numero.

Un controllo passo dopo passo per ogni layer della rete

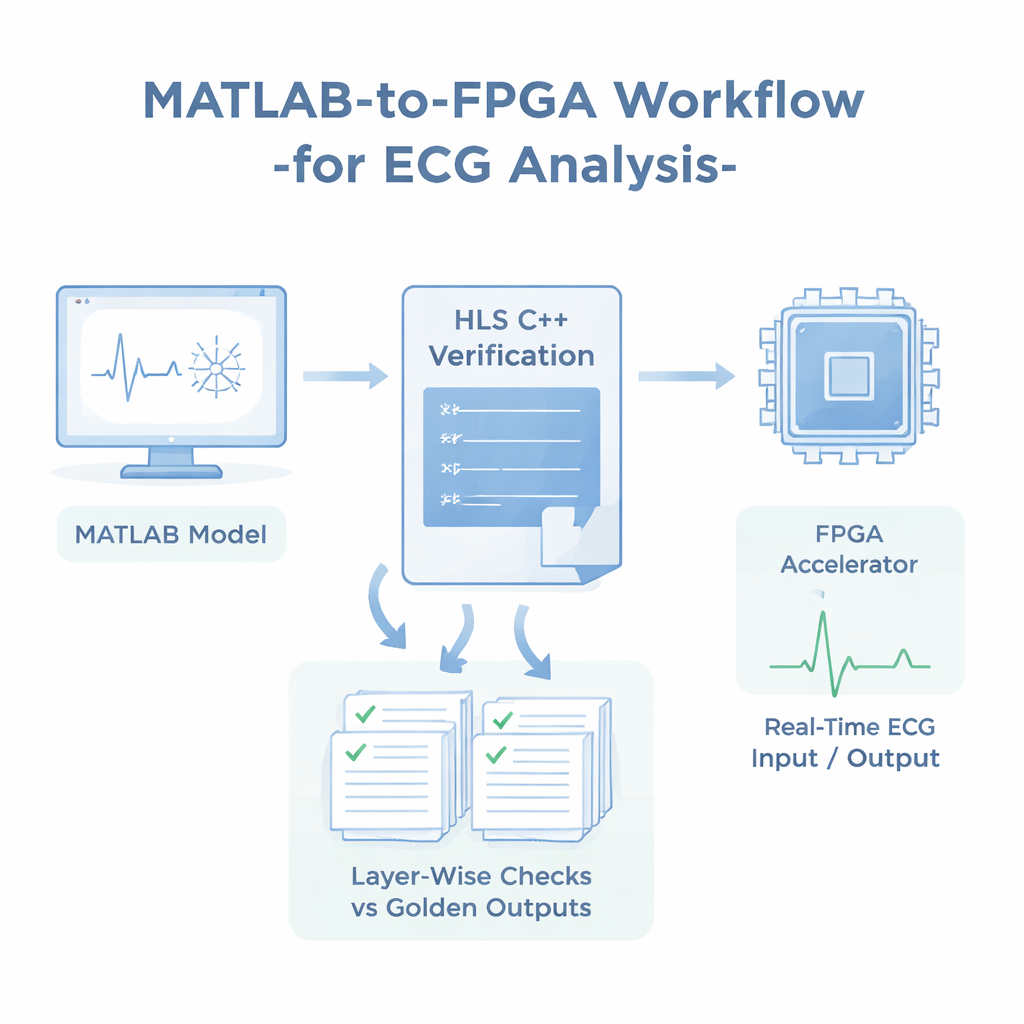

L’autore colma questa lacuna proponendo un flusso di lavoro focalizzato sulla verifica per una rete neurale convoluzionale monodimensionale che classifica i battiti cardiaci dal noto MIT‑BIH Arrhythmia Database. La rete, costruita in MATLAB, analizza brevi porzioni di dati ECG e le assegna a uno dei cinque tipi di battito, includendo il normale e diversi ritmi anomali. Tre versioni della rete, con profondità differenti, sono addestrate sugli stessi dati. Dopo l’addestramento, pesi, bias e gli output di ogni layer sui segnali di test vengono salvati come «golden outputs»—un registro numerico preciso del comportamento del modello MATLAB.

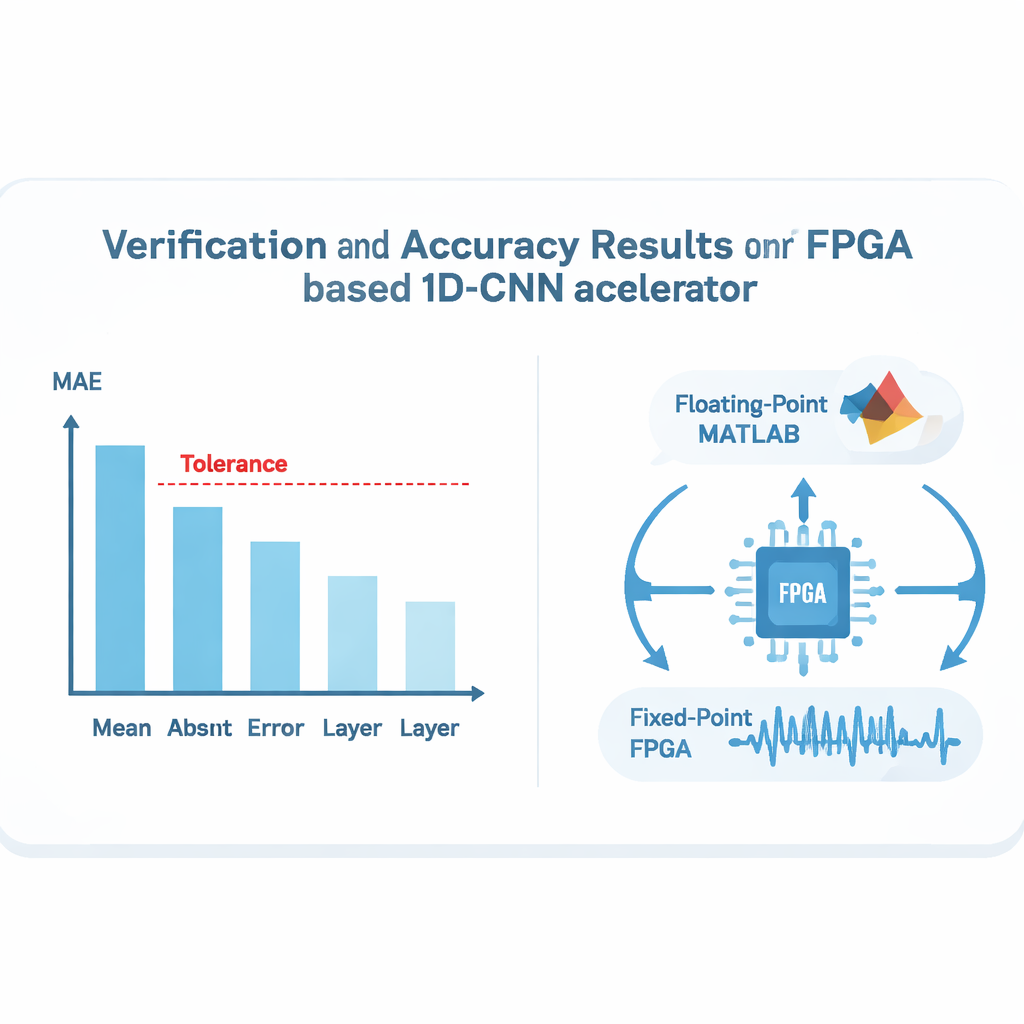

Da MATLAB a C++ fino all’FPGA, con i numeri tracciati

Invece di premere un pulsante di conversione automatica, la rete viene reimplementata manualmente in C++, seguendo la stessa organizzazione dei dati e gli stessi passaggi matematici di MATLAB. Questo codice C++ viene quindi utilizzato con uno strumento di high‑level synthesis per generare l’hardware che gira su una scheda FPGA PYNQ‑Z1. In ogni fase—MATLAB, C++ e FPGA—gli output dei layer sono confrontati con i golden outputs memorizzati usando una metrica semplice: l’errore assoluto medio, che misura la differenza numerica media tra due insiemi di risultati. Lo studio definisce una tolleranza rigorosa: tutti i layer devono restare sotto un errore di 1.5×10⁻³. Su migliaia di campioni ECG, ogni layer testato rispetta questo obiettivo, e l’accuratezza finale di classificazione resta quasi invariata: circa 98.3–98.4% in MATLAB e C++, e solo circa 0.2 punti percentuali in meno sull’FPGA, una differenza coerente con gli effetti attesi dell’uso di numeri a virgola fissa più corti nell’hardware.

Velocizzare l’hardware senza compromettere la matematica

Una volta garantita la correttezza, il progetto viene ottimizzato per la velocità. Le parti più impegnative della rete—i layer convoluzionali—vengono mappate sulla logica programmabile dell’FPGA, usando aritmetica a virgola fissa per efficienza, mentre compiti meno gravosi come il calcolo finale della softmax vengono eseguiti sul processore integrato del chip con numeri in virgola mobile standard. Tecniche come il pipelining dei loop, lo unrolling e la frammentazione accurata della memoria in banchi paralleli permettono a diverse parti del calcolo e dei trasferimenti di dati di funzionare in parallelo. Una versione hardware ottimizzata elabora una finestra di battito in circa 1.7 millisecondi e rientra comodamente nei limiti di risorse e consumo dell’FPGA, mantenendo nel contempo il comportamento numerico layer‑wise del modello MATLAB originale.

Cosa significa questo per i futuri dispositivi intelligenti

Per i non specialisti, il messaggio chiave è che oggi è possibile non solo accelerare su un chip a basso consumo un sofisticato classificatore di ritmi cardiaci basato su MATLAB, ma anche dimostrare che il funzionamento interno del chip corrisponde da vicino al modello software di riferimento su ogni layer. Invece di inseguire la velocità a scapito dell’affidabilità, questo approccio costruisce una chiara traccia di verifica dal codice MATLAB in virgola mobile all’hardware FPGA in virgola fissa. La stessa ricetta di verifica—salvare i golden outputs, confrontare gli errori layer‑wise con una soglia rigorosa e verificare l’accuratezza finale—può essere applicata ad altre reti neurali monodimensionali in ambiti come i monitor sanitari indossabili, sensori industriali e veicoli intelligenti, contribuendo a garantire che quando gli algoritmi lasciano il laboratorio e passano nei dispositivi, le loro decisioni restino affidabili.

Citazione: Bal, S. Towards the transformation of MATLAB models into FPGA-Based hardware accelerators. Sci Rep 16, 5027 (2026). https://doi.org/10.1038/s41598-026-36033-z

Parole chiave: acceleratori FPGA, reti neurali MATLAB, classificazione aritmie ECG, verifica hardware, deep learning a virgola fissa