Clear Sky Science · it

Progettazione di moltiplicatori approssimati a basso consumo e alta velocità che utilizzano compressori 4:2 in modalità corrente basati sulla tecnologia CNTFET

Immagini più nitide con meno energia

Ogni volta che il tuo telefono scatta una foto, riproduce un video o applica un filtro AI, esegue milioni di piccole moltiplicazioni. Calcolare tutto esattamente richiede energia e rallenta il sistema, mentre l'occhio umano spesso non percepisce piccoli errori numerici. Questo articolo mostra come «allentare» deliberatamente parte di quei calcoli usando un nuovo tipo di circuiteria, riducendo consumo e ritardo mantenendo le immagini visivamente indistinguibili dai risultati esatti.

Perché una matematica imperfetta può comunque apparire perfetta

Molte applicazioni moderne — come l'elaborazione delle immagini, il video e l'apprendimento automatico — tollerano naturalmente piccoli errori. Una lieve variazione nella luminosità di un pixel, o un piccolo spostamento nella risposta di un filtro, è di solito impercettibile. Gli autori sfruttano questo usando moltiplicatori approssimati: circuiti che scambiano un po' di precisione aritmetica per grandi risparmi in consumo, area del chip e velocità. Si concentrano su moltiplicatori 8×8, un blocco comune nell'elaborazione digitale dei segnali, e valutano non solo l'errore numerico, ma anche come queste approssimazioni influenzano la qualità finale dell'immagine utilizzando metriche standard come il rapporto segnale‑rumore di picco (PSNR) e la similarità strutturale (MSSIM).

Un nuovo tipo di blocco di base per moltiplicatori veloci

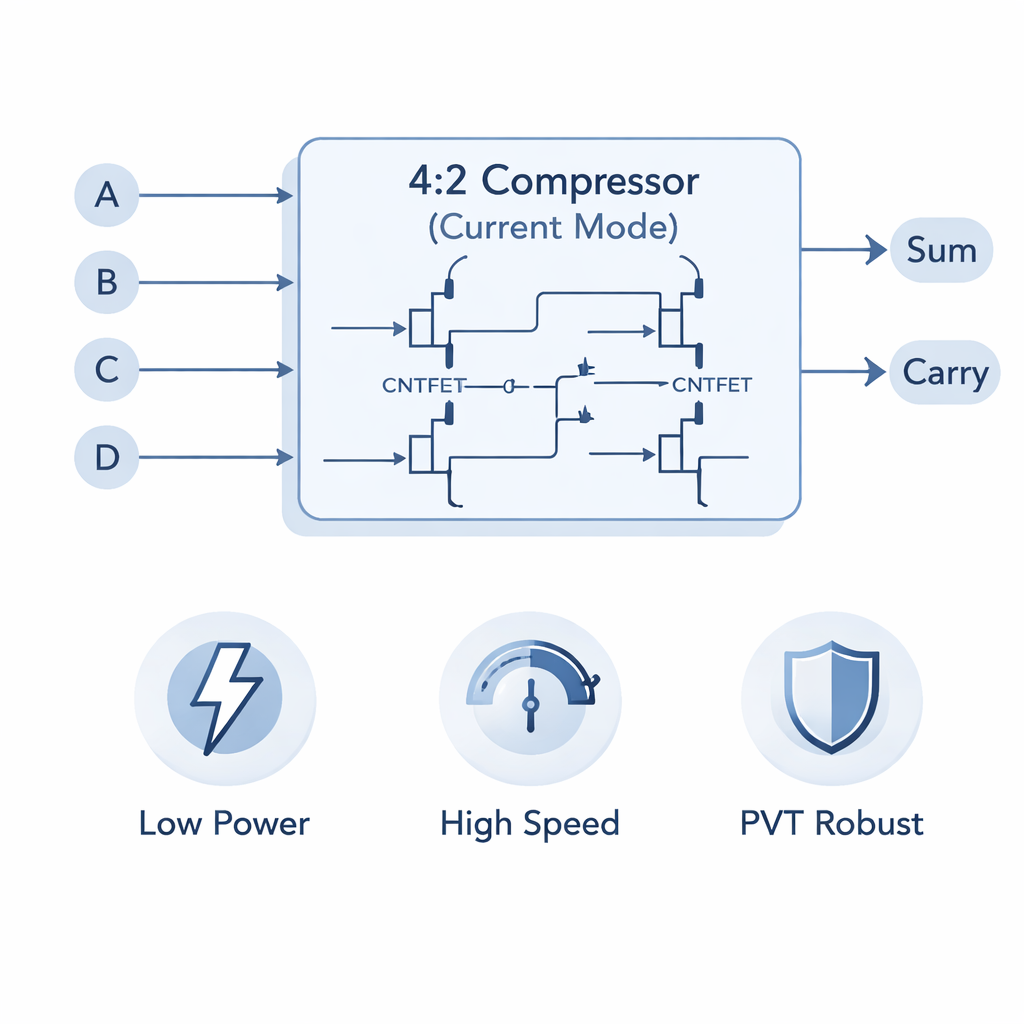

Il cuore del progetto è un componente chiamato compressore 4:2, che riduce quattro bit di ingresso e un ingresso di riporto in due uscite, «somma» e «riporto». I compressori tradizionali usano transistor CMOS o FinFET in modalità tensione, che diventano difficili da scalare a dimensioni molto ridotte. Questo lavoro combina invece logica in modalità corrente con transistor a effetto di campo a nanotubi di carbonio (CNTFET) a 7 nanometri. Vedendo l'informazione come correnti anziché solo tensioni, i circuiti possono sommare correnti direttamente senza complesse reti di rilevamento di soglia. I CNTFET, la cui tensione di soglia può essere regolata variando il diametro del nanotubo, permettono di costruire porte majority, XOR e altre porte di base con pochissimi transistor, alti margini di rumore e bassa energia per operazione.

Sei varianti di compressori «abbastanza buoni»

Gli autori propongono sei nuovi design di compressori 4:2. Quattro sono compressori approssimati a modalità singola, ciascuno esplorando un diverso modo di semplificare la logica interna per ridurre consumo, ritardo o errore. Altri due sono compressori a doppia funzione che possono passare tra comportamento esatto e approssimato tramite power gating, così da avere attiva solo la parte necessaria del circuito. Tra queste opzioni misurano con cura la distanza d'errore (quanto un'uscita può deviare dal valore perfetto), quanto spesso le uscite restano esatte e quanto i circuiti sono robusti rispetto a variazioni di processo, tensione e temperatura. Grazie all'approccio in modalità corrente con CNTFET, i nuovi compressori sono dal 30% al 50% meno sensibili a tali variazioni rispetto a design CMOS o FinFET comparabili, consumando allo stesso tempo solo circa 12–25 microwatt con ritardi interni sub‑nanosecondo.

Due design di moltiplicatori per immagini e AI

Utilizzando questi compressori, il gruppo costruisce due moltiplicatori Dadda 8×8. Il primo tipo usa compressori approssimati in ogni colonna, massimizzando il risparmio energetico. Il secondo adotta un approccio più selettivo: elimina completamente le quattro colonne di uscita meno significative (troncamento), utilizza compressori approssimati nelle colonne intermedie e mantiene compressori esatti nelle colonne più significative dove gli errori sarebbero visivamente evidenti. Simulazioni in HSPICE e MATLAB mostrano che, per la migliore configurazione, il consumo scende a circa 0,52 mW, la latenza a 1,88 ns e il prodotto potenza‑ritardo a 0,97 pJ — miglioramenti significativi rispetto ai precedenti moltiplicatori approssimati.

Cosa significa per le immagini reali

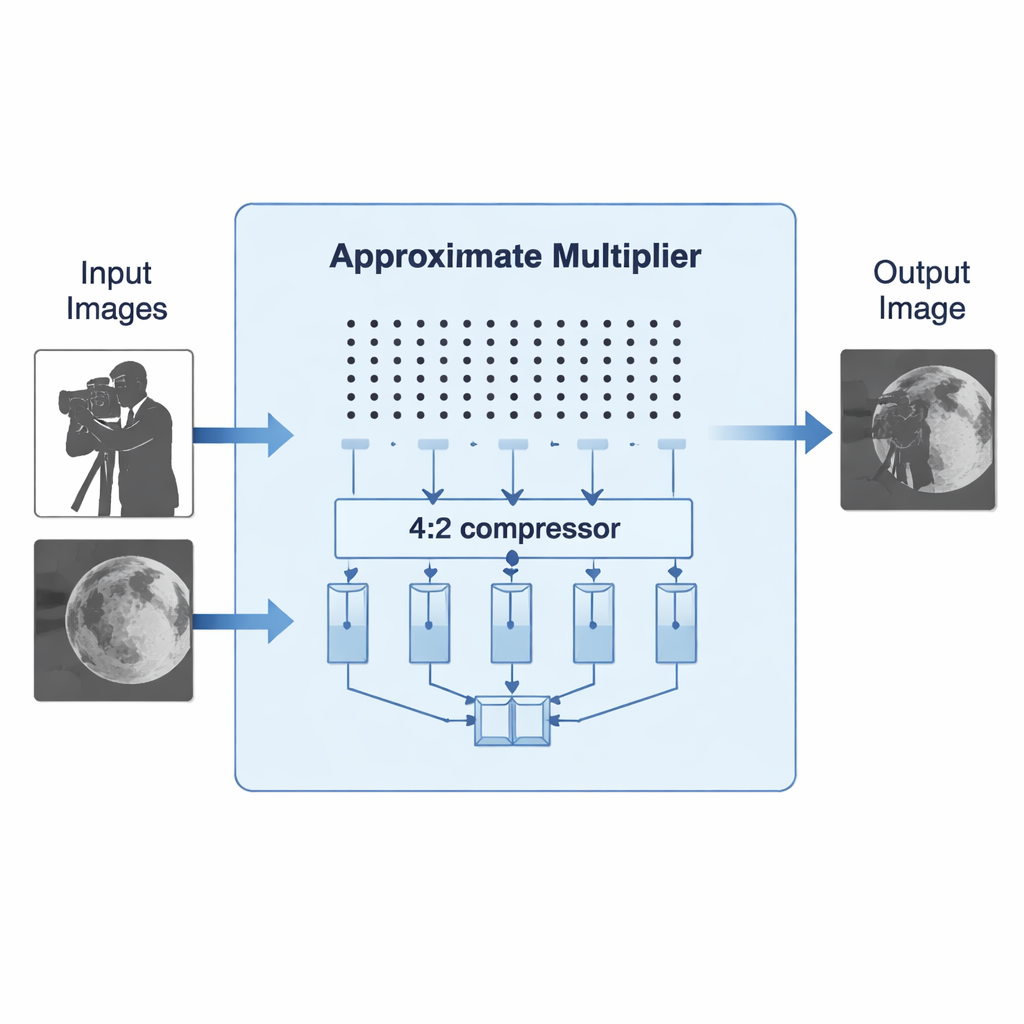

Per verificare se questi risparmi contano nella pratica, gli autori eseguono compiti standard di elaborazione immagini come la moltiplicazione di due immagini di riferimento (i classici «cameraman» e «moon») e l'accentuazione dei dettagli. Confrontano le immagini prodotte da moltiplicatori esatti e dai loro design approssimati. Nonostante errori aritmetici interni fino a ±2 in alcuni casi, il miglior moltiplicatore proposto aumenta la similarità strutturale (MSSIM) da circa il 60% nei design approssimati precedenti a circa il 97%, e migliora il PSNR del 15–20%. Visivamente, le immagini restano nitide e dettagliate, mentre l'hardware sottostante consuma molto meno e lavora più velocemente, rendendo questo approccio interessante per fotocamere a basso consumo, sistemi di visione portatili e dispositivi AI periferici dove la durata della batteria e la velocità contano più dell'aritmetica perfetta.

Citazione: Foroutan, P., Navi, K. Design of low power and high speed approximate multipliers utilizing current mode 4 to 2 compressors based on CNTFET technology. Sci Rep 16, 4834 (2026). https://doi.org/10.1038/s41598-026-35104-5

Parole chiave: moltiplicatori approssimati, CNTFET, elaborazione delle immagini, circuiti a basso consumo, logica in modalità corrente