Clear Sky Science · it

Ottimizzazione delle prestazioni degli InSe-FET mediante materiali dielettrici high-k per applicazioni analogiche/RF

Elettronica più veloce e intelligente su un foglio minuscolo

I dispositivi moderni — dai telefoni 5G ai radar e agli scanner medici — dipendono da transistor in grado sia di amplificare segnali deboli sia di operare a velocità molto elevate. Questo articolo esplora come un materiale ultra‑sottile promettente, il seleniuro di indio (InSe), possa essere perfezionato per offrire un guadagno di segnale maggiore per i futuri circuiti analogici e a radiofrequenza (RF), come quelli usati per comunicazioni wireless e rilevamento. Scegliendo con cura lo strato isolante che si trova accanto al canale attivo del transistor, gli autori mostrano come aumentare le prestazioni bilanciando il compromesso inevitabile tra potenza e velocità.

Nuovi materiali oltre il silicio di tutti i giorni

Per decenni il silicio è stato il cavallo di battaglia dell’elettronica, ma gli ingegneri stanno ora guardando a materiali atomici che possono essere staccati in strati spessi poche unità atomiche. Questi materiali “2D” possono essere flessibili, trasparenti e molto efficienti nel trasportare carica elettrica. Il grafene è stato la prima stella di questa classe, ma poiché manca di un gap energetico fatica negli interruttori on‑off convenzionali. Materiali come il seleniuro di indio offrono un compromesso: mantengono i vantaggi degli strati 2D pur avendo un gap energetico che permette ai dispositivi di commutare nettamente e operare a bassa potenza. Studi precedenti hanno esaminato principalmente l’InSe per la logica digitale e il rilevamento della luce; questo lavoro sposta l’attenzione sul suo ruolo nei circuiti analogici e RF, dove l’amplificazione lineare e il comportamento ad alte frequenze contano più del semplice commutare binario.

Come cambiare lo strato invisibile altera il comportamento del dispositivo

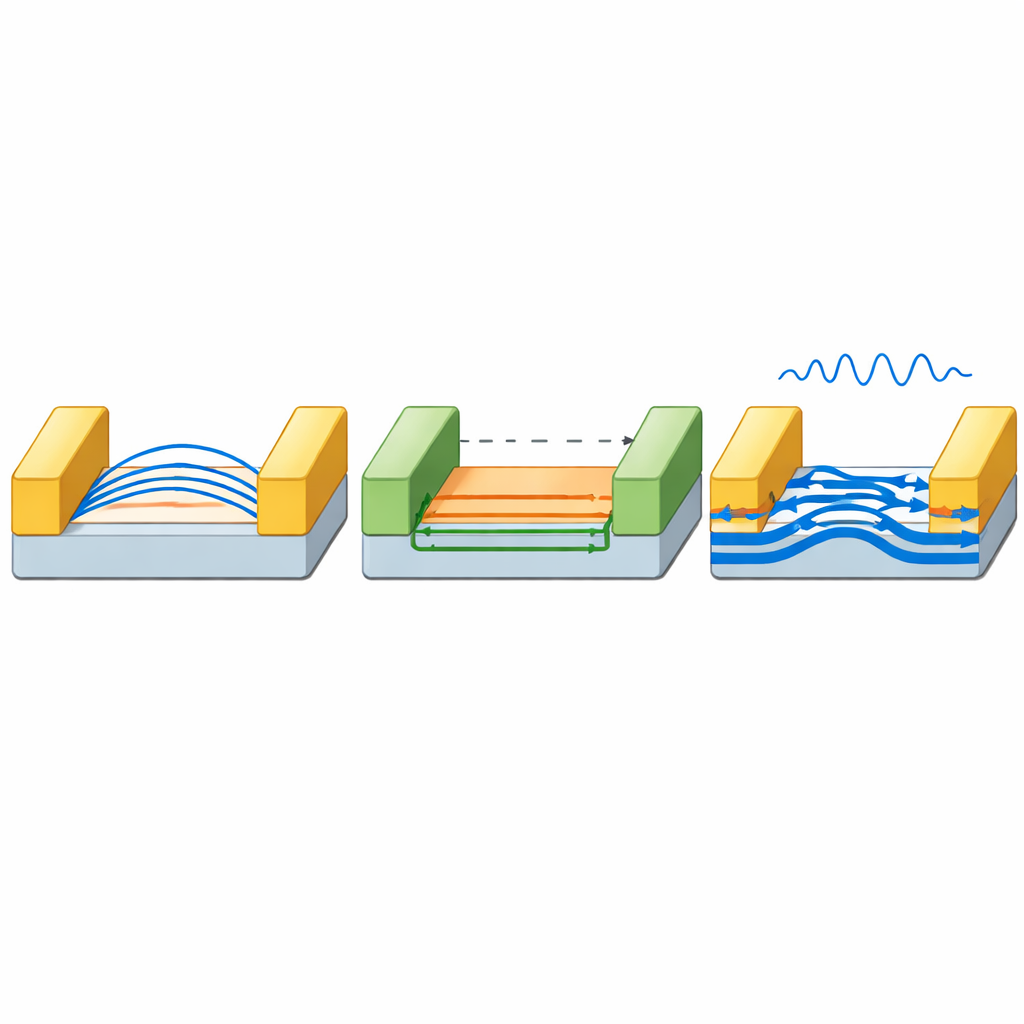

Ogni transistor a effetto di campo si basa su un gate che controlla un sottile canale di carica tramite uno strato isolante, o dielettrico, interposto. Qui gli autori simulano transistor InSe con diversi materiali dielettrici, da un ossido standard simile a quelli usati nei chip al silicio fino ai cosiddetti dielettrici high‑k che immagazzinano carica elettrica in modo più efficace. Utilizzando modelli computerizzati a livello quantistico dettagliati, calcolano come gli elettroni si muovono attraverso una striscia di InSe su scala nanometrica quando la tensione del gate varia. All’aumentare della costante dielettrica, il campo elettrico generato dal gate “afferra” il canale con più forza, attirando più carica in movimento e abbassando la barriera energetica che gli elettroni devono superare. Ciò porta a una corrente più alta quando il dispositivo è acceso e a una separazione più netta tra gli stati on e off, risultato positivo sia per l’uso digitale sia per quello analogico.

Trasformare il miglior controllo in un guadagno di segnale maggiore

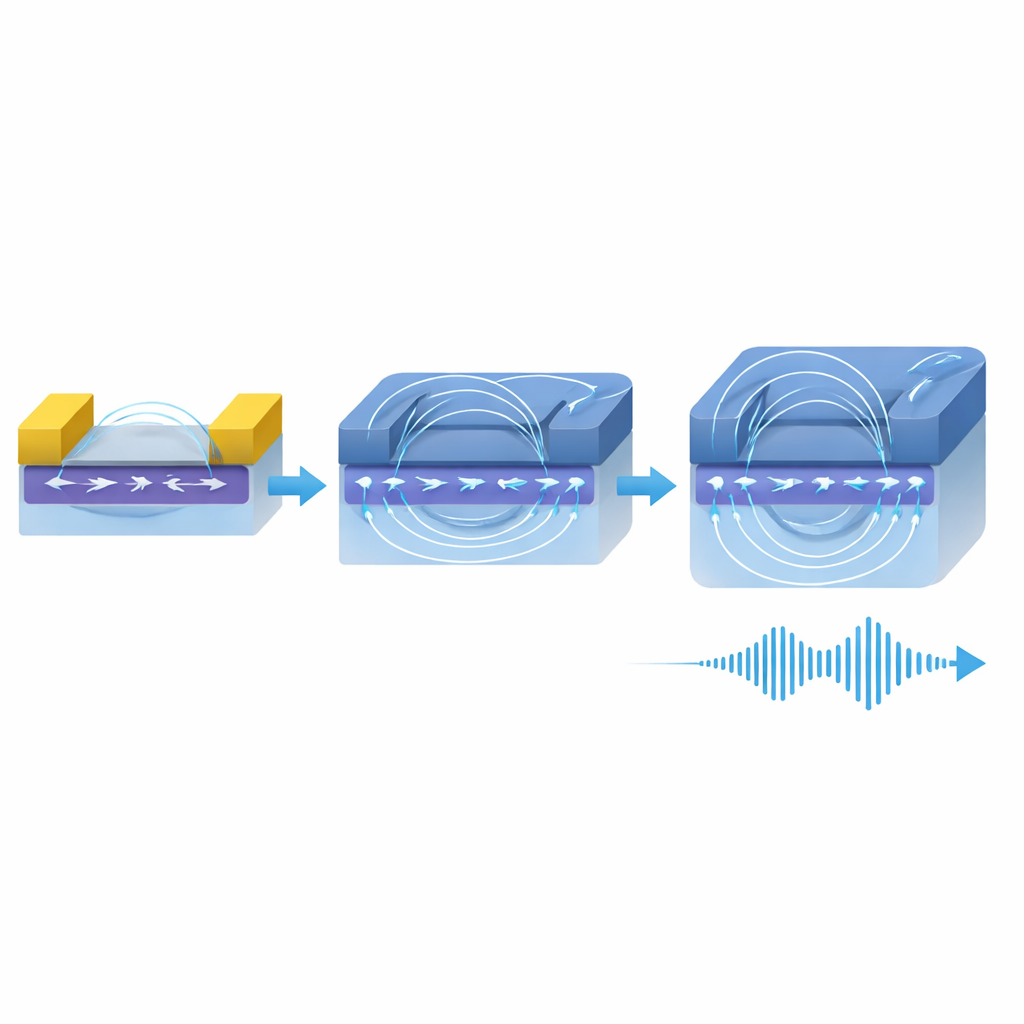

Il vero fulcro dello studio sono le grandezze di merito per analogico e RF — parametri che descrivono quanto bene un transistor può amplificare segnali e a quale costo in termini di potenza o larghezza di banda. Con materiali high‑k, i dispositivi InSe simulati mostrano quasi il doppio della transconduttanza, una misura di quanto efficacemente variazioni di tensione in ingresso si trasformano in variazioni di corrente in uscita. Questo, a sua volta, aumenta il guadagno intrinseco, che combina la transconduttanza con la capacità del dispositivo di mantenere stabile la tensione di uscita. Gli autori esaminano anche misure composite che fondono guadagno, velocità ed efficienza — ad esempio quanto guadagno si può ottenere a una data frequenza operativa o quanto efficacemente ogni unità di corrente viene impiegata per ottenere amplificazione. In tutti questi casi, i dielettrici a più alto k forniscono vantaggi evidenti, talvolta migliorando le metriche di prestazione del 70 fino a oltre il 150 percento.

Il costo del colpo in più: un impatto sulla massima velocità

Non esiste però un pasto gratis. Lo stesso dielettrico high‑k che rafforza la presa del gate sul canale aumenta anche la capacità del dispositivo, il che significa che immagazzina più carica che deve essere spostata ogni volta che il transistor commuta. Pur migliorando la corrente di pilotaggio e il guadagno, questa carica aggiuntiva rallenta il ritmo ultimo a cui il transistor può operare, riducendo leggermente la frequenza di cut‑off — il punto in cui non fornisce più un’amplificazione utile. Nelle simulazioni, questa metrica di velocità cala di circa il 10 percento per il caso con k più elevato rispetto all’ossido convenzionale. Gli autori evidenziano questo come un compromesso di progetto: gli ingegneri possono sintonizzare la scelta del dielettrico a seconda che sia più importante un guadagno elevato, la frequenza massima o un equilibrio ottimale tra i due.

Cosa significa per i futuri chip wireless e di sensing

In termini semplici, lo studio mostra che sostituendo lo strato isolante sottile in un transistor InSe con un materiale che trattiene meglio la carica, gli ingegneri possono costruire interruttori minuscoli che amplificano i segnali molto più efficacemente, seppure con una modesta riduzione della velocità massima. Ciò rende i dispositivi InSe con dielettrici high‑k particolarmente interessanti per circuiti analogici e RF a bassa tensione, dove un guadagno pulito e l’efficienza energetica contano più che spingersi verso le frequenze assolute più alte. Con l’aumentare del realismo nelle simulazioni — includendo effetti come la dispersione e i difetti — e con il miglioramento delle tecniche di fabbricazione, tali transistor su misura in materiali 2D potrebbero sostenere una nuova generazione di tecnologie di comunicazione e sensing flessibili e a basso consumo.

Citazione: Ahmad, M.A., Imam, M., Mech, B.C. et al. Performance optimization of InSe-FETs using high-k dielectric materials for analog/RF applications. Sci Rep 16, 9573 (2026). https://doi.org/10.1038/s41598-025-21242-9

Parole chiave: transistor a seleniuro di indio, dielettrici high-k, elettronica analogica RF, dispositivi semiconduttori 2D, simulazione nanoelettronica