Clear Sky Science · he

חישוב יעיל ועיצוב ארכיטקטורת מכפיל וידיק מהיר בדיוק כפול

מדוע חישובים מהירים יותר משמעותיים

בכל פעם שאתם צופים בוידאו בזרם חי, משתמשים בניווט בטלפון או מאפשרים למערכת בינה מלאכותית לנתח תמונות רפואיות, חומרה ממומחית מבצעת בחשאי מיליארדי חישובים זעירים בשנייה. חלק גדול מהפעולות הללו הן כפל של מספרים בפורמט נקודה צפה, הדרך הסטנדרטית שבאמצעותה מחשבים מייצגים ערכים ממשיים כמו 3.14159. מאמר זה חוקר שיטה חכמה יותר לבניית אחד מהרכיבים המרכזיים האלה: מכפיל מהיר ויעיל באנרגיה שמושפע מרעיונות במתמטיקה הוודית הקדומה כדי לשפר חומרה דיגיטלית מודרנית.

מטכניקות מתמטיות עתיקות לשבבים מודרניים

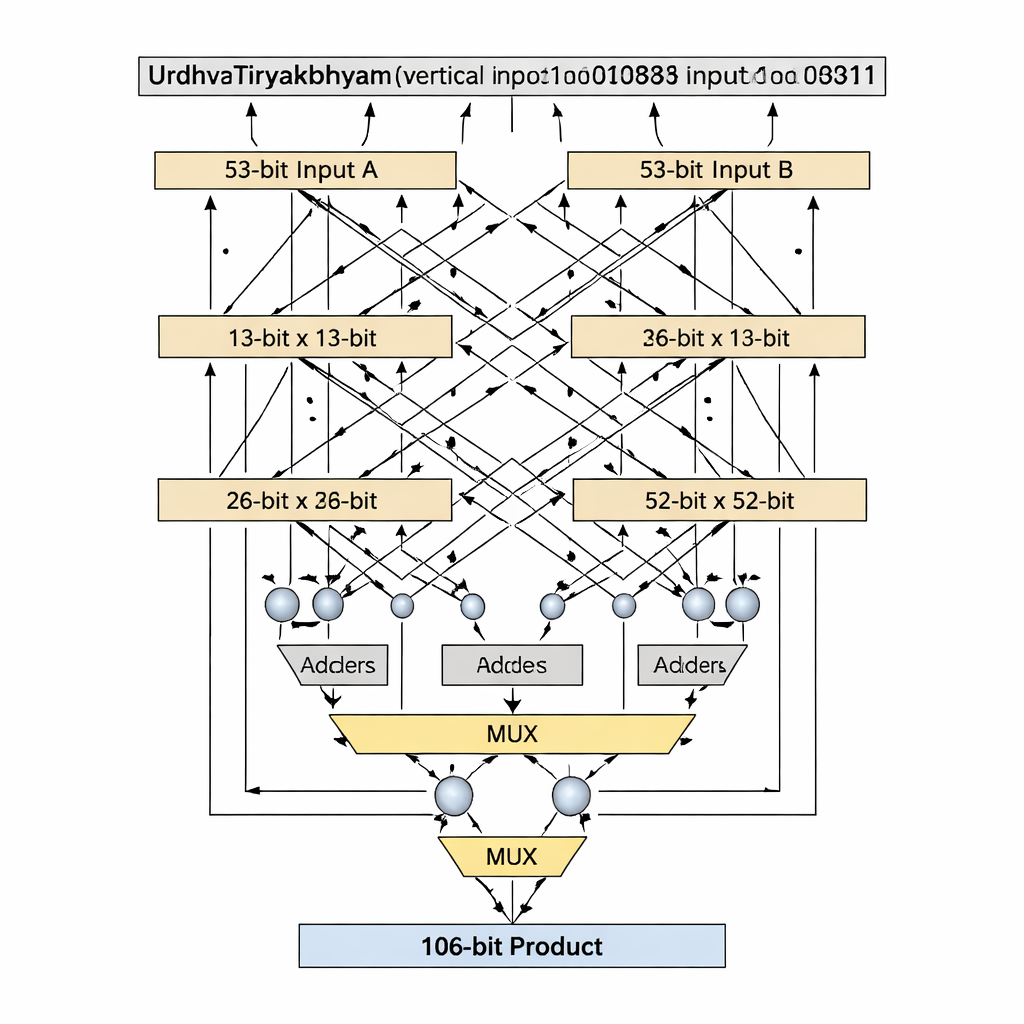

אריתמטיקה בנקודה צפה מהווה בסיס לעיבוד אותות דיגיטלי, עיבוד תמונה, תקשורת ומאיצי למידה עמוקה. מכפילים סטנדרטיים חייבים לטפל במילים בינאריות רחבות — 64 סיביות לדיוק כפול — ולעשות זאת במהירות מבלי לבזבז שטח שבב או אנרגיה. גישות מסורתיות, כגון בות׳, קאראצ׳ובה ומכפילים מערכיים, מאזנות בין מהירות, גודל חומרה ומורכבות עיצוב. המתמטיקה הוודית, מערכת של 16 כללים אריתמטיים קלאסיים שהופיעו בהודו, כוללת שיטת כפל הנקראת Urdhva Tiryakbhyam, או "אנכי ומאונך". היא יוצרת מכפלות חלקיות באופן מקבילי מאוד, מה שיכול לצמצם את מספר השלבים הביניים ואת החומרה הנדרשת. חוקרים התאימו לאחרונה רעיונות אלו למעגלים דיגיטליים, אך עיצובים קיימים עדיין נושאים עליהם עלויות שימוש כשהם מיושמים עבור פעולות נקודה צפה בדיוק כפול.

מה מיוחד במכפיל החדש הזה

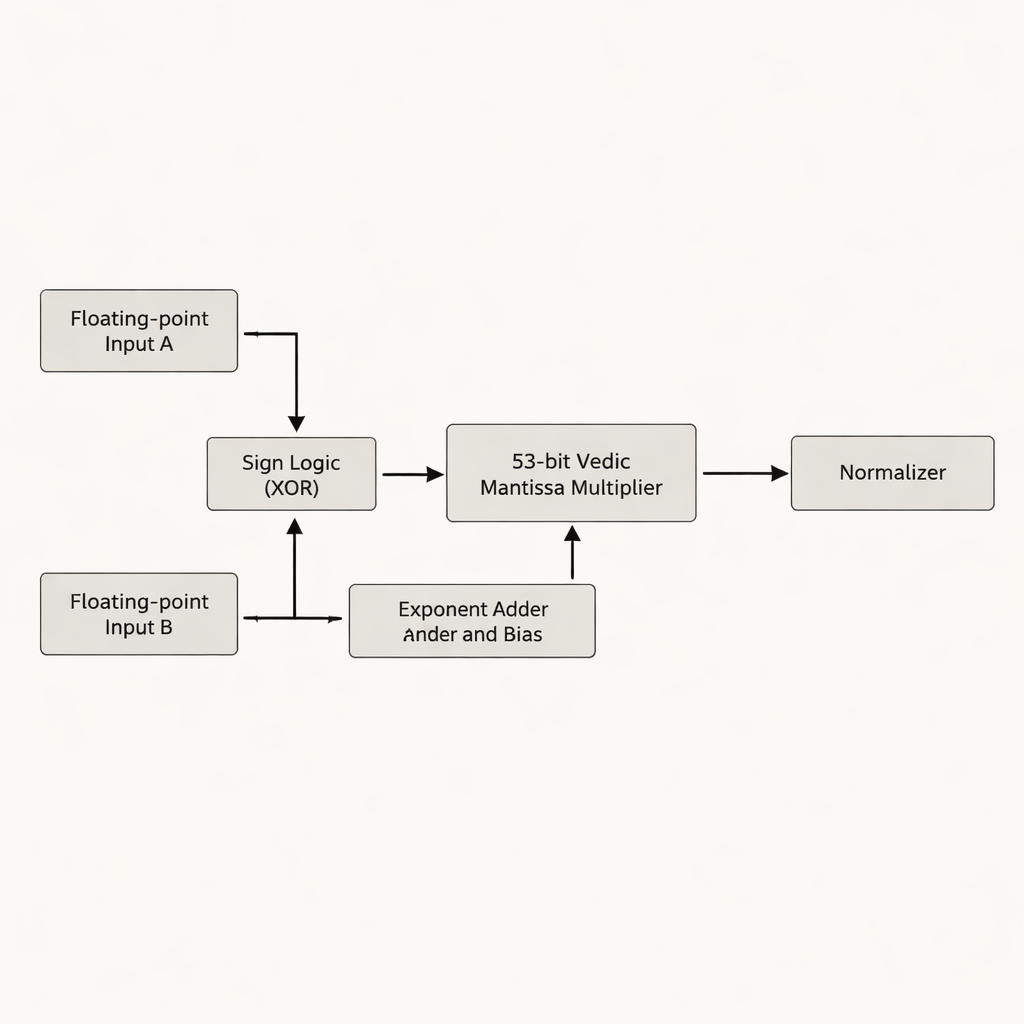

המחברים מציעים מכפיל נקודה צפה בדיוק כפול שמתמקד במנטיסה — החלק במספר בנקודה צפה שמכיל את רוב הספרות המשמעותיות. במקום להשלים את המנטיסה בת 52 סיביות ל־54 סיביות, כפי שעושים עיצובים קודמים רבים, הם עובדים עם המנטיסה היעילה האמיתית של 53 סיביות, ובכך נמנעים מביטול "מרחב לבן" שצורך אחסון וחיווט מיותר בשבב. ליבת העיצוב היא מכפיל וידיק של 53 סיביות המבוסס על Urdhva Tiryakbhyam, המאורגן בהיררכיה של בלוקים קטנים יותר: יחידות של 3 סיביות בונות יחידות של 6 סיביות, שמרכיבות 12, 13, 26 ו־52 סיביות, הכול משולב לשלב הסופי של 53 סיביות. הארכיטקטורה מפרידה את העבודה לשלוש פאזות עיקריות — חישוב סימן, חיבור ואיזון מעריך, וכפל מנטיסה ואחריו נירמול — בהתאמה לסטנדרט IEEE‑754 תוך קיצוץ במעגלים מיותרים.

בלוקים בגודל ראשוני לחומרה נקייה יותר

חידוש מרכזי הוא האופן שבו העיצוב מתמודד עם רוחבי ביט שהם מספרים ראשוניים, כגון 13 ו־53, שאינם מתחלקים באופן חלק לבלוקים שווים. פירוקי וידיק סטנדרטיים מניחים קלטים מחולקים שווה, אך זה הופך למגושם או מבזבז עבור אורכי ראשוניים. המחברים מציעים אלגוריתם "ביט-ראשוני" שחוזר באופן חכם על מכפיל וידיק קטן יותר בגודל (n−1), בתוספת סכמים, מולטיפלקסרים ושער לוגי יחיד, כדי לדמות מכפיל בגודל n ללא השטחה. עבור שלב של 13 סיביות, הקלטים נחלקים לחתיכות של 1 סיבית ו־12 סיביות; יוצרים מכפלות חלקיות באמצעות מכפיל וידיק של 12 סיביות, בחירה מותנית (באמצעות מולטיפלקסרים) בהתבסס על הביטים החשובים ביותר ומספר קטן של סכמים. הדפוס הזה מתדרג ל־53 סיביות עם ליבת 52 סיביות. פירוק מותאם זה מקצר את הנתיב הקריטי — שרשרת הלוגיקה הארוכה ביותר שעל אות לעבור — תוך שמירה על מספר נמוך של אלמנטים לוגיים.

רווחים מדודים במהירות, בגודל ובצריכת חשמל

העיצוב תואר בשפת תיאור חומרה Verilog ומומש על FPGA של Xilinx Zynq באמצעות כלי Vivado. לאורך מכפילים וידיק של 13, 26, 52, 53 ו־64 סיביות, יחידת ה־53 סיביות המוצעת מציגה איזון נאות בין עיכוב, שימוש בלוגיקה (טבלאות חיפוש ומחברים I/O) והספק מוערך. בהשוואה למכפילים קודם לכן בדיוק כפול המבוססים על בות׳, קאראצ׳ובה וסידורים וידיים אחרים, הארכיטקטורה החדשה מקטינה באופן משמעותי את העיכוב במקרה הגרוע ואת כמות משאבי ה‑FPGA הנדרשים, מבלי להוסיף מורכבות למעגלי הנקודה הצפה הסובבים. מאחר שכפל המנטיסה מהיר יותר ועומק הלוגיקה רדוד יותר, פעילות ההחלפה פוחתת, מה שמצביע על מוצר עיכוב‑הספק טוב יותר אף על פי שהשוואות הספק ישירות בין טכנולוגיות קשות לביצוע.

השפעות על בינה מלאכותית ועיבוד אותות

כדי לבחון את העיצוב בעומס עבודה אמיתי, המחברים שילבו את מכפיל הווידיק בדיוק כפול במנוע הקונבולוציה של רשת עצבית קונבולוציונלית, שם פעולות כפל‑ויאקום (multiply‑and‑accumulate) שולטות בזמן הריצה. החלפת מכפילים קונבנציונליים בתקן IEEE‑754 ובמכפילי וידיק קודמים בעיצוב החדש הקטינה את זמן הקונבולוציה, צמצמה את צריכת האנרגיה וקיצרה את זמן המסקנה, תוך שמירה על אותה דיוק סיווג. יתרונות דומים צפויים במשימות כבדות חישוב כמו פילטרים דיגיטליים, איתור קצוות וצינורות עיבוד תמונה רפואית, שם מכפילים מהירים יותר מעלים ישירות את התפוקה ויכולים לאפשר למכשירים לפעול קרירים יותר או על סוללות קטנות יותר.

מה זה אומר לטכנולוגיה היומיומית

במילים פשוטות, המאמר מראה שהשאלה של שאיבת רעיון כפל חכמה מהמתמטיקה הוודית והתאמתו במדויק לפורמטים בינאריים מודרניים יכולה להניב מכפיל שהוא קטן יותר, מהיר יותר ויעיל אנרגטית יותר לעומת עיצובים סטנדרטיים. בלוק בנייה משופר זה יכול להשתלב במעבדים, שבבי עיבוד אותות ומאיצי בינה מלאכותית, ולהוביל לניתוח נתונים מהיר יותר, למכשירים רגישים יותר ואפשרות לצריכת חשמל נמוכה יותר במערכות מחלונות סמארטפונים ועד סורקי רפואיים. המחברים מציינים גם כיוונים עתידיים, כולל לוגיקה הפיכה לאנרגיה נמוכה אף יותר ושילוב ביחידות עיבוד גדולות יותר, מה שמרמז שהנישא בין אריתמטיקה עתיקה לחומרה מודרנית רק בתחילתו.

ציטוט: Kumar, A.S., Sahitya, G., Kusuma, R. et al. Efficient computation and design of high speed double precision Vedic multiplier architecture. Sci Rep 16, 7364 (2026). https://doi.org/10.1038/s41598-026-38147-w

מילות מפתח: מכפיל וידיק, אריתמטיקה עם נקודה צפה, עיצוב FPGA, עיבוד אותות דיגיטלי, רשתות עצביות קונבולוציוניות