Clear Sky Science · fr

Cellule mémoire intégrée à gain basée sur des semi-conducteurs à oxyde : matériaux et stratégies d’intégration pour la prochaine génération de mémoire sur puce

Pourquoi une mémoire plus rapide et plus intelligente compte

Nos téléphones, ordinateurs portables et centres de données deviennent de plus en plus puissants, mais une limite de vitesse cachée subsiste : le déplacement des données entre le processeur et la mémoire. Cet article explore un nouveau type de mémoire sur puce qui pourrait atténuer ce « mur de la mémoire », rendant les ordinateurs futurs plus rapides et plus économes en énergie pour des tâches comme l’intelligence artificielle, l’informatique en nuage et les applications quotidiennes. En repensant la construction des cellules mémoire et les matériaux employés, les chercheurs visent à placer beaucoup plus de données à proximité du processeur tout en diminuant la consommation d’énergie et la dissipation thermique.

Le goulot d’étranglement à l’intérieur des ordinateurs modernes

Pendant des décennies, les performances des processeurs ont progressé beaucoup plus vite que la mémoire principale qui les alimente en données. Ce décalage, connu sous le nom de mur de la mémoire, signifie que des puces rapides restent souvent inactives en attendant des informations. Les concepteurs ont tenté d’atténuer ce goulot d’étranglement avec plusieurs niveaux de mémoire cache situés sur le processeur lui‑même. Les caches actuels reposent sur un type de mémoire appelé SRAM, très rapide mais volumineux et énergivore car chaque bit de données nécessite six transistors. Pour augmenter la capacité, les entreprises empilent des puces SRAM en trois dimensions ou intègrent de la DRAM embarquée sur la puce, mais la DRAM conventionnelle dépend encore de petits condensateurs difficiles à fabriquer à des échelles extrêmes et difficiles à intégrer aux circuits logiques standard.

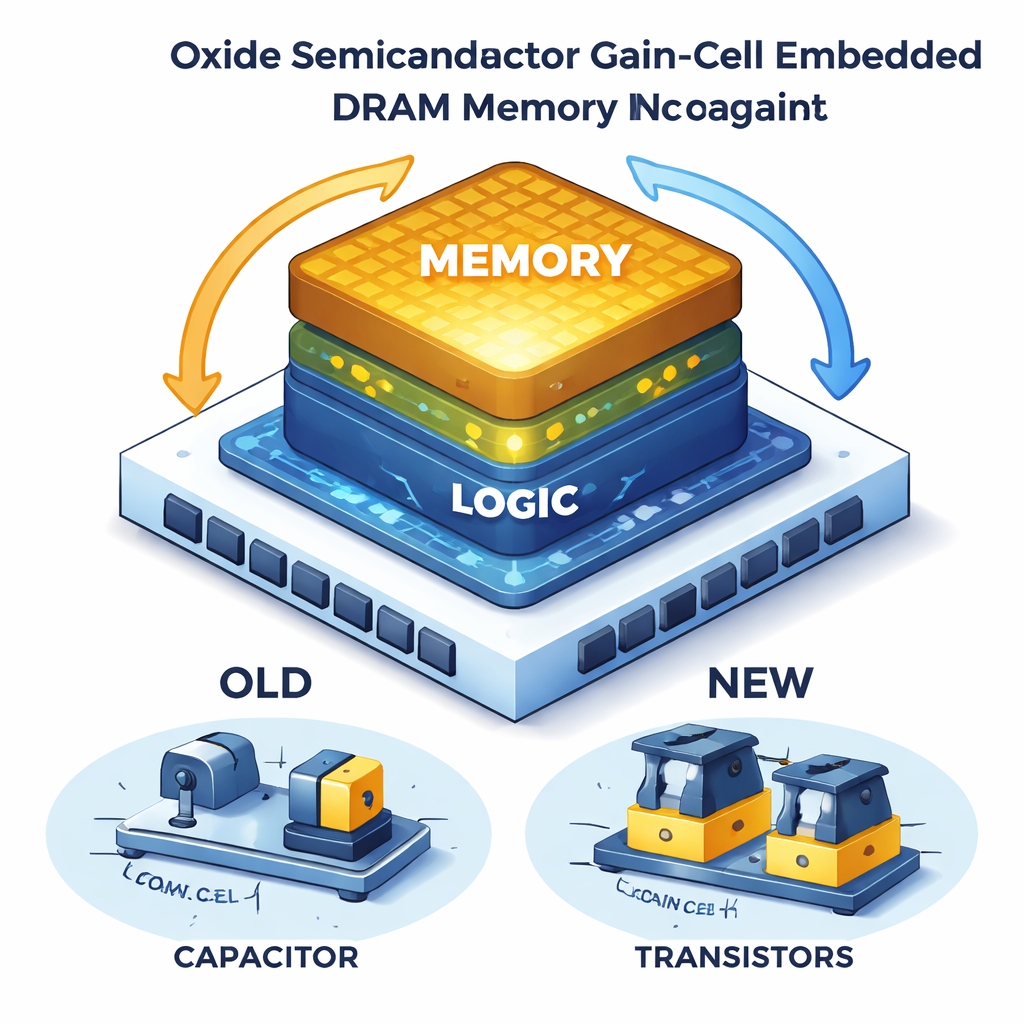

Une autre forme de cellule mémoire

L’article se concentre sur une alternative appelée DRAM intégrée à cellule à gain, ou GC‑eDRAM. Au lieu d’utiliser un condensateur séparé pour stocker une charge, une cellule à gain utilise uniquement des transistors pour conserver les données, simplifiant la structure et la rendant plus compatible avec la fabrication de puces standard. Cette conception s’adapte naturellement à l’empilement tridimensionnel au‑dessus des circuits logiques, promettant des agencements « mémoire‑sur‑logique » à haute densité. Un autre avantage est sa lecture non destructive : la lecture d’une valeur stockée ne l’épuise pas immédiatement, ce qui peut réduire la fréquence des opérations de rafraîchissement. Cependant, dans les versions traditionnelles en silicium, la charge stockée fuit en moins d’une milliseconde, si bien que des rafraîchissements fréquents gaspillent encore de l’énergie et limitent l’utilité.

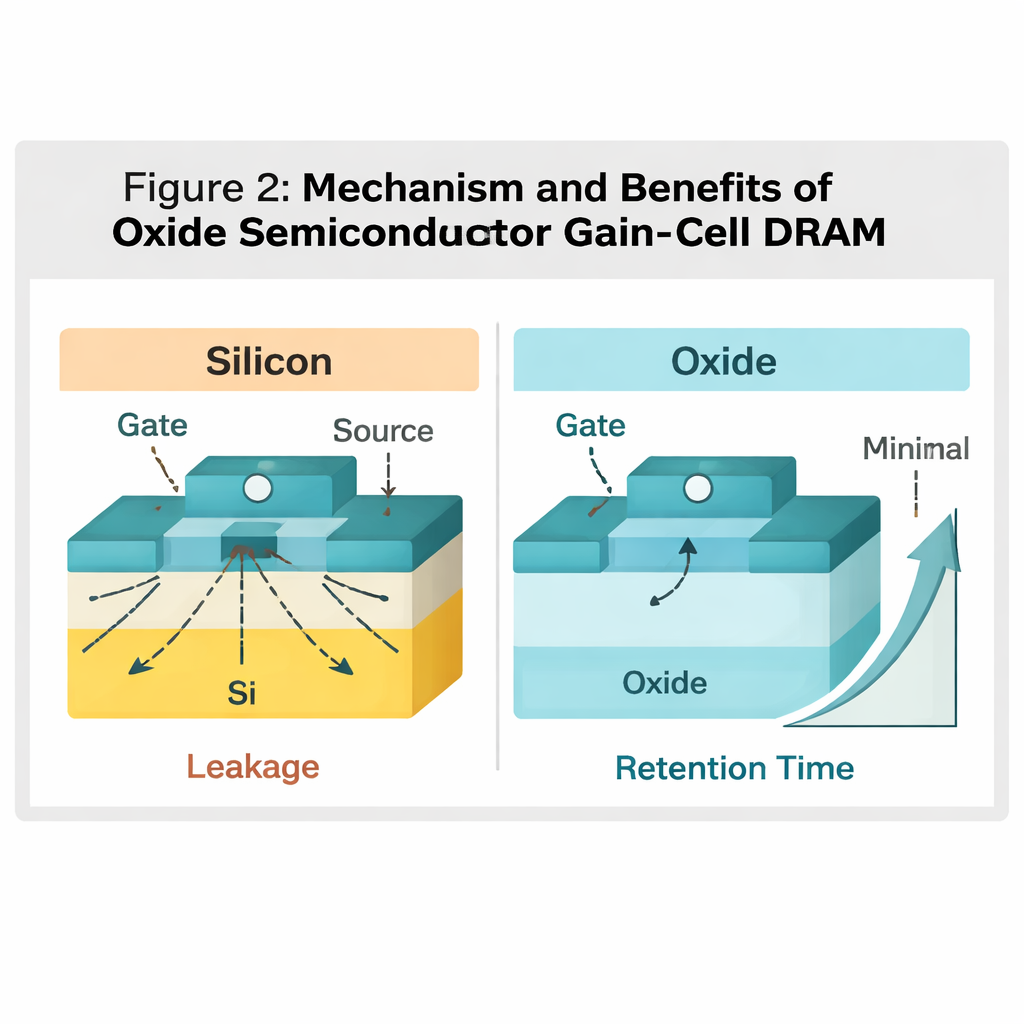

Semi‑conducteurs à oxyde : des commutateurs plus calmes et plus froids

Pour surmonter la fuite dans les cellules à gain, les auteurs mettent en avant les semi‑conducteurs à oxyde — des matériaux tels que l’oxyde d’indium, gallium et zinc (IGZO) et des composés apparentés — comme matériaux de canal pour les transistors. Ces oxydes possèdent une large bande interdite, ce qui supprime fortement le courant indésirable quand un transistor est supposé être coupé. Des expériences ont mesuré des courants de fuite si faibles qu’ils approchent les limites des appareils de test, et des prototypes de cellules à gain conservent désormais les données pendant plusieurs secondes, heures, voire plus d’un jour, comparé aux millièmes de seconde des conceptions en silicium. Fait crucial, ces oxydes peuvent être déposés à des températures relativement basses compatibles avec l’étape « back‑end » de la fabrication de puces, permettant aux ingénieurs de construire des couches mémoire denses directement au‑dessus de la logique en silicium existante sans l’endommager.

Construire vers le haut : empilements 3D et transistors microscopiques

À mesure que les puces continuent à rétrécir, réduire simplement la taille des transistors apporte de nouveaux problèmes, comme un contrôle médiocre du canal et une augmentation des fuites. L’article passe en revue des formes avancées de transistors qui entourent le canal par la grille (concepts gate‑all‑around et channel‑all‑around) pour maintenir un contrôle strict même à l’échelle nanométrique. En utilisant des semi‑conducteurs à oxyde dans ces structures multi‑grilles, les chercheurs ont démontré des canaux très courts, des fuites extrêmement faibles et une forte rétention des données tout en empilant plusieurs couches mémoire verticalement. Certains designs expérimentaux atteignent déjà ou dépassent l’efficacité de surface des meilleures cellules DRAM actuelles, suggérant que les puces futures pourraient héberger une capacité mémoire énorme dans une empreinte très réduite juste au‑dessus des cœurs de processeur.

Des matériaux de laboratoire à des produits fiables

Transformer ces dispositifs prometteurs en mémoire pratique exige un travail soigné d’ingénierie des matériaux. L’article décrit comment ajuster le mélange de métaux dans l’oxyde, contrôler la teneur en oxygène et cristalliser les films pour équilibrer haute vitesse et stabilité à long terme. Il couvre également les méthodes pour gérer les défauts, la contamination par l’hydrogène et les interfaces délicates entre les oxydes et les couches isolantes afin que les dispositifs restent stables sous chaleur et fonctionnement prolongé. Enfin, il aborde l’ingénierie des connexions métalliques pour que la résistance de contact ne compromette pas les bénéfices des nouveaux matériaux. Ensemble, ces stratégies visent à fournir une mémoire à la fois dense et suffisamment fiable pour une fabrication à grande échelle.

Ce que cela signifie pour l’informatique de tous les jours

Les auteurs concluent que les mémoires à cellule à gain basées sur des semi‑conducteurs à oxyde pourraient remodeler la façon dont les puces sont construites à l’avenir. En combinant des cellules mémoire minuscules et à faible fuite avec un empilement 3D au‑dessus des circuits logiques, les concepteurs pourraient placer beaucoup plus de mémoire rapide à côté du processeur tout en maîtrisant la consommation d’énergie. Cela atténuerait le mur de la mémoire, aidant tout, des accélérateurs IA aux serveurs cloud en passant par les appareils personnels, à fonctionner plus vite et plus efficacement. Bien que des défis subsistent en matière de fiabilité, d’uniformité de fabrication et d’intégration à l’échelle de la puce, le travail présenté ici trace une voie claire vers des systèmes informatiques plus compacts, puissants et économes en énergie.

Citation: Chung, S.W., Yoon, S.H. & Jeong, J.K. Oxide semiconductor gain cell-embedded memory: materials and integration strategies for next generation on-chip memory. Commun Eng 5, 39 (2026). https://doi.org/10.1038/s44172-026-00616-5

Mots-clés: mémoire sur puce, semi‑conducteurs à oxyde, mise à l’échelle de la DRAM, circuits intégrés 3D, matériel pour IA