Clear Sky Science · fr

Cartographier les dynamiques d’hystérésis variées dans des FETs MoS2 à l’échelle en utilisant la méthode universelle dérivée de la modélisation TCAD

Pourquoi les commutateurs minuscules ont besoin d’un comportement fiable

L’électronique moderne progresse vers des transistors toujours plus petits, et les matériaux bidimensionnels (2D) tels que le disulfure de molybdène (MoS2) sont des candidats de premier plan pour les puces du futur. Mais à mesure que ces commutateurs rétrécissent, leur comportement peut devenir incohérent : un même dispositif peut réagir différemment selon son utilisation immédiate précédente. Cet effet de mémoire, appelé hystérésis, est souvent écarté comme une nuisance mineure. Dans ce travail, les auteurs montrent que l’hystérésis recèle en réalité une mine d’informations sur les défauts cachés à l’intérieur des transistors avancés — et ils proposent une méthode universelle pour extraire ces informations.

Comment sont construits les transistors de prochaine génération

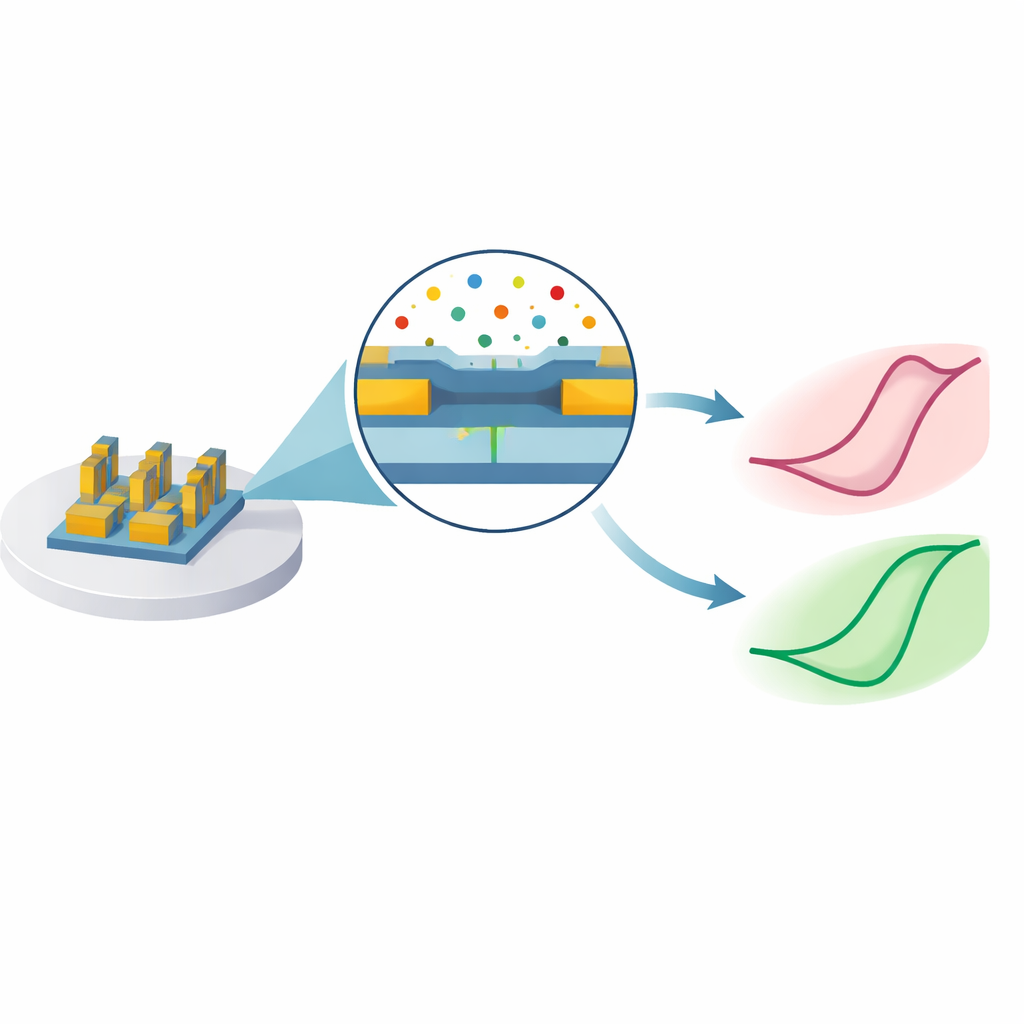

Les futurs transistors à effet de champ 2D utilisent une couche ultrafine de MoS2 comme canal où circule le courant, recouverte d’un oxyde isolant très mince comme l’oxyde d’hafnium (HfO2), avec une électrode de grille métallique par-dessus. Pour poursuivre la miniaturisation, cet oxyde doit être électriquement de l’ordre d’un nanomètre d’épaisseur, ce qui fait qu’un seul défaut à l’intérieur peut fortement perturber le canal. Ces défauts agissent comme de minuscules pièges pouvant retenir ou relâcher temporairement des charges électriques. Parce que les défauts peuvent se trouver à différentes profondeurs dans l’oxyde et interagir à la fois avec le canal et avec la grille, leur comportement collectif peut stabiliser ou déstabiliser le transistor de façons subtiles. Comprendre ce paysage de défauts est crucial si les transistors 2D veulent rivaliser avec la technologie silicium actuelle.

Pourquoi le transistor se souvient de son passé

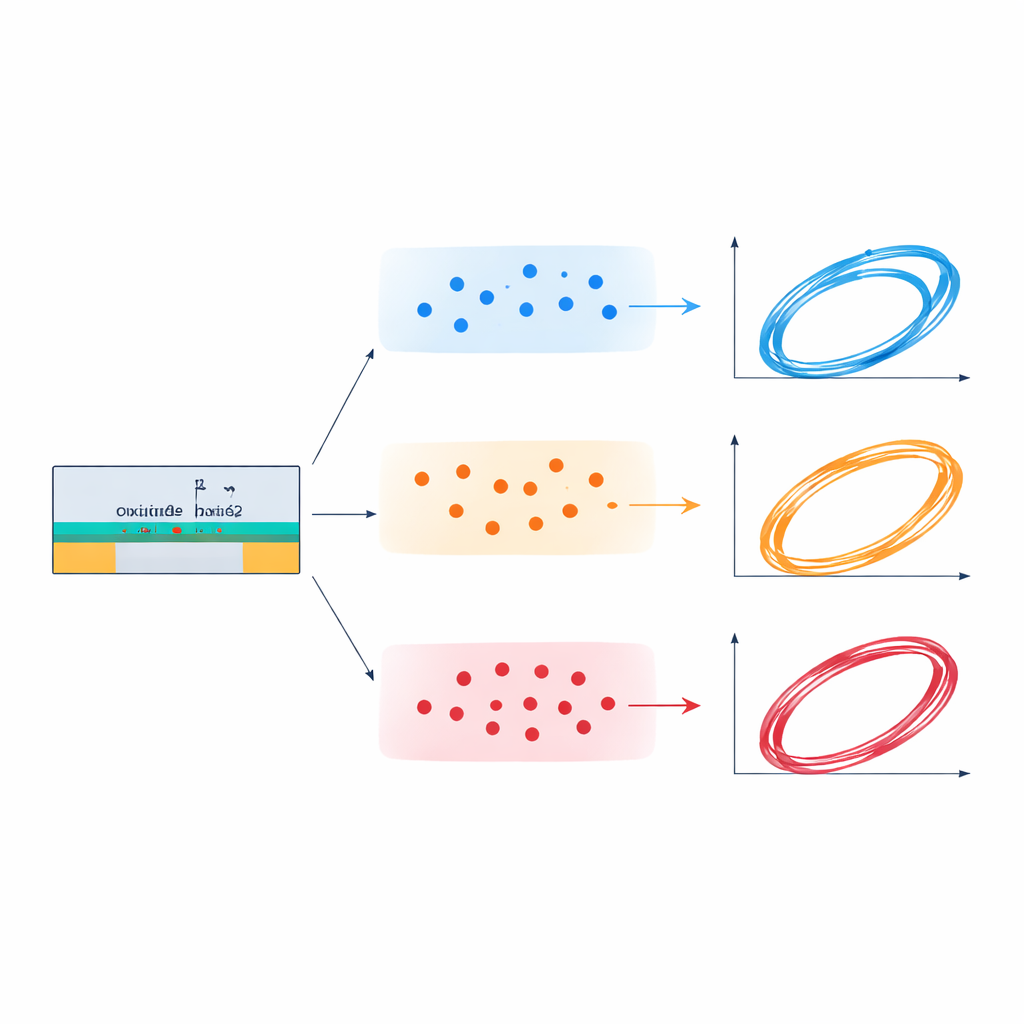

Lorsque les ingénieurs balayent la tension de grille vers le haut puis vers le bas et mesurent le courant, ils observent souvent que les balayages dans les deux sens ne coïncident pas. Cette boucle est l’hystérésis. Traditionnellement, les chercheurs mesurent la distance entre les deux courbes en un seul point de fonctionnement et appellent cela la largeur d’hystérésis, concluant souvent qu’elle est « faible » ou « négligeable ». Les auteurs soutiennent que cette pratique est trompeuse, surtout pour les dispositifs réduits où différents groupes de défauts peuvent contribuer de manière opposée. Selon la vitesse de mesure et le courant de fonctionnement, un même transistor peut présenter des boucles classiques dans le sens horaire, des boucles inversées dans le sens antihoraire, des transitions entre les deux, ou même une hystérésis quasi nulle lorsque des effets opposés se compensent.

Une carte universelle cachée dans les courbes

Pour démêler cette complexité, l’équipe utilise des simulations informatiques détaillées (TCAD) de transistors MoS2 à l’échelle nanométrique avec des populations de défauts contrôlées à différentes profondeurs dans l’oxyde. Ils proposent ensuite une méthode universelle de cartographie de l’hystérésis. Au lieu d’extraire un seul nombre, ils balayant la largeur d’hystérésis sur une large plage de courants — depuis juste au-dessus de l’état off jusqu’à près de l’état on — et pour des temps de balayage couvrant plusieurs ordres de grandeur. Cela produit des milliers de courbes montrant comment l’hystérésis évolue avec la vitesse de mesure à chaque courant. À partir de ces données, ils définissent des « fonctions universelles d’hystérésis » supérieure et inférieure qui encadrent tous les comportements possibles. Ces enveloppes révèlent clairement quels types de défauts sont actifs, s’ils interagissent principalement avec le canal ou avec la grille supérieure, et s’ils favorisent des boucles dans le sens horaire ou antihoraire.

Relier les boucles rapides à la dérive à long terme

Les mêmes défauts qui provoquent l’hystérésis entraînent également des dérives lentes du comportement du transistor sous contrainte prolongée, un problème connu sous le nom d’instabilité de polarisation-température (BTI). En simulant des expériences standard de contrainte puis de récupération, les auteurs relient des caractéristiques de leurs cartes d’hystérésis à des signatures BTI inhabituelles, telles qu’un déplacement apparemment négatif qui ne se relaxe ensuite que vers une valeur positive. Ils montrent que les pièges proches du canal tendent à causer des décalages lents et majoritairement permanents, tandis que les pièges plus proches de la grille entraînent des changements plus rapides mais en grande partie réversibles. Leur méthode peut s’appliquer non seulement aux dispositifs MoS2 simulés mais aussi aux données mesurées sur de vrais transistors MoS2 et WSe2 fabriqués en salles blanches de recherche et en lignes pilotes, y compris dans des cas où des ions errants dans l’oxyde participent au piégeage de charge.

Des données complexes à des recommandations pratiques

En transformant des boucles d’hystérésis confuses en cartes standardisées, ce travail propose un outil diagnostique puissant pour les technologies de transistors émergentes. La méthode fonctionne directement sur des jeux de données expérimentales et ne nécessite pas l’accès à des outils de simulation avancés, ce qui la rend largement utilisable en laboratoire. Pour les ingénieurs, le message clé est que l’hystérésis n’est pas seulement un défaut à minimiser, mais l’empreinte de problèmes de fiabilité sous-jacents. Décoder cette empreinte avec la méthode de cartographie proposée peut orienter le choix de meilleurs matériaux, des interfaces plus propres et des procédés plus intelligents, aidant les transistors 2D à passer de prototypes prometteurs à des éléments véritablement fiables de l’électronique future.

Citation: Lv, Y.Z., Wu, Y.H., Cai, H.H. et al. Mapping diverse hysteresis dynamics in scaled MoS2 FETs using the universal method derived from TCAD modeling. npj 2D Mater Appl 10, 35 (2026). https://doi.org/10.1038/s41699-026-00671-8

Mots-clés: transistors 2D, hystérésis, défauts d’oxyde, fiabilité des dispositifs, FETs MoS2