Clear Sky Science · fr

Vers la transformation de modèles MATLAB en accélérateurs matériels basés sur FPGA

Transformer des algorithmes de laboratoire en dispositifs réels

Beaucoup de percées médicales et d’ingénierie modernes naissent sous la forme de logiciels développés par des chercheurs, souvent dans des outils conviviaux comme MATLAB. Mais lorsque ces mêmes algorithmes doivent fonctionner en temps réel — par exemple pour repérer des anomalies dangereuses du rythme cardiaque à partir d’un électrocardiogramme (ECG) — ils exigent la rapidité et l’efficacité du matériel spécialisé. Cet article montre comment déplacer de façon fiable un réseau neuronal complexe de détection de battements cardiaques de MATLAB vers une puce spécialisée appelée FPGA, sans perdre la précision dont médecins et ingénieurs ont besoin.

Pourquoi réécrire du code pour des puces est si difficile

Les FPGA (Field-Programmable Gate Arrays) sont des puces reconfigurables prisées pour leur vitesse et leur faible consommation d’énergie. Traditionnellement, les programmer nécessitait des langages axés matériel comme VHDL ou Verilog, très éloignés du code mathématique et de traitement du signal de haut niveau que les scientifiques écrivent dans MATLAB. De nouveaux outils peuvent convertir automatiquement des algorithmes en descriptions matérielles, mais ils demandent souvent des ajustements manuels et se concentrent surtout sur la performance : la vitesse d’exécution et les ressources utilisées. Ce qui manquait, c’était une méthode claire pour prouver que le matériel fait exactement ce que faisait le logiciel original, couche par couche, nombre par nombre.

Un contrôle pas à pas pour chaque couche du réseau

L’auteur comble cette lacune en proposant un flux de travail axé sur la vérification pour un réseau neuronal convolutionnel unidimensionnel qui classe les battements cardiaques à partir de la célèbre base de données MIT-BIH Arrhythmia. Le réseau, construit dans MATLAB, analyse de courts extraits de données ECG et les affecte à l’un des cinq types de battements, incluant les rythmes normaux et plusieurs rythmes anormaux. Trois versions du réseau, de profondeurs différentes, sont entraînées sur les mêmes données. Après l’entraînement, les poids, biais et les sorties de chaque couche sur des signaux de test sont sauvegardés comme « sorties de référence » — un enregistrement numérique précis du comportement du modèle MATLAB.

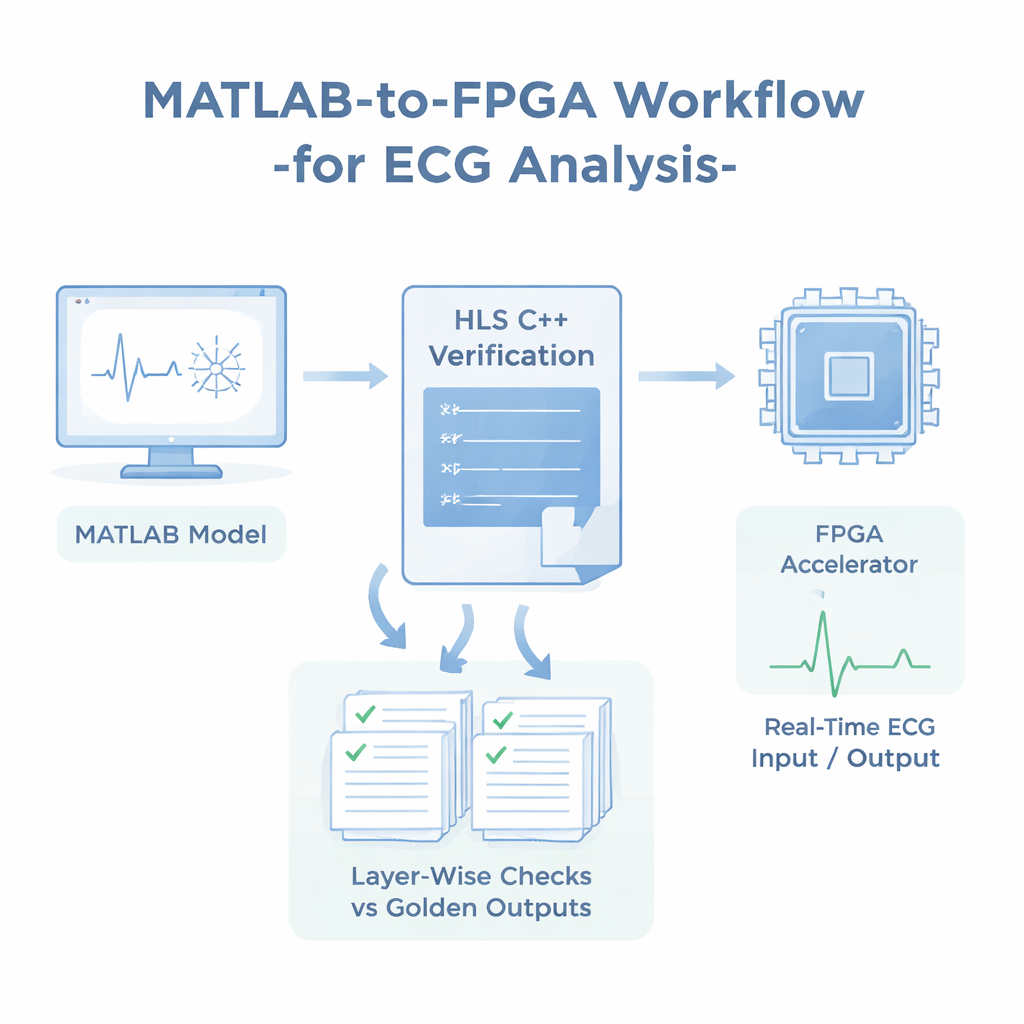

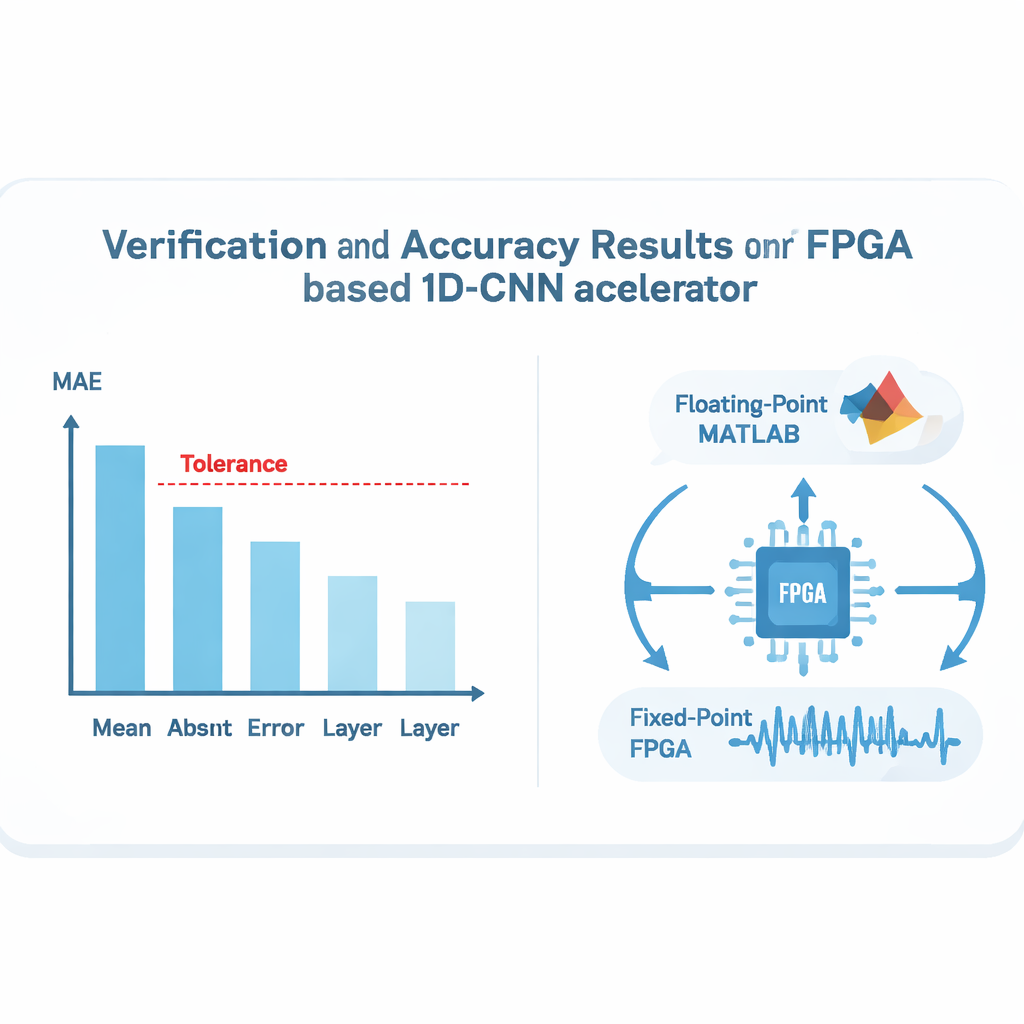

De MATLAB à C++ puis FPGA, avec suivi des nombres

Plutôt que d’appuyer sur un bouton de « conversion » automatique, le réseau est réimplémenté manuellement en C++, en suivant la même organisation des données et les mêmes étapes mathématiques que dans MATLAB. Ce code C++ est ensuite utilisé avec un outil de synthèse de haut niveau pour générer le matériel qui s’exécute sur une carte FPGA PYNQ-Z1. À chaque étape — MATLAB, C++ et FPGA — les sorties des couches sont comparées aux sorties de référence stockées à l’aide d’un indicateur simple : l’erreur absolue moyenne, qui mesure la différence numérique moyenne entre deux ensembles de résultats. L’étude fixe une tolérance stricte : toutes les couches doivent rester en dessous d’une erreur de 1,5×10⁻³. Sur des milliers d’échantillons ECG, chaque couche testée respecte cet objectif, et la précision finale de classification reste quasi inchangée : environ 98,3–98,4 % dans MATLAB et C++, et seulement environ 0,2 point de pourcentage de moins sur le FPGA, une différence compatible avec les effets attendus de l’utilisation de nombres en virgule fixe plus courts dans le matériel.

Accélérer le matériel sans briser les calculs

Une fois la correction assurée, la conception est optimisée pour la vitesse. Les parties les plus exigeantes du réseau — les couches convolutionnelles — sont mappées sur la logique programmable du FPGA, en utilisant l’arithmétique en virgule fixe pour l’efficacité, tandis que des tâches plus légères comme le calcul final softmax s’exécutent sur le processeur intégré de la puce avec des nombres à virgule flottante classiques. Des techniques telles que le pipeline de boucles, le déroulement de boucles et le partitionnement soigné de la mémoire en banques parallèles permettent à différentes parties des calculs et des transferts de données de s’exécuter en parallèle. Une version optimisée du matériel traite une fenêtre de battement en environ 1,7 milliseconde et tient confortablement dans les limites de ressources et de puissance du FPGA, tout en préservant le comportement numérique couche par couche du modèle MATLAB original.

Ce que cela signifie pour les futurs appareils intelligents

Pour les non-spécialistes, le message clé est qu’il est désormais possible non seulement d’accélérer un classificateur de rythmes cardiaques sophistiqué basé sur MATLAB sur une puce à faible consommation, mais aussi de prouver que le fonctionnement interne de la puce correspond étroitement au modèle logiciel de référence à chaque couche. Plutôt que de rechercher la vitesse au détriment de la fiabilité, cette approche crée une piste d’audit claire du code MATLAB en virgule flottante au matériel FPGA en virgule fixe. La même recette de vérification — sauvegarder des sorties de référence, comparer les erreurs couche par couche à un seuil strict et vérifier la précision finale — peut être appliquée à d’autres réseaux neuronaux unidimensionnels dans des domaines tels que les dispositifs de santé portables, les capteurs industriels et les véhicules intelligents, aidant à garantir que lorsque les algorithmes quittent le laboratoire pour s’intégrer aux appareils, leurs décisions restent fiables.

Citation: Bal, S. Towards the transformation of MATLAB models into FPGA-Based hardware accelerators. Sci Rep 16, 5027 (2026). https://doi.org/10.1038/s41598-026-36033-z

Mots-clés: Accélérateurs FPGA, Réseaux neuronaux MATLAB, Classification des arythmies ECG, Vérification matérielle, Deep learning en virgule fixe