Clear Sky Science · fr

Conception de multiplicateurs approchés basse consommation et haute vitesse utilisant des compresseurs 4-à-2 en mode courant basés sur la technologie CNTFET

Images plus nettes avec moins d'énergie

Chaque fois que votre téléphone prend une photo, diffuse une vidéo ou applique un filtre d'IA, il effectue des millions de petites multiplications. Faire tous ces calculs exactement coûte de l'énergie et ralentit les traitements, alors que l'œil humain ne perçoit souvent pas de petites erreurs numériques. Cet article montre comment « détendre » délibérément une partie de ces calculs grâce à un nouveau type de circuit, réduisant la consommation et la latence tout en conservant des images visuellement indiscernables des résultats exacts.

Pourquoi des calculs imparfaits peuvent sembler parfaits

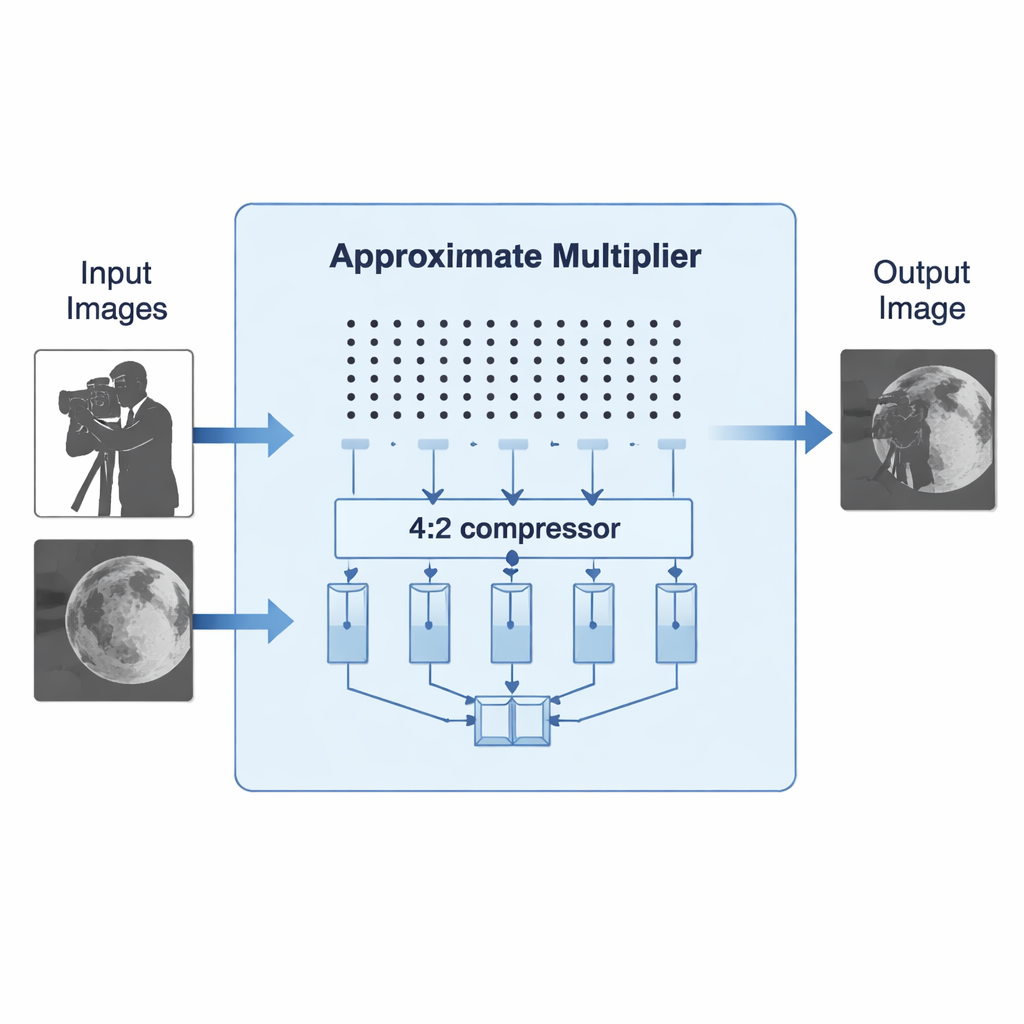

Beaucoup d'applications modernes — comme le traitement d'image, la vidéo et l'apprentissage automatique — tolèrent naturellement de petites erreurs. Une légère variation de la luminosité d'un pixel ou un petit décalage dans la réponse d'un filtre est généralement imperceptible. Les auteurs exploitent cela en utilisant des multiplicateurs approchés : des circuits qui échangent un peu de précision arithmétique contre d'importantes économies d'énergie, de surface de puce et de temps. Ils se concentrent sur des multiplicateurs 8×8, élément courant du traitement numérique du signal, et évaluent non seulement l'erreur numérique, mais aussi l'impact réel de ces approximations sur la qualité finale des images à l'aide de métriques standard telles que le rapport signal‑sur‑bruit de crête (PSNR) et la similarité structurelle (MSSIM).

Un nouveau bloc de construction pour des multiplicateurs rapides

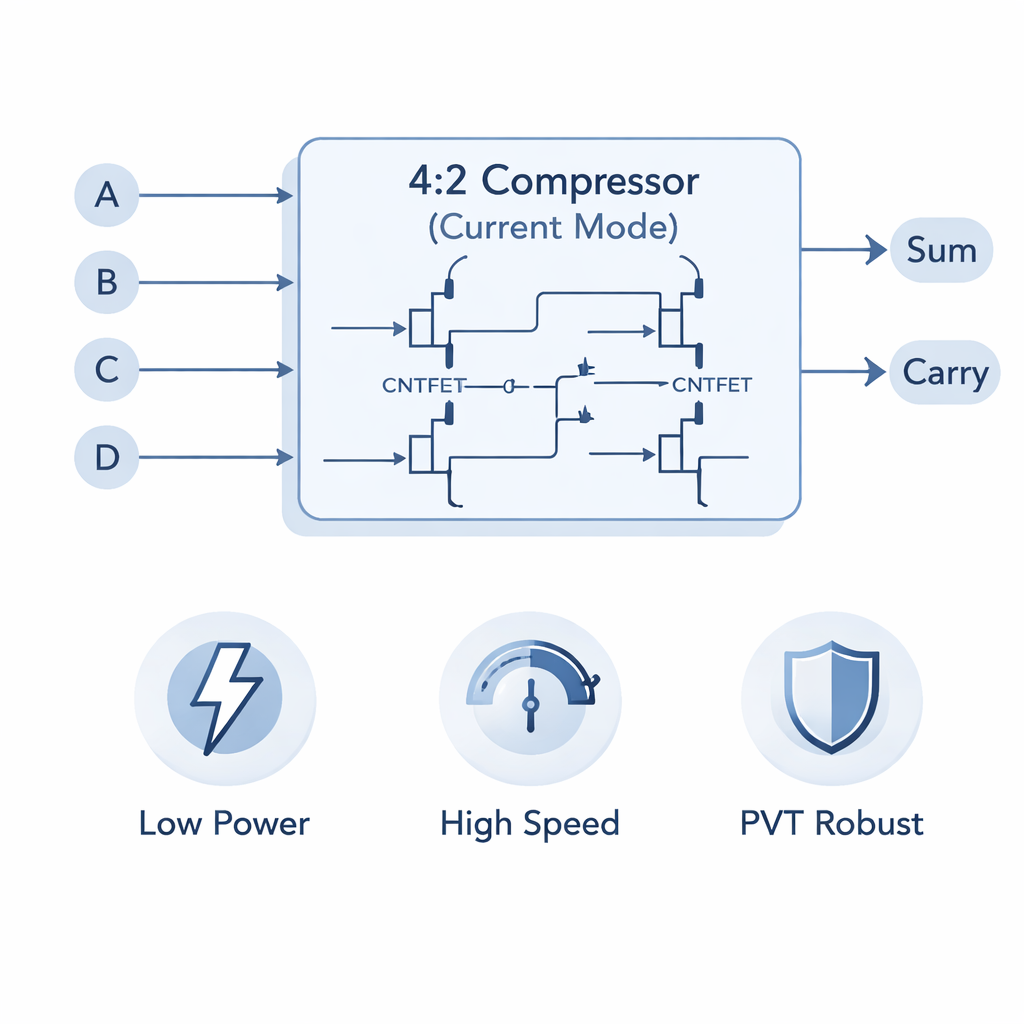

Au cœur de la conception se trouve un composant appelé compresseur 4:2, qui réduit quatre bits d'entrée et une entrée de retenue en deux sorties, « somme » et « retenue ». Les compresseurs traditionnels utilisent des transistors CMOS ou FinFET en mode tension, dont la mise à l'échelle devient difficile à très petites dimensions. Ce travail combine plutôt la logique en mode courant avec des transistors à effet de champ en nanotubes de carbone (CNTFET) de 7 nanomètres. En considérant l'information comme des courants plutôt que seulement des tensions, les circuits peuvent sommer les courants directement sans circuits lourds de détection de seuil. Les CNTFET, dont la tension de seuil peut être ajustée par le diamètre des nanotubes, permettent de réaliser des portes majoritaires, XOR et d'autres portes de base avec très peu de transistors, de marges de bruit élevées et une faible énergie par opération.

Six variantes de compresseurs « suffisants »

Les auteurs proposent six nouveaux designs de compresseurs 4:2. Quatre sont des compresseurs approchés monomodes, chacun explorant une manière différente de simplifier la logique interne et de réduire la consommation, la latence ou l'erreur. Deux autres sont des compresseurs à double fonction pouvant basculer entre comportement exact et approché via du power gating, de sorte qu'une seule partie du circuit soit active à la fois. Pour ces options, ils mesurent soigneusement la distance d'erreur (à quel point une sortie peut s'écarter de la perfection), la fréquence des sorties encore exactes, et la robustesse des circuits face aux variations de procédé, de tension et de température. Grâce à l'approche en mode courant avec CNTFET, les nouveaux compresseurs sont 30–50 % moins sensibles à ces variations que des conceptions CMOS ou FinFET comparables, tout en consommant seulement environ 12–25 microwatts avec des délais internes sub‑nanosecondes.

Deux conceptions de multiplicateurs pour l'image et l'IA

En s'appuyant sur ces compresseurs, l'équipe construit deux multiplicateurs Dadda 8×8. Le premier type utilise des compresseurs approchés dans chaque colonne, maximisant les économies d'énergie. Le second adopte une approche plus sélective : il supprime complètement les quatre colonnes de sortie les moins significatives (tronquature), utilise des compresseurs approchés dans les colonnes intermédiaires, et conserve des compresseurs exacts dans les colonnes les plus significatives où les erreurs seraient visuellement perceptibles. Des simulations sous HSPICE et MATLAB montrent que, pour la meilleure configuration, la puissance tombe à environ 0,52 mW, la latence à 1,88 ns, et le produit puissance‑délai à 0,97 pJ — des améliorations significatives par rapport aux multiplicateurs approchés antérieurs.

Ce que cela signifie pour les images réelles

Pour vérifier si ces économies sont pertinentes en pratique, les auteurs exécutent des tâches d'image standard comme la multiplication de deux images de référence (les classiques « cameraman » et « moon ») et l'accentuation. Ils comparent les images produites par des multiplicateurs exacts et leurs conceptions approchées. Malgré des erreurs arithmétiques internes allant jusqu'à ±2 dans certains cas, le meilleur multiplicateur proposé fait passer la similarité structurelle (MSSIM) d'environ 60 % pour des conceptions approchées antérieures à environ 97 %, et augmente le PSNR de 15–20 %. Visuellement, les images restent nettes et détaillées, tandis que le matériel sous‑jacent consomme beaucoup moins d'énergie et fonctionne plus rapidement, rendant cette approche intéressante pour les appareils photo basse consommation, les systèmes de vision portables et les dispositifs d'IA en périphérie où l'autonomie et la rapidité priment sur l'arithmétique parfaite.

Citation: Foroutan, P., Navi, K. Design of low power and high speed approximate multipliers utilizing current mode 4 to 2 compressors based on CNTFET technology. Sci Rep 16, 4834 (2026). https://doi.org/10.1038/s41598-026-35104-5

Mots-clés: multiplicateurs approchés, CNTFET, traitement d'image, circuits basse consommation, logique en mode courant