Clear Sky Science · es

Sinapsis espintrónicas multi-bit escalables y robustas para computación analógica en memoria

Por qué una memoria más inteligente importa para la IA cotidiana

Desde asistentes de voz hasta aplicaciones de fotos, la inteligencia artificial moderna depende en gran medida de redes neuronales profundas: programas que manejan millones de pequeñas “pesos” numéricos para tomar decisiones. Mover esos pesos entre la memoria y los procesadores cuesta mucho más energía que los propios cálculos. Este artículo explora un nuevo tipo de celda de memoria magnética que puede tanto almacenar esos pesos como ayudar a realizar los cálculos directamente donde residen los datos, prometiendo hardware de IA más rápido y eficiente.

Llevando el cómputo tipo cerebro dentro del chip de memoria

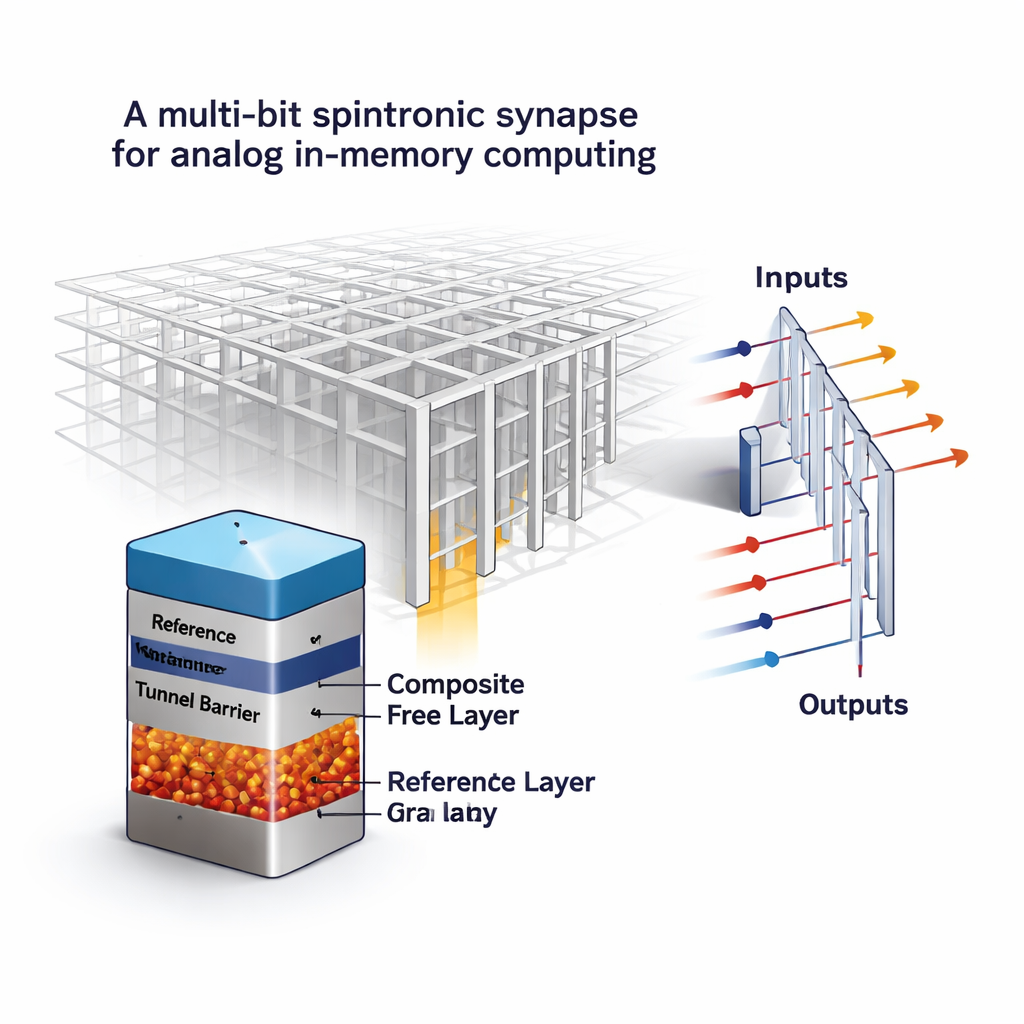

Los ordenadores actuales siguen la clásica arquitectura de von Neumann, donde los datos circulan constantemente entre la memoria y un procesador separado. Las redes neuronales, que se reducen a enormes cantidades de multiplicaciones matriz–vector, chocan fuertemente con este cuello de botella. Una alternativa prometedora es la computación en memoria, donde una gran rejilla (una matriz de cruce) de celdas de memoria contiene los pesos de la red y, al mismo tiempo, convierte voltajes entrantes en corrientes de salida que representan los cálculos. Se han probado muchos dispositivos experimentales para este papel, pero a menudo sufren comportamientos ruidosos y valores que derivan, lo cual es arriesgado cuando cada celda debe representar más que un 0 o un 1.

Transformar la memoria magnética de encendido–apagado a “analógica”

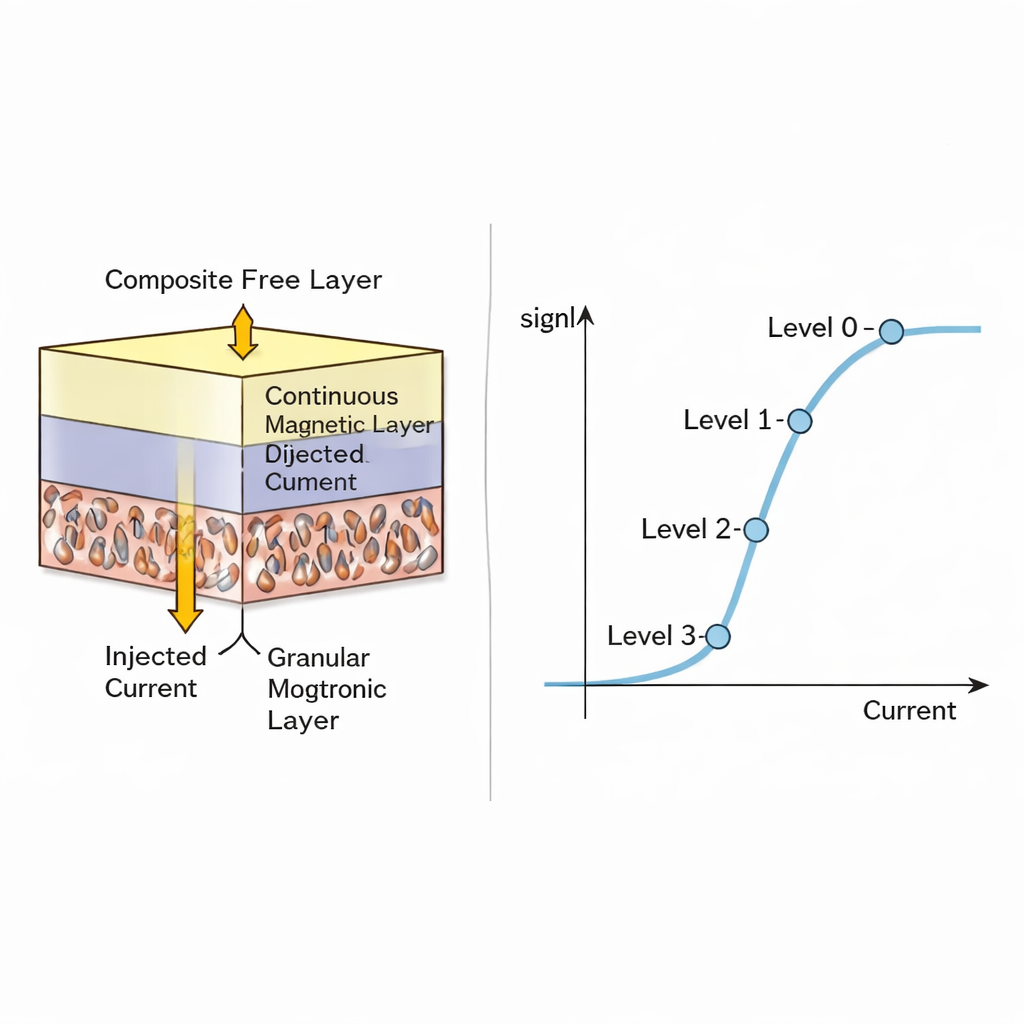

Los autores parten de la memoria magnética de acceso aleatorio (MRAM), una tecnología no volátil ya valorada por su velocidad, durabilidad y compatibilidad con procesos estándar de fabricación de chips. Una celda MRAM convencional es una unión túnel magnética: dos capas magnéticas separadas por una barrera aislante. Según si las capas se alinean o se oponen, la resistencia eléctrica de la celda es baja o alta, codificando un solo bit. La clave aquí es rediseñar la capa magnética “libre” para que deje de ser un bloque uniforme que cambia de golpe. En su lugar, el nuevo diseño combina una película continua muy fina encima de una capa magnética granular más gruesa compuesta por muchos pequeños granos magnéticos. Cada grano puede invertir su dirección a corrientes ligeramente diferentes, de modo que la resistencia global puede estabilizarse en varios niveles intermedios en lugar de solo “bajo” y “alto”.

¿Cuántos matices de magnetismo son útiles?

Usando modelos computacionales detallados de la dinámica magnética, el equipo muestra que inyectar una corriente spin-polarizada en esta capa compuesta provoca un proceso de conmutación gradual, grano por grano. A medida que se barre la corriente, la magnetización media y por tanto la resistencia trazan una curva suave en forma de S, habilitando estados analógicos casi continuos. Los autores examinan luego cómo las diferencias de fabricación entre celdas y los efectos térmicos aleatorios de un ciclo de escritura a otro perturban estos niveles. Encuentran que, aunque los estados intermedios son algo más ruidosos, los estados extremos (totalmente conmutados en un sentido u otro) permanecen muy ajustados y robustos. Para dispositivos de tamaño realista (alrededor de 50–75 nanómetros de lado), concluyen que cuatro niveles de resistencia distinguibles con fiabilidad —equivalentes a 2 bits por celda— son prácticos sin errores excesivos.

De la celda única al acelerador de IA completo

Para ser útil, este MRAM multinivel debe leerse con precisión e integrarse en sistemas de computación completos. Los autores diseñan y simulan un circuito de detección que usa un convertidor analógico-digital “flash” rápido para distinguir entre los cuatro niveles de resistencia de cada celda. Exploran cómo el contraste entre los estados de conductancia más altos y más bajos afecta la velocidad de lectura, el consumo energético y el tamaño del circuito de detección, mostrando que un mayor contraste conduce directamente a lecturas más rápidas y eficientes en energía. A continuación, integran su modelo de MRAM de 2 bits por celda en un acelerador en memoria simulado que ejecuta una red ResNet-18 sobre el conjunto de imágenes CIFAR-10. En comparación con una línea base que usa celdas MRAM estándar de 1 bit, la versión multi-bit duplica aproximadamente la densidad de almacenamiento y reduce a la mitad el número requerido de bloques de cruce. Esto se traduce en reducciones de hasta alrededor de 1,8× en área de chip, energía y latencia, y en más de 3× de mejora en la métrica combinada energía–retardo, todo ello mientras se preserva esencialmente la precisión de reconocimiento de la red.

Cómo se compara con otras ideas de memoria

El estudio también compara este enfoque con tecnologías competidoras como la memoria resistiva y la de cambio de fase, así como otros conceptos magnéticos que dependen del movimiento de paredes de dominio o de skyrmiones. Aunque esas alternativas también pueden producir un comportamiento parecido al analógico, a menudo requieren dispositivos mayores o formas especiales y tienden a ser más impredecibles. En contraste, las celdas MRAM granulares conservan la facilidad de fabricación y la resistencia de la MRAM convencional mientras ganan niveles de almacenamiento adicionales. Las pruebas a nivel de sistema sugieren que, bajo variaciones realistas, las sinapsis basadas en MRAM mantienen la precisión de las redes neuronales mucho más alta que diseños similares construidos sobre memorias resistivas más variables, especialmente cuando las redes se vuelven dispersas para ahorrar energía adicional.

Qué implica esto para la IA cotidiana del futuro

En términos simples, los autores han mostrado una forma de enseñar a una tecnología de memoria magnética probada a almacenar no solo ceros y unos, sino pequeños valores analógicos de pesos directamente dentro de una celda compacta. Mediante la ingeniería cuidadosa de una estructura en capas que reparte el comportamiento magnético entre muchos granos diminutos, obtienen múltiples niveles de resistencia estables que son lo bastante robustos para tareas de IA del mundo real. Cuando estas celdas se organizan en grandes matrices y se combinan con circuitos de detección adecuados, pueden realizar los cálculos centrales del aprendizaje profundo mientras reducen drásticamente el movimiento de datos. Si se llegan a implementar en hardware, tales sinapsis espintrónicas multi-bit podrían hacer que los sistemas de IA futuros —ya sea en centros de datos, teléfonos inteligentes o sensores embebidos— sean más rápidos y energéticamente más eficientes sin sacrificar la precisión.

Cita: Gupte, K.K., Mugdho, S.S., Huang, C. et al. Scalable and robust multi-bit spintronic synapses for analog in-memory computing. npj Unconv. Comput. 3, 8 (2026). https://doi.org/10.1038/s44335-026-00055-7

Palabras clave: computación en memoria, memoria espintrónica, MRAM, hardware neuromórfico, redes neuronales profundas