Clear Sky Science · es

Gestión térmica de microelectrónica 3D integrada heterogéneamente: desafíos y direcciones futuras de investigación

Por qué apilar chips cambia tus dispositivos cotidianos

Desde teléfonos y portátiles hasta centros de datos que alimentan la inteligencia artificial, nuestros dispositivos electrónicos siguen haciéndose más pequeños mientras realizan más trabajo que nunca. Para lograrlo, los ingenieros están apilando distintos tipos de chips unos sobre otros, creando paquetes tridimensionales compactos. Esta maniobra mejora el rendimiento y reduce las latencias de señal, pero también encierra enormes cantidades de calor en un espacio diminuto. El artículo revisado explica por qué el calor se ha convertido en una de las mayores amenazas para esta nueva generación de electrónicos —y qué están haciendo los investigadores para evitar que estos pequeños rascacielos de silicio se sobrecalienten.

Construyendo pequeños rascacielos electrónicos

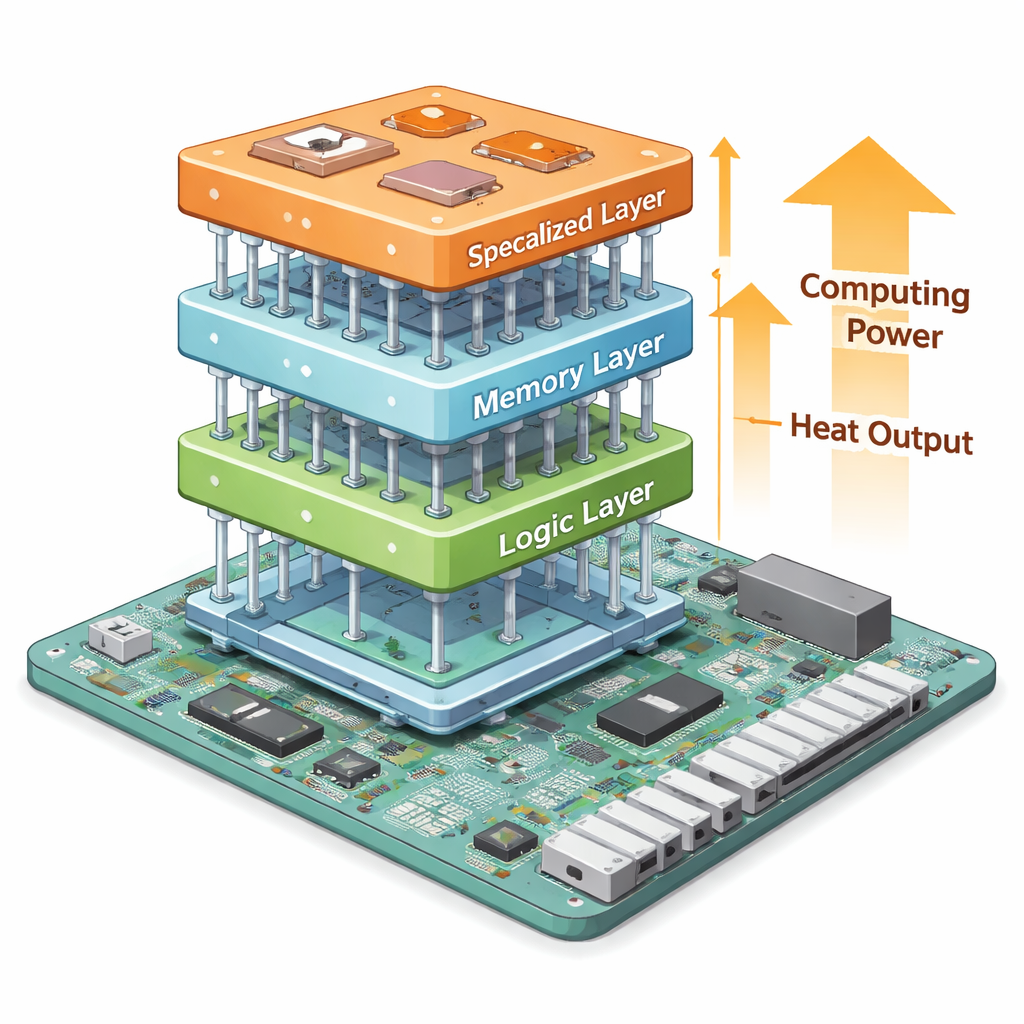

Los chips tradicionales son mayormente planos: los circuitos se extienden lado a lado en una sola oblea de silicio. A medida que resulta más difícil seguir reduciendo las características en dos dimensiones, la industria se orienta hacia la integración heterogénea tridimensional, donde varias capas de distintos chips —lógica, memoria, radio, fotónica y más— se apilan verticalmente y se conectan mediante pilares metálicos. Esta disposición acorta las rutas de comunicación y permite a los diseñadores combinar tecnologías fabricadas en distintas plantas. El resultado es un procesamiento más rápido, menor latencia en las comunicaciones y mejor eficiencia energética, especialmente valiosos para inteligencia artificial, computación en la nube y sistemas avanzados de comunicación.

El coste oculto de concentrar más potencia

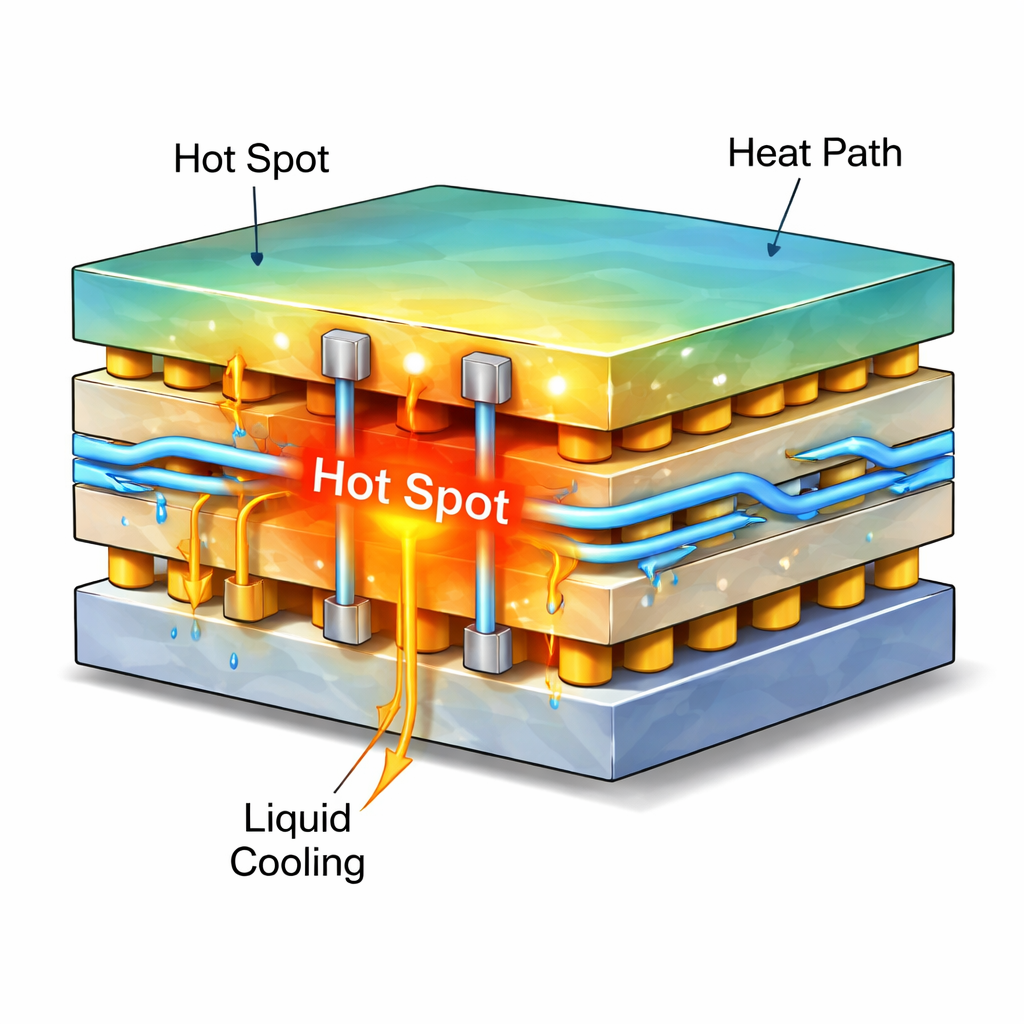

Apilar chips tan juntos tiene una desventaja seria: al calor le resulta más difícil escapar. Cada capa genera calor por pérdidas eléctricas habituales —resistencia en los conductores, conmutación de interruptores y pequeñas corrientes de fuga que nunca se apagan por completo. En pilas 3D estas pérdidas se acumulan, y las capas intermedias, más alejadas de cualquier superficie de refrigeración, tienden a ser las más calientes. La temperatura puede aumentar de forma desigual, creando puntos calientes que miden apenas una fracción de milímetro pero son mucho más cálidos que su entorno. Incluso unos pocos grados por encima del rango de operación previsto pueden reducir drásticamente la fiabilidad, acelerar el desgaste y, en casos extremos, desencadenar un bucle autoalimentado de aumento de temperatura y corriente conocido como fuga térmica (thermal runaway).

Cuando el calor se expande, flexiona y rompe cosas

La revisión explica que los problemas térmicos no son solo que un chip funcione caliente; pueden dañar silenciosamente todo el paquete. Los distintos materiales en la pila —silicio, metales, polímeros y cerámicas— se dilatan cantidades diferentes al calentarse. Al ciclarse el dispositivo entre reposo y plena potencia, estas discrepancias generan tensiones mecánicas que pueden agrietar soldaduras, abrir huecos en las interfaces y dañar las conexiones verticales rellenas de metal. Al mismo tiempo, el calentamiento desigual provoca diafonía térmica: un dado lógico caliente puede calentar involuntariamente una capa de memoria o una capa óptica de baja potencia encima, degradando su rendimiento. Con el tiempo, pequeñas cavidades y grietas alrededor de las estructuras que transportan calor crecen, añadiendo resistencia térmica adicional y dificultando aún más la extracción de calor donde más importa.

Nuevas técnicas para mover el calor en tres dimensiones

Para afrontar estos retos, los investigadores están replanteando cada parte de la ruta térmica. Algunas estrategias buscan dispersar el calor más eficazmente dentro de la pila usando mejores underfills y materiales intercapas que conduzcan el calor sin interferir con las señales eléctricas. Otras reutilizan los pilares metálicos verticales como conductos dedicados al calor o añaden pilares adicionales exclusivos para disipación junto a las rutas de señal. La revisión también destaca una tendencia a acercar mucho más el sistema de refrigeración a la fuente de calor. Pequeños canales líquidos y bosques de micro aletas pueden ser grabados directamente dentro o entre las capas del chip, permitiendo que el refrigerante fluya a decenas de micrómetros de los puntos más calientes. Estos sistemas de refrigeración embebidos pueden eliminar flujos de calor extremos y adaptar el flujo a las necesidades de cada capa, pero introducen nuevos problemas de resistencia mecánica, complejidad de fabricación y fiabilidad a largo plazo frente a presión y humedad.

Hacia dónde se dirige el campo

En general, el artículo concluye que el control térmico determinará en gran medida hasta dónde pueden llegar los electrónicos apilados en 3D. Ninguna solución única es suficiente: el diseño del chip, los materiales, las conexiones verticales, las capas de interfaz y los canales de refrigeración deben diseñarse de forma conjunta y no aisladamente. Trabajos futuros se centrarán en formas escalables de combinar materiales de alta conductividad compatibles mecánicamente con procesos fabricables y de baja temperatura, así como en herramientas de diseño más inteligentes que traten el comportamiento térmico al mismo nivel que la velocidad y el consumo. Si se superan estos obstáculos, las pilas de chips tridimensionales podrían seguir ofreciendo más potencia de cálculo en paquetes cada vez más pequeños —sin consumirse por el calor.

Cita: Sharma, M.K., Ramos-Alvarado, B. Thermal management of 3-D heterogeneously integrated microelectronics: challenges and future research directions. Commun Eng 5, 28 (2026). https://doi.org/10.1038/s44172-026-00590-y

Palabras clave: apilamiento de chips 3D, refrigeración de electrónicos, gestión térmica, refrigeración microfluídica, integración heterogénea