Clear Sky Science · es

Mapeo de dinámicas diversas de histéresis en FETs de MoS2 escalados mediante el método universal derivado del modelado TCAD

Por qué los interruptores diminutos necesitan un comportamiento fiable

La electrónica moderna avanza hacia transistores cada vez más pequeños, y materiales bidimensionales (2D) como el disulfuro de molibdeno (MoS2) son candidatos líderes para los chips del futuro. Pero a medida que estos interruptores se reducen, su comportamiento puede volverse inconsistente: el mismo dispositivo puede responder de forma distinta según cómo se haya usado apenas momentos antes. Este efecto similar a la memoria, llamado histéresis, a menudo se considera una molestia menor. En este trabajo, los autores muestran que la histéresis en realidad oculta una gran cantidad de información sobre las fallas internas de los transistores avanzados, y presentan una forma universal de extraer esa información.

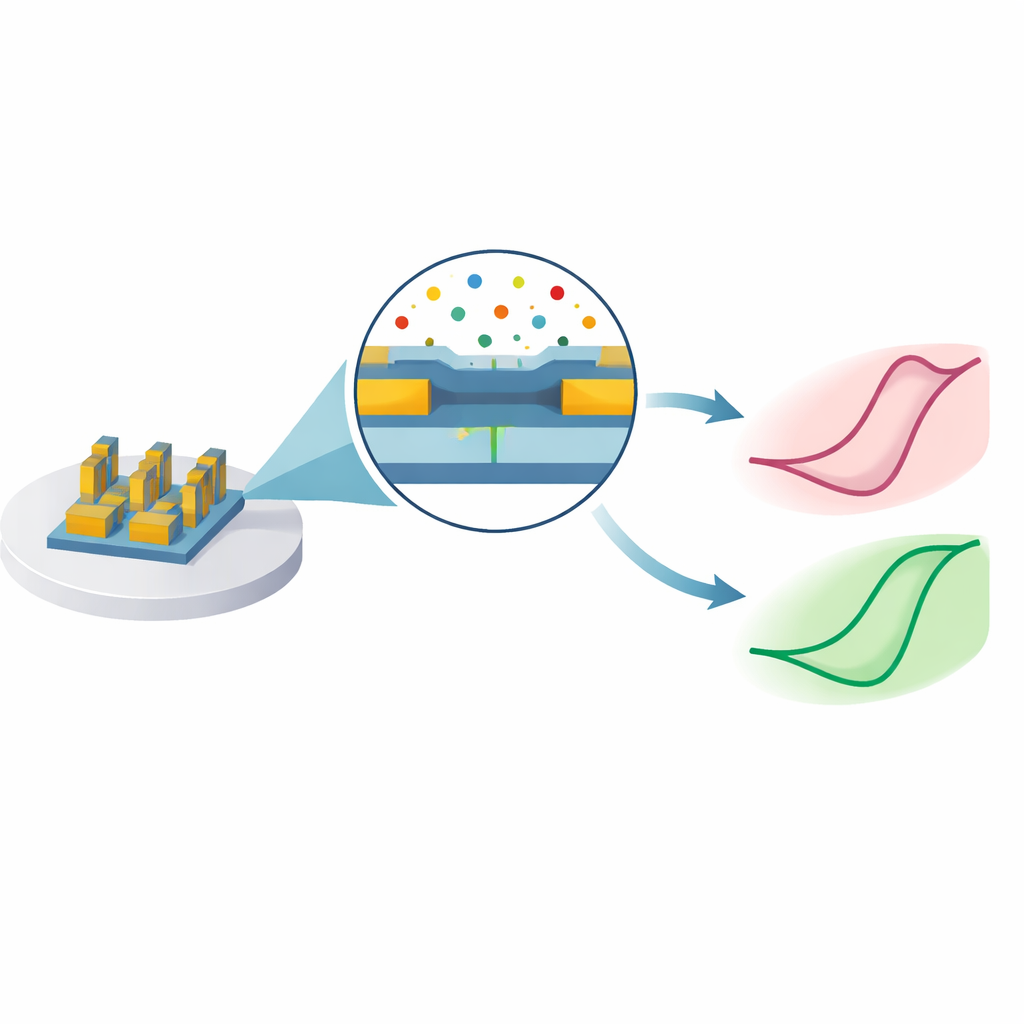

Cómo se construyen los transistores de próxima generación

Los futuros transistores de efecto campo 2D emplean una capa ultrafina de MoS2 como canal por donde fluye la corriente, cubierta por un óxido aislante muy delgado como el óxido de hafnio (HfO2), y un electrodo de puerta metálico en la parte superior. Para seguir reduciendo el tamaño de los dispositivos, este óxido debe ser eléctricamente de apenas un nanómetro de espesor, lo que significa que cualquier defecto individual en él puede perturbar fuertemente el canal. Estos defectos actúan como trampas diminutas que pueden retener o liberar carga eléctrica temporalmente. Dado que los defectos pueden situarse a distintas profundidades dentro del óxido e interactuar tanto con el canal como con la puerta, su comportamiento colectivo puede estabilizar o desestabilizar el transistor de formas sutiles. Entender este paisaje de defectos es crucial si los transistores 2D quieren competir con la tecnología de silicio actual.

Por qué el transistor recuerda su pasado

Cuando los ingenieros barran el voltaje de puerta hacia arriba y hacia abajo y registran la corriente, a menudo encuentran que las trayectorias de subida y bajada no coinciden. Este bucle es la histéresis. Tradicionalmente, los investigadores miden la separación entre las dos curvas en un único punto de operación y lo llaman ancho de histéresis, concluyendo a menudo que es “pequeño” o “despreciable”. Los autores sostienen que esta práctica resulta engañosa, especialmente en dispositivos escalados en los que distintos grupos de defectos pueden contribuir de maneras opuestas. Dependiendo de la velocidad de medida y de la corriente de operación, el mismo transistor puede mostrar bucles convencionales en sentido horario, bucles invertidos en sentido antihorario, alternar entre ambos o incluso casi nula histéresis cuando los efectos opuestos se cancelan.

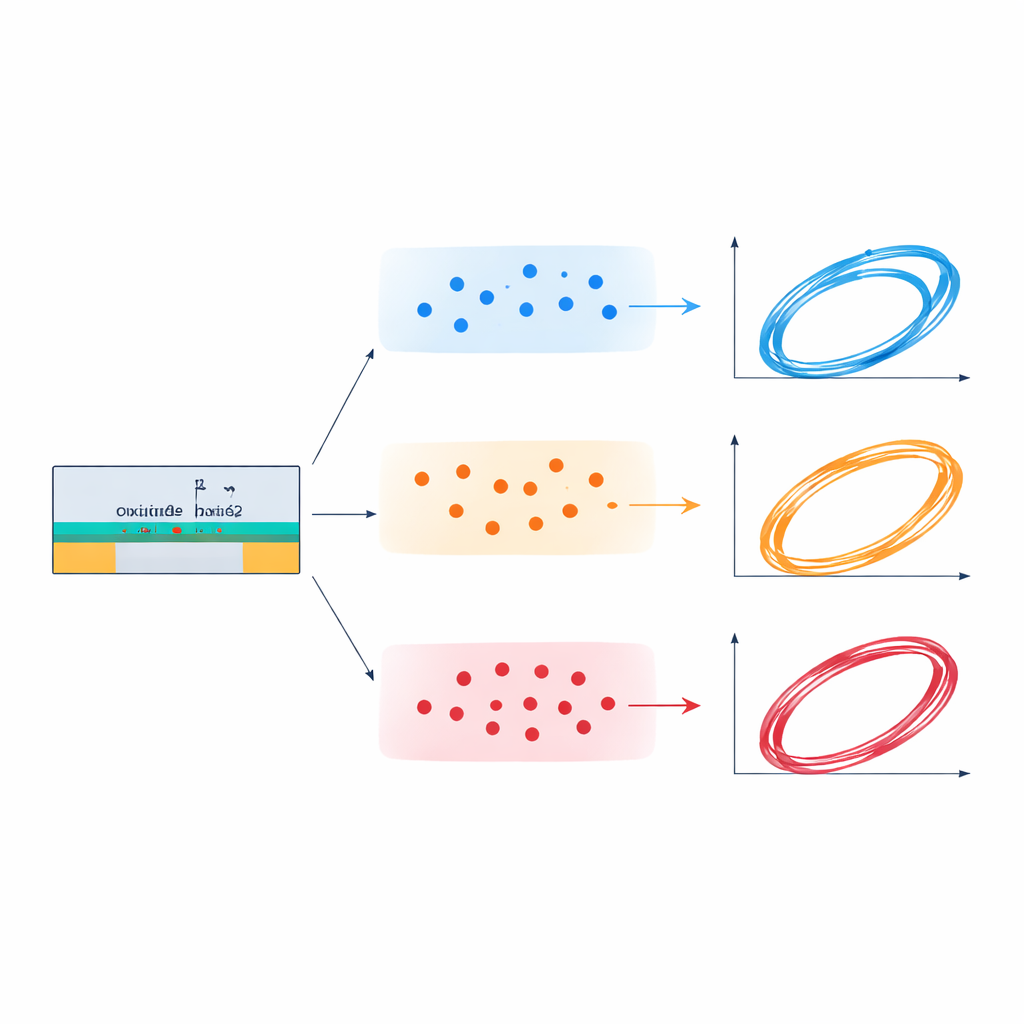

Un mapa universal oculto en las curvas

Para desenmarañar esta complejidad, el equipo usa simulaciones por computadora detalladas (TCAD) de transistores de MoS2 a nanoescala con poblaciones de defectos controladas en diferentes profundidades del óxido. A continuación proponen un método universal de mapeo de histéresis. En lugar de extraer un único número, barrén el ancho de histéresis a lo largo de un amplio rango de corrientes —desde apenas por encima del estado apagado hasta casi el estado encendido— y para tiempos de barrido que abarcan muchos órdenes de magnitud. Esto produce miles de curvas que muestran cómo cambia la histéresis con la velocidad de medida en cada corriente. A partir de ellas definen funciones universales de histéresis superior e inferior que encierran todos los comportamientos posibles. Estos envolventes revelan claramente qué tipos de defectos están activos, si interactúan principalmente con el canal o con la puerta superior, y si favorecen bucles en sentido horario o antihorario.

Vinculando bucles rápidos con deriva a largo plazo

Los mismos defectos que causan histéresis también impulsan desviaciones lentas en el comportamiento del transistor bajo estrés prolongado, un problema conocido como inestabilidad por temperatura y polarización (BTI). Mediante la simulación de experimentos estándar de estrés y recuperación, los autores conectan rasgos en sus mapas de histéresis con firmas inusuales de BTI, como un desplazamiento aparente negativo que solo más tarde se relaja hacia uno positivo. Demuestran que las trampas cercanas al canal tienden a causar desplazamientos lentos y mayormente permanentes, mientras que las trampas más próximas a la puerta producen cambios más rápidos pero en gran medida reversibles. Su método puede aplicarse no solo a dispositivos de MoS2 simulados sino también a datos medidos de transistores reales de MoS2 y WSe2 fabricados en salas limpias de investigación y en líneas piloto, incluyendo casos en los que iones en deriva dentro del óxido se suman al juego de atrapamiento de carga.

De datos complejos a orientación práctica

Al convertir bucles de histéresis desordenados en mapas estandarizados, este trabajo ofrece un diagnóstico potente para tecnologías emergentes de transistores. El método funciona directamente con conjuntos de datos experimentales y no requiere acceso a herramientas avanzadas de simulación, lo que lo hace ampliamente utilizable en distintos laboratorios. Para los ingenieros, el mensaje clave es que la histéresis no es solo un defecto a minimizar, sino la huella digital de problemas de confiabilidad subyacentes. Decodificar esa huella con el método de mapeo propuesto puede guiar la selección de mejores materiales, interfaces más limpias y procesos más inteligentes, ayudando a que los transistores 2D avancen de prototipos prometedores a bloques de construcción realmente fiables de la electrónica futura.

Cita: Lv, Y.Z., Wu, Y.H., Cai, H.H. et al. Mapping diverse hysteresis dynamics in scaled MoS2 FETs using the universal method derived from TCAD modeling. npj 2D Mater Appl 10, 35 (2026). https://doi.org/10.1038/s41699-026-00671-8

Palabras clave: transistores 2D, histéresis, defectos de óxido, confiabilidad de dispositivos, FETs de MoS2