Clear Sky Science · es

3D LineExplore: un método de exploración de líneas 3D para el enrutamiento geométrico de PCB multicapa

Cableado más inteligente para las placas de circuito dentro de todo

Todos los teléfonos inteligentes, ordenadores portátiles y automóviles ocultan hoy pequeñas autopistas de cobre que transportan señales entre chips. A medida que la electrónica concentra más componentes en menos espacio, trazar estas “carreteras” microscópicas en las placas de circuito impreso (PCB) se ha convertido en uno de los pasos más difíciles del diseño de hardware. Este artículo presenta una forma nueva de planificar automáticamente esas rutas en tres dimensiones, prometiendo diseño más rápido, menos errores y mejor rendimiento para los dispositivos que usamos a diario.

Por qué el enrutamiento tradicional choca contra un límite

Los enrutadores automáticos de PCB actuales suelen pensar en términos de una cuadrícula tipo tablero de ajedrez: la placa se divide en pequeñas celdas y algoritmos como A* buscan el camino más barato de un pin a otro. Esto funciona, pero trae compromisos. Si la cuadrícula es gruesa, las rutas son imprecisas y pueden violar las reglas de diseño. Si la cuadrícula es muy fina, la búsqueda se dispara en tamaño y se vuelve terriblemente lenta, especialmente en placas multicapa donde las pistas pueden saltar entre capas mediante pequeños agujeros perforados llamados vías. Los métodos sin cuadrícula evitan la rejilla artificial y trabajan directamente con formas, pero hasta ahora se han limitado en gran medida a diseños planos bidimensionales y les cuesta manejar de manera eficiente el enrutamiento 3D multicapa real.

Un “radar” 3D para encontrar rutas seguras

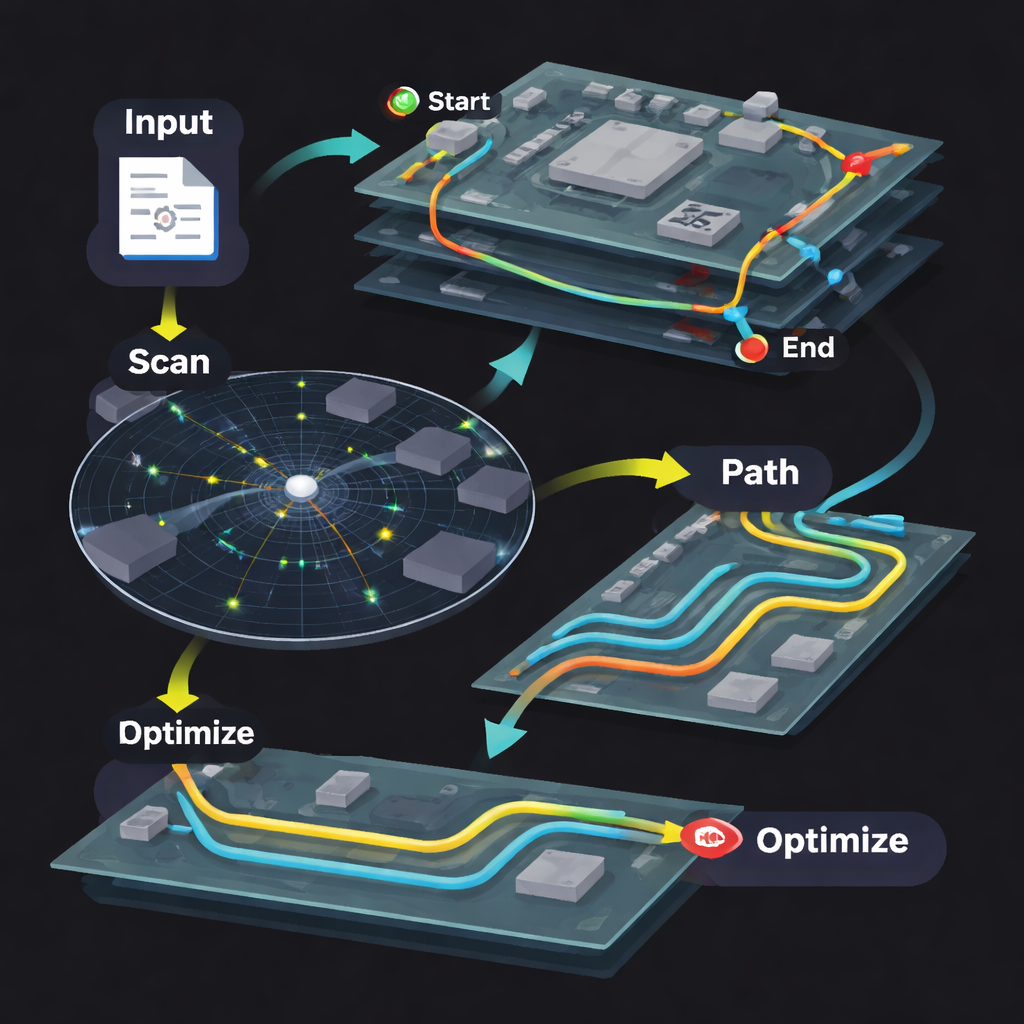

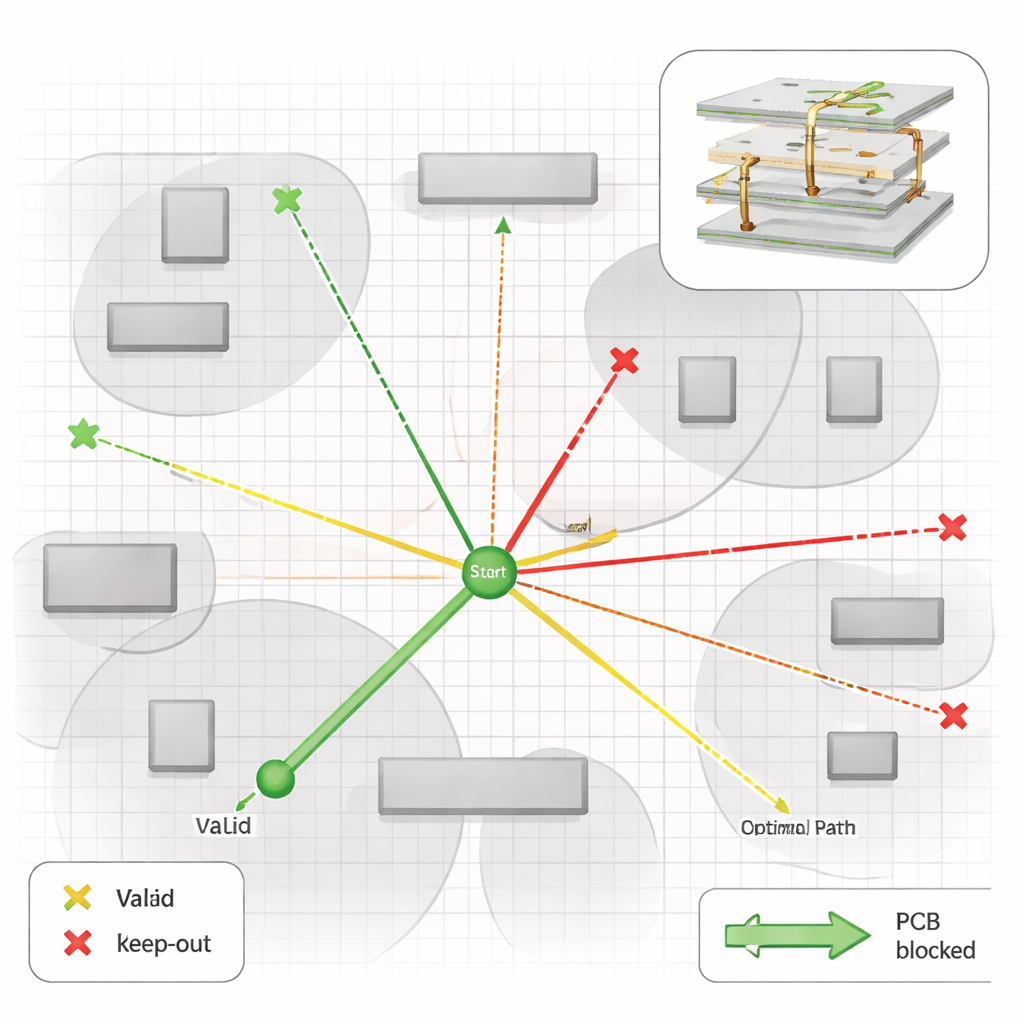

Los autores presentan 3D LineExplore, un método de enrutamiento sin cuadrícula que trabaja directamente en espacio continuo a través de múltiples capas. En su núcleo hay un algoritmo de escaneo inspirado en un “radar”. En lugar de comprobar cada celda de una rejilla, el método inspecciona el vecindario local del punto actual, identifica obstáculos cercanos como componentes y cables ya colocados, y recoge puntos clave en las esquinas de esas formas. A partir de estos, propone un conjunto compacto de “puntos de exploración” prometedores por donde un cable podría pasar de forma segura. Si el vecindario inmediato no permite hallar una ruta, el radio de escaneo se expande, pero solo cuando es necesario. Esta sondeo selectivo mantiene la búsqueda enfocada, evita comprobaciones redundantes y se extiende de forma natural a múltiples capas proyectando puntos objetivo entre capas y añadiendo puntos de exploración especiales que representan ubicaciones potenciales de vías.

Dejar que los costes guíen la mejor ruta

Una vez que se conocen los puntos de exploración, un segundo módulo elige la ruta real. Este algoritmo heurístico de evasión de obstáculos actúa como una búsqueda guiada: pondera la distancia ya recorrida, la distancia hasta cada punto candidato siguiente, el coste adicional de perforar una vía a otra capa y una estimación en línea recta de la distancia restante hasta el destino. Usando estos factores en una única función de coste y una cola de prioridad, el algoritmo siempre expande el siguiente paso más prometedor. En segundo plano, esto construye un grafo disperso de movimientos posibles sin llegar a dibujar una cuadrícula completa. Cuando se alcanza el pin objetivo, la ruta se reconstruye siguiendo los enlaces de predecesores almacenados hasta el inicio, produciendo una ruta 3D completa que sortea obstáculos y cambia de capa solo cuando compensa el coste añadido.

Limpiar redes complejas y afinar las trazas

En las PCB reales rara vez se conecta solo un par de pines a la vez. Muchas redes (nets) enlazan tres o más pines, lo que puede conducir fácilmente a callejones sin salida o rutas enredadas. 3D LineExplore aborda estos casos descomponiendo una red multipin en una secuencia de pares de pines vecinos más cercanos, enruta cada par uno por uno y luego repara cualquier fallo. Si una conexión no se puede completar según lo planeado, el algoritmo busca un empalme alternativo a un pin ya conectado cercano, restaurando la red con el mínimo cable adicional. Tras asegurar toda la conectividad, una etapa de posprocesado mejora la forma física de las pistas. Muchos diseños de alta velocidad prefieren curvas de aproximadamente 135 grados en lugar de ángulos rectos agudos, para facilitar la fabricación y reducir reflexiones eléctricas. Los autores introducen un ajuste geométrico tipo “paralelogramo” que remodela segmentos polilínea en trazas más suaves con restricción de 135 grados, preservando todas las conexiones y evitando nuevas colisiones.

Poner el nuevo método a prueba

El equipo evaluó 3D LineExplore en once placas de referencia públicas que van de simples a complejas, y lo comparó con herramientas comerciales y académicas, incluidas FreeRouting, ELECTRA, DeepPCB y un algoritmo 3D A* optimizado. En estos casos, el nuevo método conectó con éxito alrededor del 98% de los pares de pines requeridos, igualando o superando a enrutadores consolidados. Más notablemente, su longitud total de traza fue, de media, menor: aproximadamente un 15% menos que una herramienta comercial líder, lo que ayuda a reducir la latencia de señal y la pérdida de potencia. Aunque a veces utilizó más vías para sortear la congestión, este intercambio mejoró el uso del espacio y redujo la aglomeración en capas individuales. En términos de velocidad, el diseño de pasada única, combinado con el escaneo local adaptativo, permitió completar la mayoría de los diseños en segundos, y en algunos escenarios la búsqueda adaptativa redujo el tiempo de enrutamiento en más del 90% frente a una búsqueda exhaustiva de toda la placa, aumentando la longitud de traza solo ligeramente.

Qué significa esto para la electrónica futura

En términos sencillos, 3D LineExplore ofrece a los diseñadores de PCB una forma de enrutar placas densas multicapa más parecida a cómo lo haría un humano experto: mirando localmente, eligiendo solo las rutas candidatas más útiles y equilibrando caminos cortos frente al coste de cambiar de capa. Evita la pesada sobrecarga de las cuadrículas finas mientras sigue respetando estrictas reglas de diseño y produciendo trazas suaves y manufacturables. A medida que la electrónica siga creciendo en complejidad y reduciéndose en tamaño, enfoques como este—especialmente cuando se combinen con orientación futura mediante aprendizaje automático—podrían hacer que el enrutamiento automático sea tanto más rápido como más fiable, ayudando a que nuevas generaciones de dispositivos lleguen al mercado antes y funcionen con mayor eficiencia.

Cita: Sun, N., Zhang, J., Xu, N. et al. 3D LineExplore: a 3D line exploration method for multi-layer PCB geometric routing. Sci Rep 16, 6588 (2026). https://doi.org/10.1038/s41598-026-36925-0

Palabras clave: enrutamiento de PCB, placas multicapa, algoritmo sin cuadrícula, automatización del diseño electrónico, planificación de trayectorias 3D