Clear Sky Science · es

Hacia la transformación de modelos MATLAB en aceleradores hardware basados en FPGA

Convertir algoritmos de laboratorio en dispositivos reales

Muchas innovaciones médicas y de ingeniería modernas nacen como software desarrollado por investigadores, a menudo en entornos accesibles como MATLAB. Pero cuando esos mismos algoritmos deben ejecutarse en tiempo real —por ejemplo, para detectar problemas peligrosos de ritmo cardíaco a partir de un electrocardiograma (ECG)— necesitan la velocidad y eficiencia de hardware especializado. Este artículo muestra cómo trasladar de forma fiable una red neuronal compleja de detección de latidos desde MATLAB a un chip especializado llamado FPGA, sin perder la precisión de la que dependen médicos e ingenieros.

Por qué reescribir código para chips es tan difícil

Los FPGAs (Field-Programmable Gate Arrays) son chips reconfigurables valorados por su rapidez y bajo consumo energético. Tradicionalmente, programarlos requería lenguajes centrados en hardware como VHDL o Verilog, que están muy lejos del código de alto nivel matemático y de procesamiento de señales que los científicos escriben en MATLAB. Nuevas herramientas pueden convertir algoritmos automáticamente en descripciones de hardware, pero a menudo exigen ajustes manuales y se centran principalmente en el rendimiento: qué tan rápido funciona el chip y cuántos recursos utiliza. Lo que faltaba era una forma clara de demostrar que el hardware hace exactamente lo mismo que el software original, capa por capa, número por número.

Una comprobación paso a paso para cada capa de la red

El autor aborda esta laguna proponiendo un flujo de trabajo orientado a la verificación para una red neuronal convolucional unidimensional que clasifica latidos a partir de la conocida Base de Datos de Arritmias MIT-BIH. La red, construida en MATLAB, examina fragmentos cortos de señal ECG y los asigna a uno de cinco tipos de latido, incluidos normales y varios ritmos anómalos. Se entrenan tres versiones de la red, con distintas profundidades, usando los mismos datos. Tras el entrenamiento, los pesos, sesgos y las salidas de cada capa para señales de prueba se guardan como “salidas doradas”: un registro numérico preciso de cómo se comporta el modelo en MATLAB.

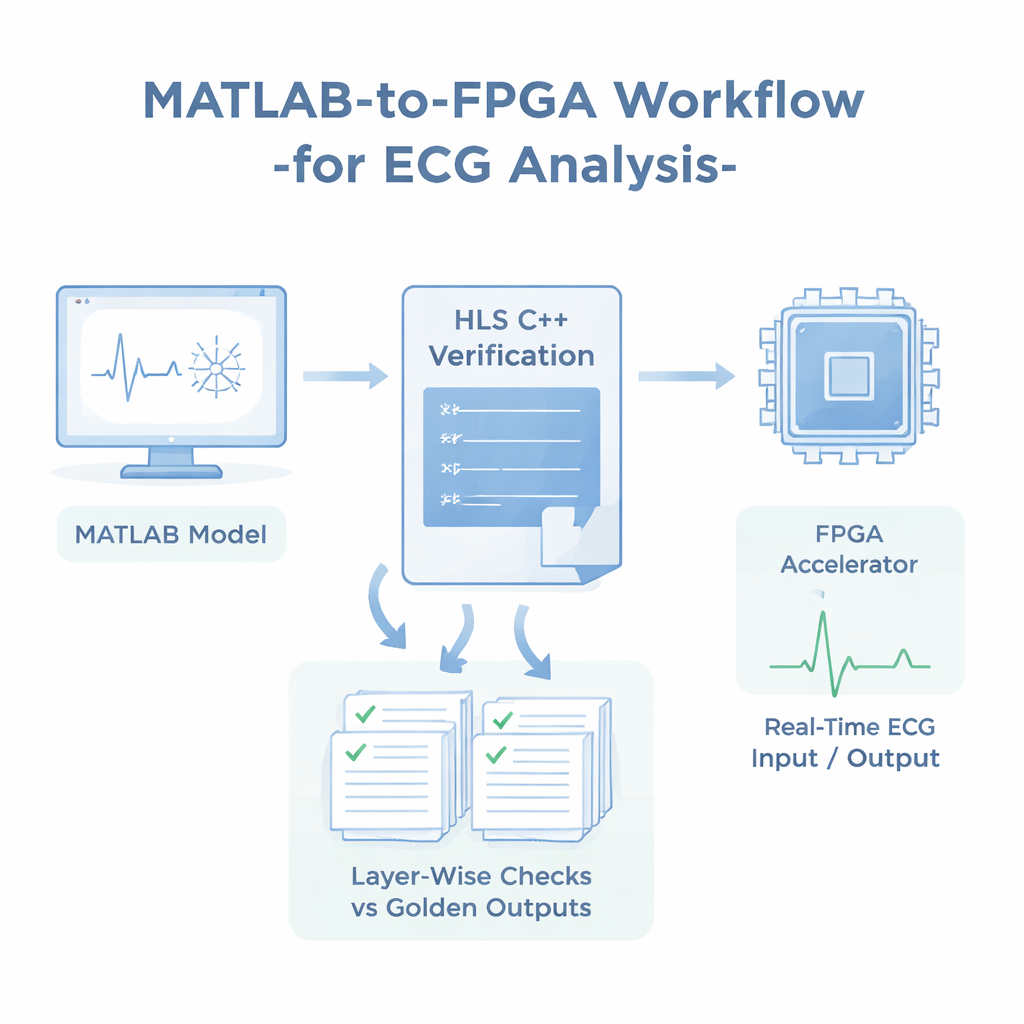

De MATLAB a C++ y al FPGA, con los números controlados

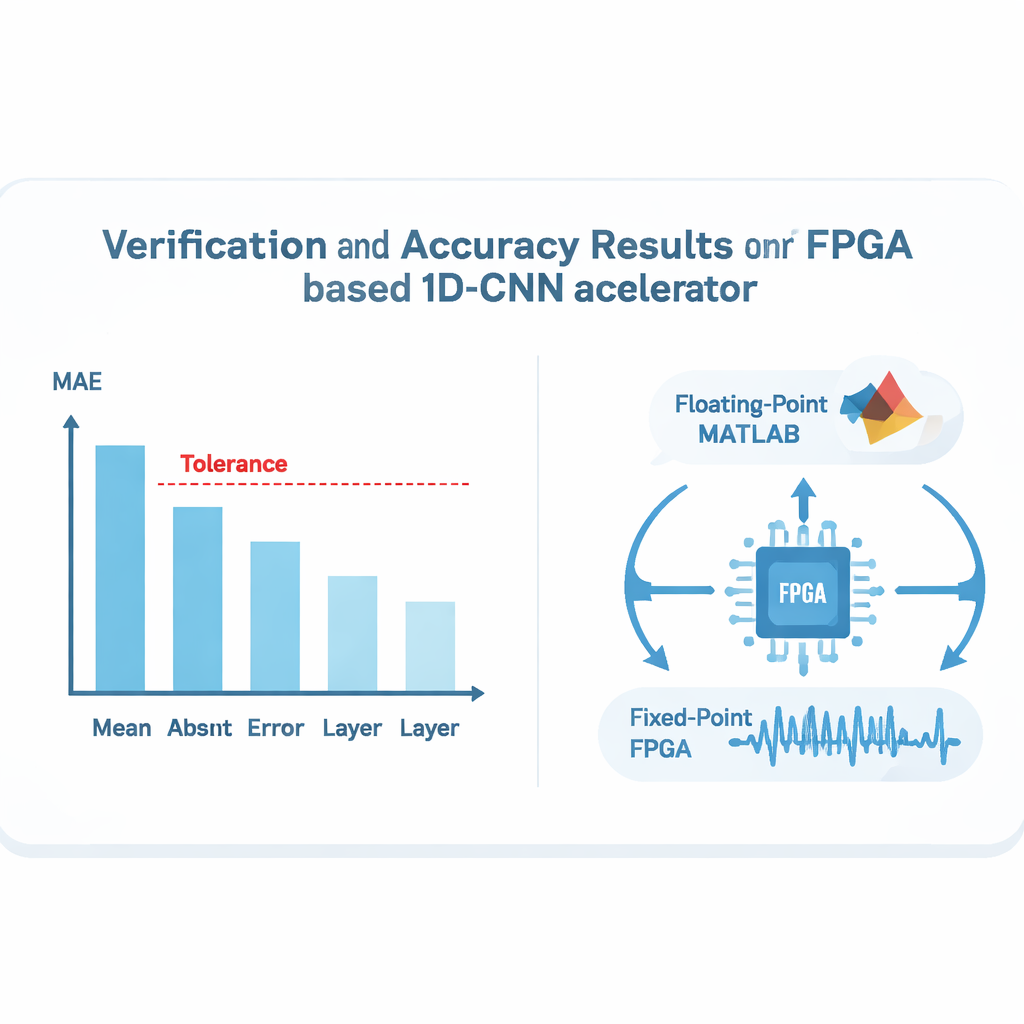

En lugar de pulsar un botón de “convertir” automático, la red se reimplementa manualmente en C++, siguiendo la misma organización de datos y pasos matemáticos que en MATLAB. Este código en C++ se usa luego con una herramienta de síntesis de alto nivel para generar hardware que se ejecuta en una placa FPGA PYNQ-Z1. En cada etapa —MATLAB, C++ y FPGA— las salidas de las capas se comparan con las salidas doradas almacenadas usando una medida simple: error absoluto medio, que cuantifica la diferencia numérica promedio entre dos conjuntos de resultados. El estudio fija una tolerancia estricta: todas las capas deben mantenerse por debajo de un error de 1.5×10⁻³. A lo largo de miles de muestras de ECG, cada capa probada cumple este objetivo, y la precisión final de clasificación se mantiene casi inalterada: alrededor de 98.3–98.4% en MATLAB y C++, y solo unos 0.2 puntos porcentuales menos en el FPGA, una diferencia coherente con los efectos esperados de usar números de punto fijo más cortos en hardware.

Hacer el hardware rápido sin romper las cuentas

Una vez asegurada la corrección, el diseño se ajusta para velocidad. Las partes más exigentes de la red —las capas convolucionales— se mapean en la lógica programable del FPGA, usando aritmética en punto fijo para mayor eficiencia, mientras que tareas menos pesadas como el cálculo final de softmax se ejecutan en el procesador integrado de la placa con números en coma flotante normales. Técnicas como el pipeline de bucles, el desenrollado de bucles y la división cuidadosa de la memoria en bancos paralelos permiten que distintas partes del cómputo y las transferencias de datos se ejecuten simultáneamente. Una versión optimizada del hardware procesa una ventana de latido en alrededor de 1.7 milisegundos y cabe holgadamente dentro de los límites de recursos y potencia del FPGA, todo ello preservando el comportamiento numérico por capas del modelo original en MATLAB.

Qué supone esto para futuros dispositivos inteligentes

Para no especialistas, el mensaje clave es que ya es posible no solo acelerar un clasificador sofisticado de ritmos cardíacos desarrollado en MATLAB en un chip de bajo consumo, sino demostrar que el funcionamiento interno del chip coincide estrechamente con el modelo de software de referencia en cada capa. En lugar de perseguir la velocidad sacrificando la fiabilidad, este enfoque construye una pista de auditoría clara desde el código en coma flotante de MATLAB hasta el hardware en punto fijo del FPGA. La misma receta de verificación —guardar salidas doradas, comparar errores capa a capa frente a un umbral estricto y comprobar la precisión final— puede aplicarse a otras redes neuronales unidimensionales en ámbitos como monitores de salud vestibles, sensores industriales y vehículos inteligentes, ayudando a garantizar que cuando los algoritmos salen del laboratorio y pasan a los dispositivos, sus decisiones sigan siendo fiables.

Cita: Bal, S. Towards the transformation of MATLAB models into FPGA-Based hardware accelerators. Sci Rep 16, 5027 (2026). https://doi.org/10.1038/s41598-026-36033-z

Palabras clave: Aceleradores FPGA, Redes neuronales en MATLAB, Clasificación de arritmias ECG, Verificación de hardware, Deep learning en punto fijo