Clear Sky Science · es

Optimización del rendimiento de FETs de InSe mediante dieléctricos de alto k para aplicaciones analógicas/RF

Electrónica más rápida e inteligente sobre una lámina diminuta

Los dispositivos modernos —desde teléfonos 5G hasta radares y escáneres médicos— dependen de transistores capaces de amplificar señales débiles y operar a velocidades muy altas. Este artículo explora cómo un material ultrafino prometedor, el seleniuro de indio (InSe), podría afinarse para ofrecer una mayor ganancia de señal en futuros circuitos analógicos y de radiofrecuencia (RF), del tipo usado en comunicaciones inalámbricas y detección. Al elegir cuidadosamente la capa aislante que se sitúa junto al canal activo del transistor, los autores muestran cómo mejorar el rendimiento mientras gestionan el inevitable compromiso entre consumo y velocidad.

Nuevos materiales más allá del silicio cotidiano

Durante décadas, el silicio ha sido la base de la electrónica, pero los ingenieros buscan ahora materiales atómicamente delgados que pueden separarse en capas de solo unos pocos átomos. Estos materiales “2D” pueden ser flexibles, transparentes y muy eficientes en el transporte de carga eléctrica. El grafeno fue la primera estrella de esta clase, pero al carecer de una brecha de energía tiene dificultades en conmutación convencional. Materiales como el seleniuro de indio ofrecen un punto intermedio: mantienen los beneficios de las capas 2D al tiempo que tienen una brecha de energía que permite a los dispositivos conmutar limpiamente y operar con baja potencia. Estudios anteriores se centraron principalmente en InSe para lógica digital y detección de luz; este trabajo desplaza la atención hacia su papel en circuitos analógicos y RF, donde la amplificación suave y el comportamiento a alta frecuencia importan más que el simple conmutado binario.

Cómo cambiar la capa invisible altera el comportamiento del dispositivo

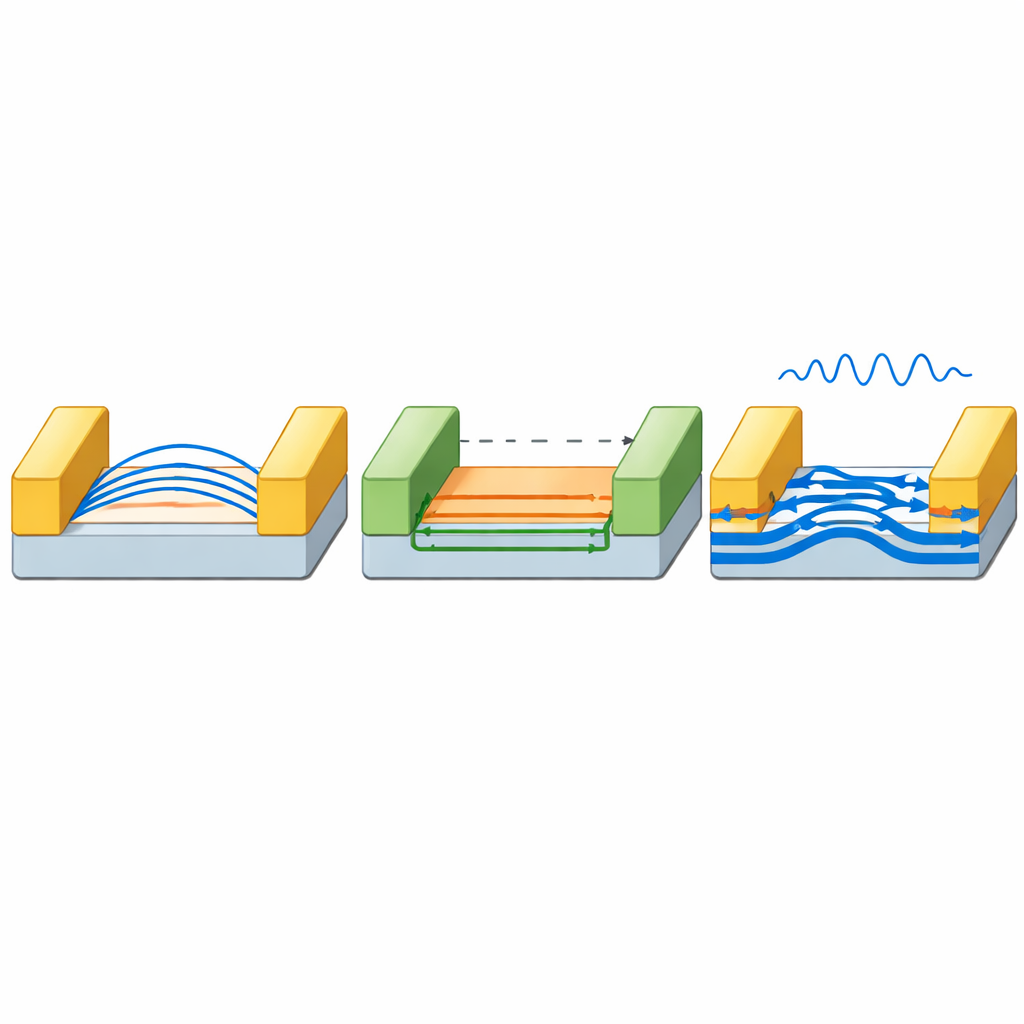

Cada transistor de efecto campo depende de una puerta que controla un canal delgado de carga usando una capa aislante, o dieléctrico, entre ambos. Aquí los autores simulan transistores de InSe con distintos materiales dieléctricos, desde un óxido estándar similar a los usados en chips de silicio hasta los llamados dieléctricos de alto k que almacenan carga eléctrica con mayor eficacia. Empleando modelos computacionales detallados a nivel cuántico, calculan cómo viajan los electrones a través de una cinta de InSe de escala nanométrica cuando varía la tensión de puerta. A medida que aumenta la constante dieléctrica, el campo eléctrico de la puerta «aprieta» el canal con más fuerza, atrayendo más carga en movimiento y reduciendo la barrera energética que los electrones deben superar. Esto conduce a una corriente mayor cuando el dispositivo está en conducción y a una separación más limpia entre los estados de encendido y apagado, lo cual es bueno tanto para uso digital como analógico.

Transformar un mejor control en mayor ganancia de señal

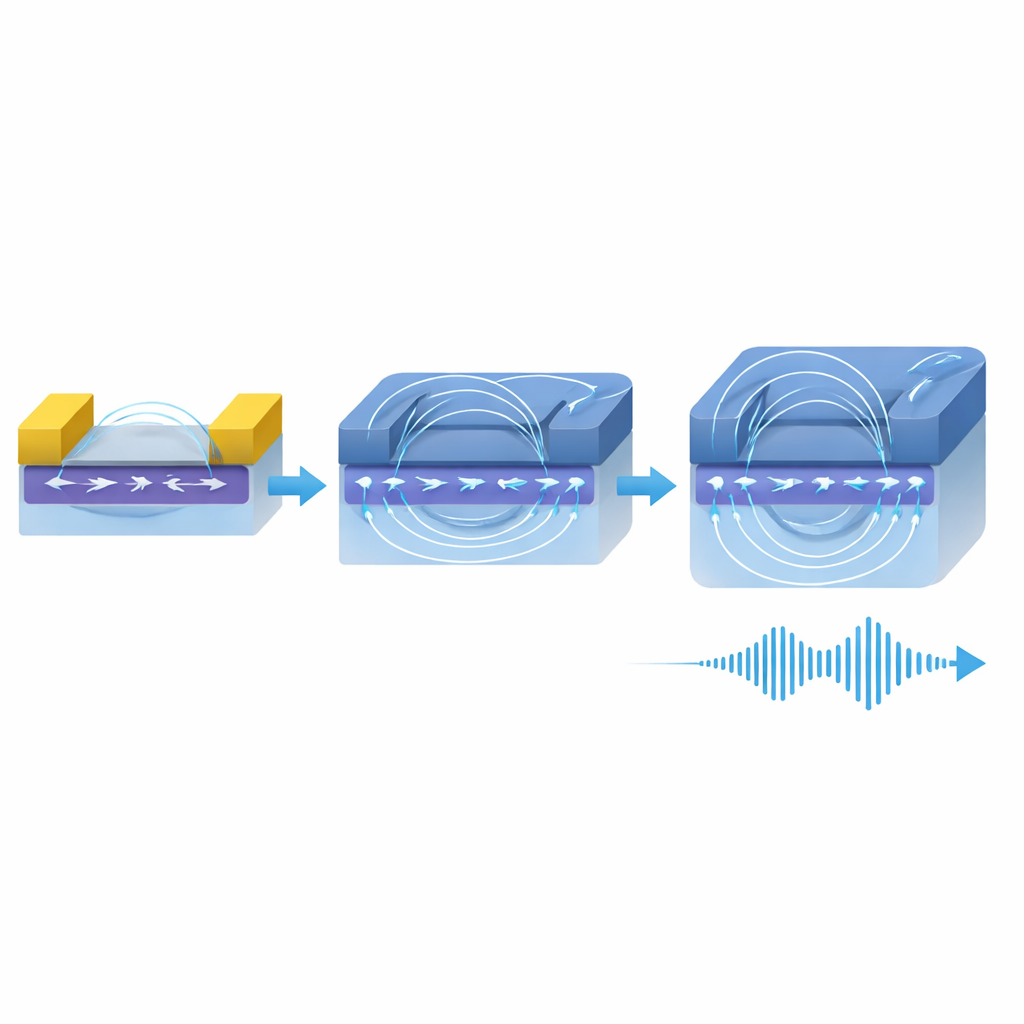

El objetivo real del estudio son las figuras de mérito analógicas y RF: magnitudes que describen qué tan bien un transistor puede amplificar señales y a qué coste en potencia o ancho de banda. Con materiales de alto k, los dispositivos de InSe simulados muestran casi el doble de transconductancia, una medida de cuán eficazmente los cambios en tensión de entrada se traducen en cambios en la corriente de salida. Esto, a su vez, eleva la ganancia intrínseca, que combina la transconductancia con la capacidad del dispositivo para mantener estable su tensión de salida. Los autores también examinan medidas compuestas que mezclan ganancia, velocidad y eficiencia —por ejemplo, cuánta ganancia se puede obtener a una frecuencia de operación dada o cuán eficaz se usa cada unidad de corriente para lograr amplificación. En todos estos casos, los dieléctricos de mayor k ofrecen ventajas claras, mejorando a veces métricas de rendimiento entre un 70 % y más del 150 %.

El coste del mayor empuje: un golpe a la velocidad máxima

No hay, sin embargo, almuerzo gratis. El mismo dieléctrico de alto k que refuerza el control de la puerta sobre el canal también aumenta la capacitancia del dispositivo, lo que significa que almacena más carga que debe moverse cada vez que el transistor conmuta. Si bien la corriente de conducción y la ganancia mejoran, esa carga extra ralentiza el ritmo máximo al que el transistor puede operar, reduciendo ligeramente la frecuencia de corte —el punto en el que deja de proporcionar amplificación útil. En las simulaciones, esta métrica de velocidad cae alrededor de un 10 % para el caso de k más alto en comparación con el óxido convencional. Los autores destacan esto como un compromiso de diseño: los ingenieros pueden ajustar la elección del dieléctrico según si lo más importante es una ganancia fuerte, la frecuencia máxima o un equilibrio óptimo entre ambos.

Qué significa esto para los chips inalámbricos y de detección futuros

En términos sencillos, el estudio muestra que al cambiar la delgada capa aislante de un transistor de InSe por un material con mejor «retención de carga», los ingenieros pueden fabricar conmutadores diminutos que amplifican señales con mucha más eficacia, aunque con una reducción moderada en la velocidad máxima. Esto hace que los dispositivos InSe con alto k sean especialmente atractivos para circuitos analógicos y RF de bajo voltaje, donde la ganancia limpia y la eficiencia energética importan más que alcanzar las frecuencias absolutas más altas. A medida que la modelización se vuelva más realista —incluyendo efectos como dispersión y defectos— y mejoren las técnicas de fabricación, tales transistores de materiales 2D a medida podrían sustentar una nueva generación de tecnologías de comunicación y detección flexibles y de bajo consumo.

Cita: Ahmad, M.A., Imam, M., Mech, B.C. et al. Performance optimization of InSe-FETs using high-k dielectric materials for analog/RF applications. Sci Rep 16, 9573 (2026). https://doi.org/10.1038/s41598-025-21242-9

Palabras clave: transistores de seleniuro de indio, dieléctricos de alto k, electrónica analógica RF, dispositivos semiconductores 2D, simulación en nanoelectrónica