Clear Sky Science · es

Computación fotónica neuromórfica con una memoria analógica electro‑óptica

Por qué importan cerebros de IA más rápidos y eficientes

La inteligencia artificial actual funciona sobre chips que consumen mucha energía y que continuamente trasladan datos entre memoria y procesadores. Este atasco desperdicia energía y ralentiza el sistema, especialmente a medida que los modelos de IA se hacen más grandes y complejos. La investigación presente introduce un nuevo tipo de circuito de computación basado en luz con memoria analógica integrada, diseñado para reducir drásticamente ese movimiento de datos y hacer que el hardware de IA futuro sea tanto más rápido como mucho más eficiente energéticamente.

La luz como nueva forma de calcular

En lugar de depender únicamente de electrones en cables metálicos, los procesadores fotónicos neuromórficos usan pulsos de luz para transportar y combinar información, imitando cómo fluyen las señales a través de redes de neuronas. La luz puede viajar en muchos colores simultáneamente por la misma vía, lo que permite un enorme paralelismo y retardos extremadamente bajos. Esto hace que los chips fotónicos sean atractivos para las intensas operaciones de “multiplicar y sumar” que dominan las redes neuronales. Sin embargo, la mayoría de los procesadores fotónicos existentes usan “pesos” fijos que deben entrenarse en otro hardware digital y luego copiarse. Eso limita su adaptabilidad y sigue dejando una gran carga sobre la memoria convencional y los circuitos de conversión.

Llevar la memoria junto a la luz

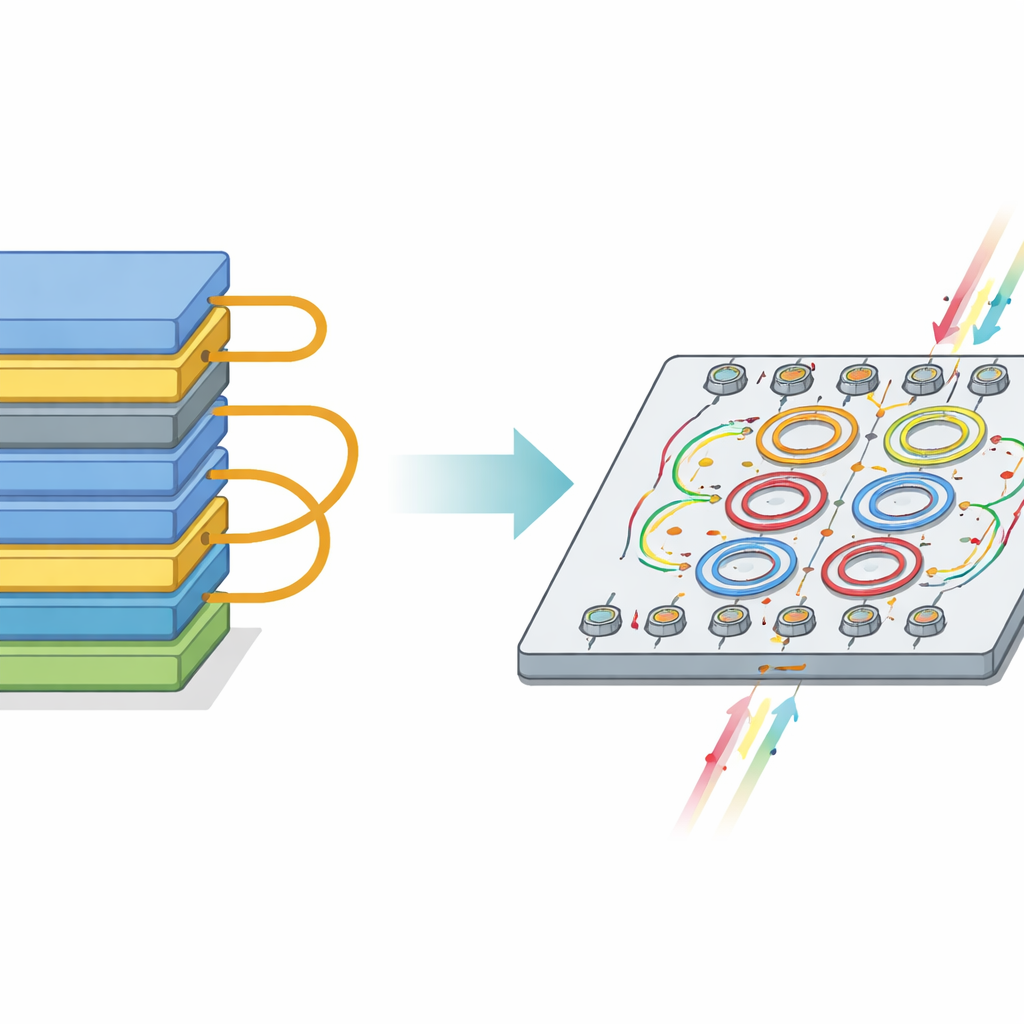

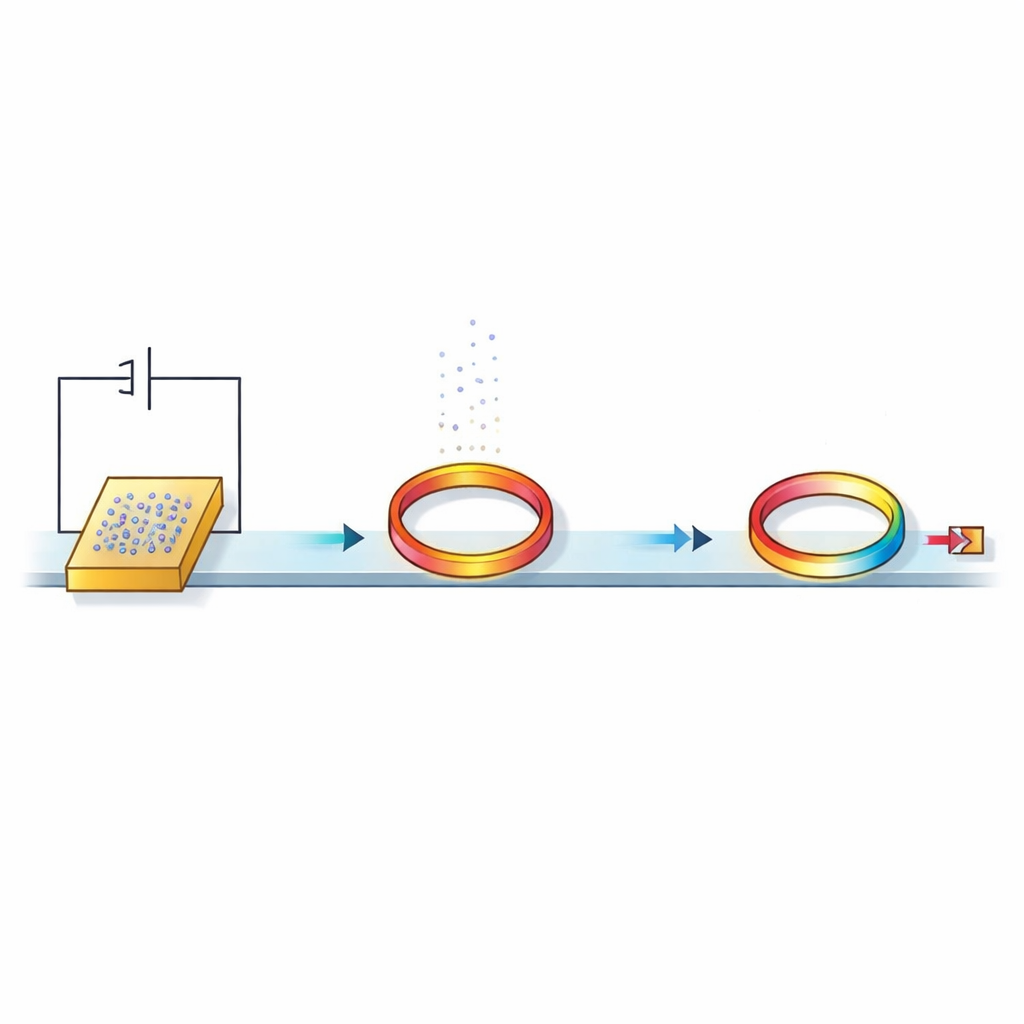

Los autores abordan esto añadiendo una memoria analógica sencilla y compatible con procesos de fundición directamente al lado de cada diminuto dispositivo óptico que representa un peso de la red neuronal. Su bloque constructivo clave es una memoria analógica electro‑óptica dinámica (DEOAM): un capacitor ordinario conectado a un anillo microscópico de silicio que guía la luz en un bucle. Un pequeño voltaje almacenado en el capacitor desplaza ligeramente cómo el anillo interactúa con la luz que pasa, fijando efectivamente la intensidad de una conexión neuronal. Porque el capacitor puede mantener ese voltaje durante un breve tiempo, ya no es necesario que convertidores digital‑a‑analógico especializados accionen cada anillo de forma continua. En su lugar, un conjunto mucho más reducido de convertidores puede actualizar muchos anillos en secuencia, mientras la memoria analógica mantiene los valores programados.

Cómo funciona el chip prototipo

El equipo fabricó un circuito fotónico neuromórfico en una plataforma comercial de silicio de 90 nanómetros, combinando electrónica estándar y nanofotónica en un único chip. Construyeron una matriz de resonadores anulares, cada uno emparejado con su propia celda de memoria capacitiva, además de conmutadores simples para escribir, mantener o reiniciar los voltajes almacenados. Cuando se escribe un voltaje, la respuesta del anillo a la luz láser cambia; cuando el circuito de escritura se desconecta, el capacitor conserva el voltaje y la luz sigue “viendo” el peso programado hasta que la carga se filtra gradualmente. Los investigadores midieron propiedades clave: la memoria puede escribirse en decenas de nanosegundos, retiene información utilizable durante alrededor de una milésima de segundo y ofrece aproximadamente cinco bits de precisión analógica. La luz recorre las rutas ópticas en picosegundos, por lo que la propia computación es extremadamente rápida en comparación con el tiempo durante el cual los valores de memoria permanecen válidos.

Pruebas con una red neuronal realista

Para entender qué implican estos límites de hardware para la IA práctica, los autores simularon cómo se comportaría un banco de pesos así dentro de una pequeña red de reconocimiento de imágenes entrenada con dígitos manuscritos del conjunto de datos MNIST. Mapearon una red de tres capas—784 entradas, 50 neuronas ocultas y 10 salidas—en matrices realistas de anillos y memorias analógicas, incluyendo ruido, precisión limitada, retención finita y otras imperfecciones. El estudio muestra que con al menos unos cuatro bits de control durante la inferencia, y más durante el entrenamiento completo en chip, el sistema aún puede alcanzar más del 95 por ciento de precisión en clasificación. También encontraron que mientras el tiempo de retención de la memoria sea al menos 100 veces mayor que el tiempo que tarda una entrada en atravesar la red, la precisión se mantiene por encima del 90 por ciento a pesar de que los pesos se “filtran” lentamente. En otras palabras, una memoria analógica con vida útil modestamente corta y con fugas puede seguir siendo muy útil cuando la computación fotónica es tan rápida.

Ahorro de energía y compensaciones de diseño

Un beneficio central de DEOAM es la drástica reducción en el número de convertidores digital‑a‑analógico. En diseños convencionales, cada peso óptico necesita su propio convertidor, por lo que la cantidad crece con el cuadrado del tamaño de la red. Con DEOAM, los convertidores se comparten a lo largo de filas o columnas y la cantidad crece solo de manera lineal. Usando mediciones reales de su prototipo y datos publicados para memorias y circuitos convertidores estándar, los autores estiman que una arquitectura fotónica integrada con memoria analógica puede reducir el consumo energético en más de un factor de 26 en comparación con esquemas tradicionales de SRAM más convertidor. También analizan cómo el ruido, el tamaño de lote durante el entrenamiento y la necesidad de refrescos periódicos de la memoria analógica afectan el rendimiento global, esbozando reglas de diseño prácticas para futuros sistemas a gran escala.

Qué significa esto para los chips de IA del futuro

Para no especialistas, el mensaje principal es que este trabajo muestra una vía realista hacia hardware de IA que es a la vez extremadamente rápido y dramáticamente más eficiente en energía, permitiendo que la luz haga los cálculos mientras memorias analógicas sencillas mantienen los ajustes en su lugar. Aunque estas memorias se desvanecen lentamente, la red puede tolerar e incluso aprovechar esa “pérdida” como una forma de regularización, ayudando a evitar el sobreajuste. Al entrelazar la memoria directamente en la estructura óptica del chip y reducir drásticamente los costosos pasos de conversión, los procesadores fotónicos neuromórficos como este podrían alimentar sistemas de IA futuros que aprendan sobre la marcha, se adapten a condiciones cambiantes y operen a alta velocidad sin las enormes facturas energéticas de los centros de datos actuales.

Cita: Lam, S., Khaled, A., Bilodeau, S. et al. Neuromorphic photonic computing with an electro-optic analog memory. Nat Commun 17, 2472 (2026). https://doi.org/10.1038/s41467-026-69084-x

Palabras clave: fotónica neuromórfica, memoria analógica, computación óptica, IA eficiente en energía, fotónica de silicio