Clear Sky Science · en

Oxide semiconductor gain cell-embedded memory: materials and integration strategies for next generation on-chip memory

Why Faster, Smarter Memory Matters

Our phones, laptops and data centers keep getting more powerful, yet a hidden speed limit remains: moving data between the processor and memory. This article explores a new kind of on-chip memory that could ease this “memory wall,” making future computers faster and more energy-efficient for tasks like artificial intelligence, cloud computing and everyday apps. By rethinking how memory cells are built and what materials they use, researchers aim to pack far more data close to the processor while cutting power use and heat.

The Bottleneck Inside Modern Computers

For decades, processor performance has improved much faster than the main memory that feeds it data. This mismatch, known as the memory wall, means fast chips often sit idle waiting for information. Designers have tried to soften this bottleneck with multiple layers of cache memory located on the processor itself. Today’s caches rely on a type of memory called SRAM, which is very fast but bulky and power-hungry because each bit of data needs six transistors. To get more capacity, companies stack SRAM chips in three dimensions or add embedded DRAM on the chip, but conventional DRAM still depends on tiny capacitors that are difficult to manufacture at extreme scales and hard to integrate with standard logic circuits.

A Different Kind of Memory Cell

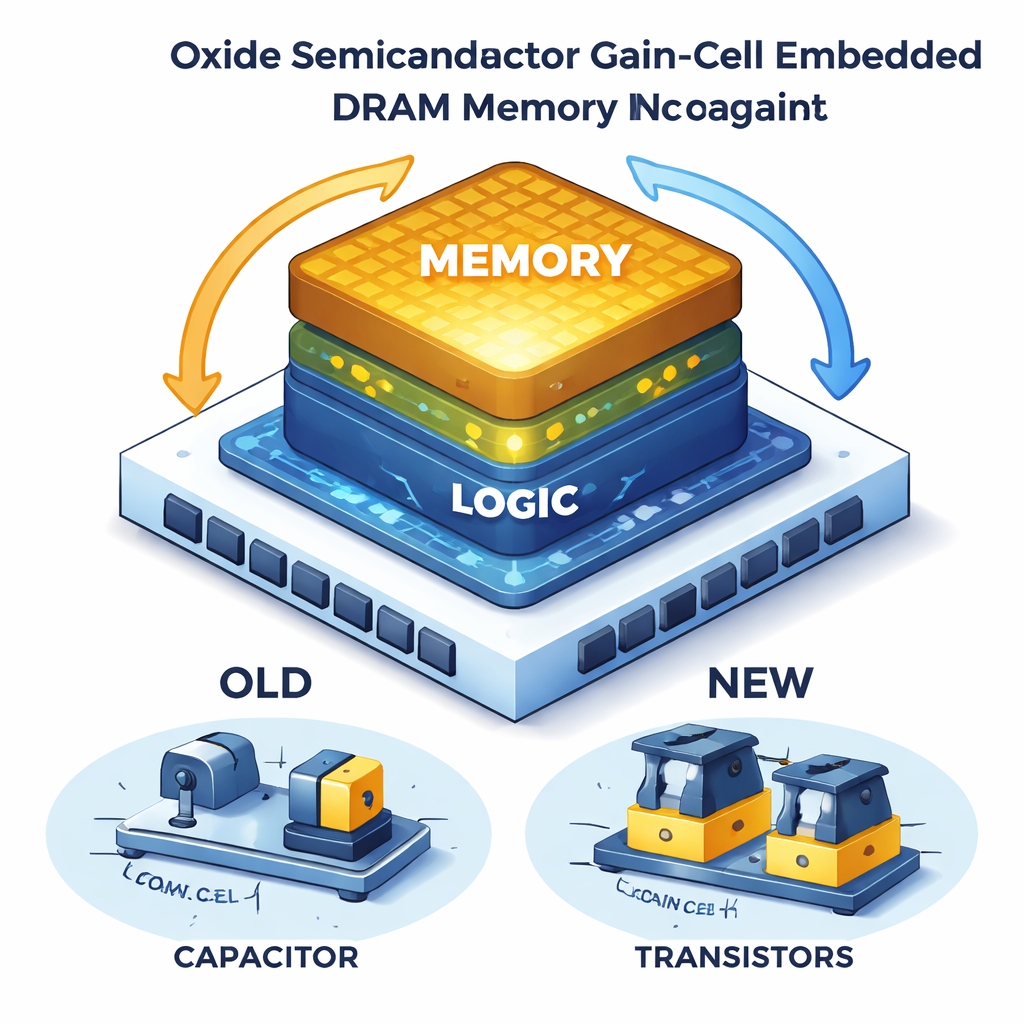

The paper focuses on an alternative called gain-cell embedded DRAM, or GC-eDRAM. Instead of using a separate capacitor to store charge, a gain cell uses only transistors to hold data, simplifying the structure and making it friendlier to standard chip manufacturing. This design naturally fits three-dimensional stacking above logic circuits, promising high-density “memory-on-logic” layouts. Another advantage is its “non-destructive read” behavior: reading a stored value does not immediately drain it, which can reduce how often the memory must be refreshed. However, in traditional silicon versions, the stored charge leaks away in less than a millisecond, so frequent refresh operations still waste energy and limit usefulness.

Oxide Semiconductors: Quieter, Cooler Switches

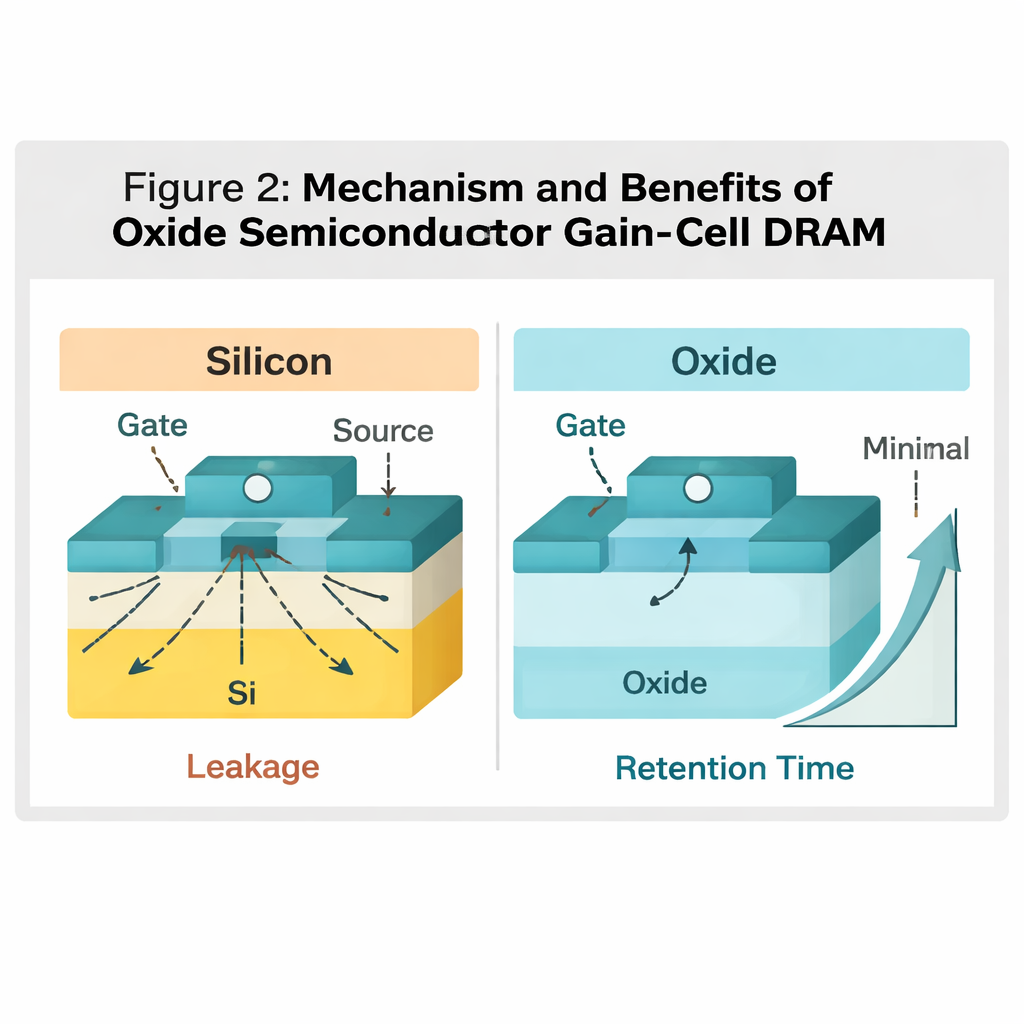

To overcome leakage in gain cells, the authors highlight oxide semiconductors—materials such as indium gallium zinc oxide (IGZO) and related compounds—as new channel materials for the transistors. These oxides have a wide energy gap, which strongly suppresses unwanted current when a transistor is supposed to be off. Experiments have measured off-currents so tiny they are near the limits of test equipment, and prototype gain cells now hold data for many seconds, hours or even more than a day, compared with thousandths of a second in silicon designs. Crucially, these oxides can be deposited at relatively low temperatures compatible with the “back-end” of chip fabrication, allowing engineers to build dense memory layers directly on top of existing silicon logic without damaging it.

Building Upward: 3D Stacks and Tiny Transistors

As chips continue to shrink, simply making transistors smaller brings new problems, like poor control over the channel and rising leakage. The paper reviews advanced transistor shapes that wrap the gate around the channel (gate-all-around and channel-all-around designs) to maintain tight control even at nanometer sizes. Using oxide semiconductors in these multi-gate structures, researchers have demonstrated very short channels, extremely low leakage and strong data retention while stacking multiple memory layers vertically. Some experimental designs already reach or surpass the area efficiency of today’s best DRAM cells, suggesting that future chips could host enormous memory capacity in a very small footprint right above the processor cores.

From Lab Materials to Reliable Products

Turning these promising devices into practical memory requires careful materials engineering. The article describes how tweaking the mix of metals in the oxide, controlling oxygen content and crystallizing the films can balance high speed with long-term stability. It also covers ways to manage defects, hydrogen contamination, and the delicate interfaces between oxides and insulating layers so that devices stay stable under heat and prolonged operation. Finally, it discusses engineering the metal connections so that contact resistance does not cancel out the benefits of the new materials. Together, these strategies aim to deliver memory that is both dense and trustworthy enough for large-scale manufacturing.

What This Means for Everyday Computing

The authors conclude that oxide semiconductor gain-cell memories could reshape how future chips are built. By combining tiny, low-leakage memory cells with 3D stacking over logic circuits, designers could place far more fast memory next to the processor while keeping power use in check. This would ease the memory wall, helping everything from AI accelerators to cloud servers and personal devices run faster and more efficiently. Although challenges remain in reliability, manufacturing uniformity and full-chip integration, the work reviewed here outlines a clear path toward more compact, powerful and energy-conscious computing systems.

Citation: Chung, S.W., Yoon, S.H. & Jeong, J.K. Oxide semiconductor gain cell-embedded memory: materials and integration strategies for next generation on-chip memory. Commun Eng 5, 39 (2026). https://doi.org/10.1038/s44172-026-00616-5

Keywords: on-chip memory, oxide semiconductors, DRAM scaling, 3D integrated circuits, AI hardware