Clear Sky Science · en

Thermal management of 3-D heterogeneously integrated microelectronics: challenges and future research directions

Why stacking chips changes your everyday gadgets

From phones and laptops to data centers powering artificial intelligence, our electronics keep shrinking while doing more work than ever. To achieve this, engineers are now stacking different kinds of chips on top of each other, creating compact three-dimensional packages. This clever move boosts performance and cuts signal delays, but it also traps enormous amounts of heat in a tiny space. The reviewed article explains why heat has become one of the biggest threats to this new generation of electronics—and what researchers are doing to keep these tiny skyscrapers of silicon from overheating.

Building tiny high-rises of electronics

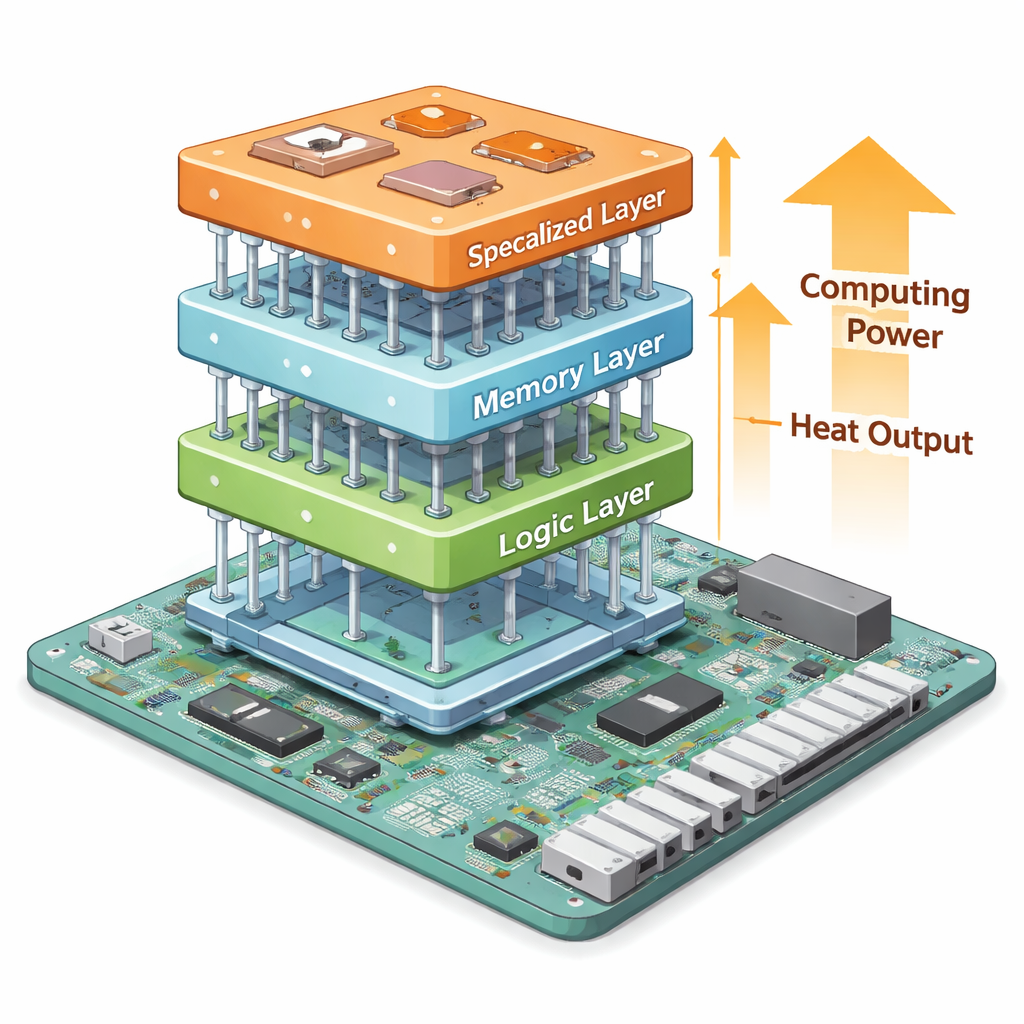

Traditional chips are mostly flat: circuits spread out side by side on a single slice of silicon. As it becomes harder to keep shrinking features in two dimensions, industry is turning to three-dimensional heterogeneous integration, where several layers of different chips—logic, memory, radio, photonics, and more—are stacked vertically and linked by metal pillars. This arrangement shortens communication paths and allows designers to mix and match technologies made in different factories. The result is faster processing, lower communication delay, and better energy use, which are especially valuable for artificial intelligence, cloud computing, and advanced communication systems.

The hidden cost of packing more power

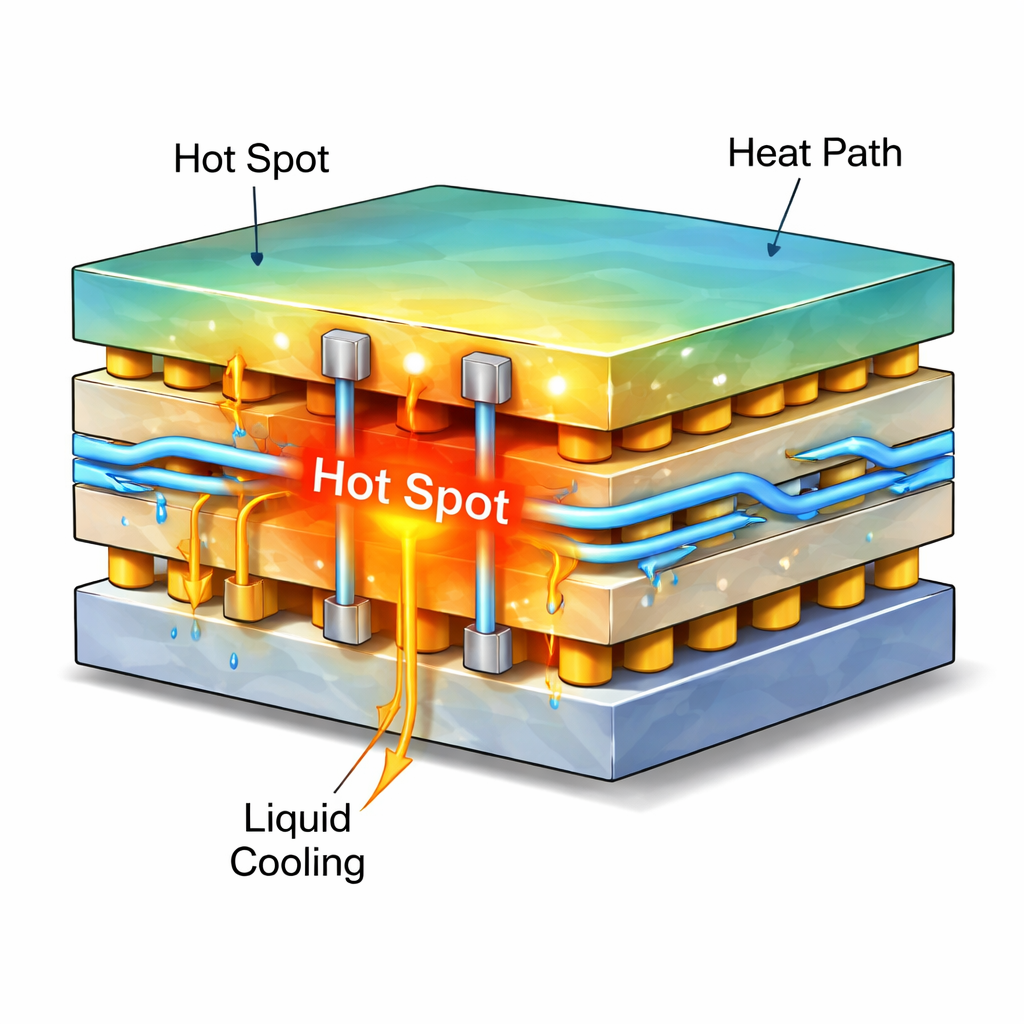

Stacking chips so tightly comes with a serious downside: heat has a harder time escaping. Each layer generates heat through familiar electrical losses—resistance in wires, switches turning on and off, and tiny leakage currents that never fully turn off. In 3-D stacks these losses add up, and the middle layers, farthest from any cooling surface, tend to become the hottest. Temperature can rise unevenly, creating hotspots that are only a fraction of a millimeter wide but far hotter than their surroundings. Even a few degrees above the intended operating range can sharply reduce reliability, speed up wear, and in extreme cases trigger a self-reinforcing loop of rising temperature and rising current known as thermal runaway.

When heat spreads, bends, and breaks things

The review explains that temperature problems are not just about a chip running warm; they can quietly damage the entire package. Different materials in the stack—silicon, metals, polymers, and ceramics—expand by different amounts when heated. As the device cycles between idle and full power, these mismatches create mechanical stress that can crack solder joints, open gaps at interfaces, and damage the metal-filled vertical connections. At the same time, uneven heating causes thermal crosstalk: a hot logic die can unintentionally warm a low-power memory or optical layer above it, degrading its performance. Over time, small voids and cracks around the heat-carrying structures grow, adding extra thermal resistance and making it even harder to remove heat where it matters most.

New tricks for moving heat in three dimensions

To cope with these challenges, researchers are rethinking every part of the thermal path. Some strategies aim to spread heat more effectively inside the stack by using better underfills and interlayer materials that conduct heat well without disturbing electrical signals. Others repurpose the vertical metal pillars as dedicated heat conduits or add extra, heat-only pillars alongside signal paths. The review also highlights a shift toward bringing the cooling system much closer to the heat source. Tiny liquid channels and forests of microscopic pin-fins can be etched directly into or between the chip layers, allowing coolant to flow within tens of micrometers of the hottest spots. These embedded coolers can remove extreme heat fluxes while tailoring flow to the needs of each layer, but they introduce new issues of mechanical strength, manufacturing complexity, and long-term reliability under pressure and moisture.

Where the field is headed next

Overall, the article concludes that controlling heat will largely determine how far 3-D stacked electronics can progress. No single solution is enough: chip layout, materials, vertical connections, interface layers, and cooling channels must be designed together rather than in isolation. Future work will focus on scalable ways to combine high-conductivity, mechanically compatible materials with manufacturable, low-temperature processes, as well as smarter design tools that treat thermal behavior on equal footing with speed and power. If these hurdles can be overcome, three-dimensional chip stacks could keep delivering more computing power in ever smaller packages—without burning themselves out.

Citation: Sharma, M.K., Ramos-Alvarado, B. Thermal management of 3-D heterogeneously integrated microelectronics: challenges and future research directions. Commun Eng 5, 28 (2026). https://doi.org/10.1038/s44172-026-00590-y

Keywords: 3D chip stacking, electronics cooling, thermal management, microfluidic cooling, heterogeneous integration