Clear Sky Science · en

Design of low power and high speed approximate multipliers utilizing current mode 4 to 2 compressors based on CNTFET technology

Sharper images with less energy

Every time your phone snaps a photo, streams a video, or runs an AI filter, it performs millions of tiny multiplications. Doing all this math exactly costs energy and slows things down, yet the human eye often cannot see small numerical errors. This paper shows how to deliberately “relax” some of that math using a new kind of circuitry, cutting power and delay while keeping images visually indistinguishable from exact results.

Why imperfect math can still look perfect

Many modern applications—like image processing, video, and machine learning—are naturally tolerant to small errors. A slight change in the brightness of one pixel, or a tiny shift in a filter response, is usually invisible to us. The authors exploit this by using approximate multipliers: circuits that trade a bit of arithmetic accuracy for big savings in power, chip area, and speed. They focus on 8×8 multipliers, a common building block in digital signal processing, and evaluate not just numerical error, but how these approximations actually affect final image quality using standard metrics such as peak signal‑to‑noise ratio (PSNR) and structural similarity (MSSIM).

A new kind of building block for fast multipliers

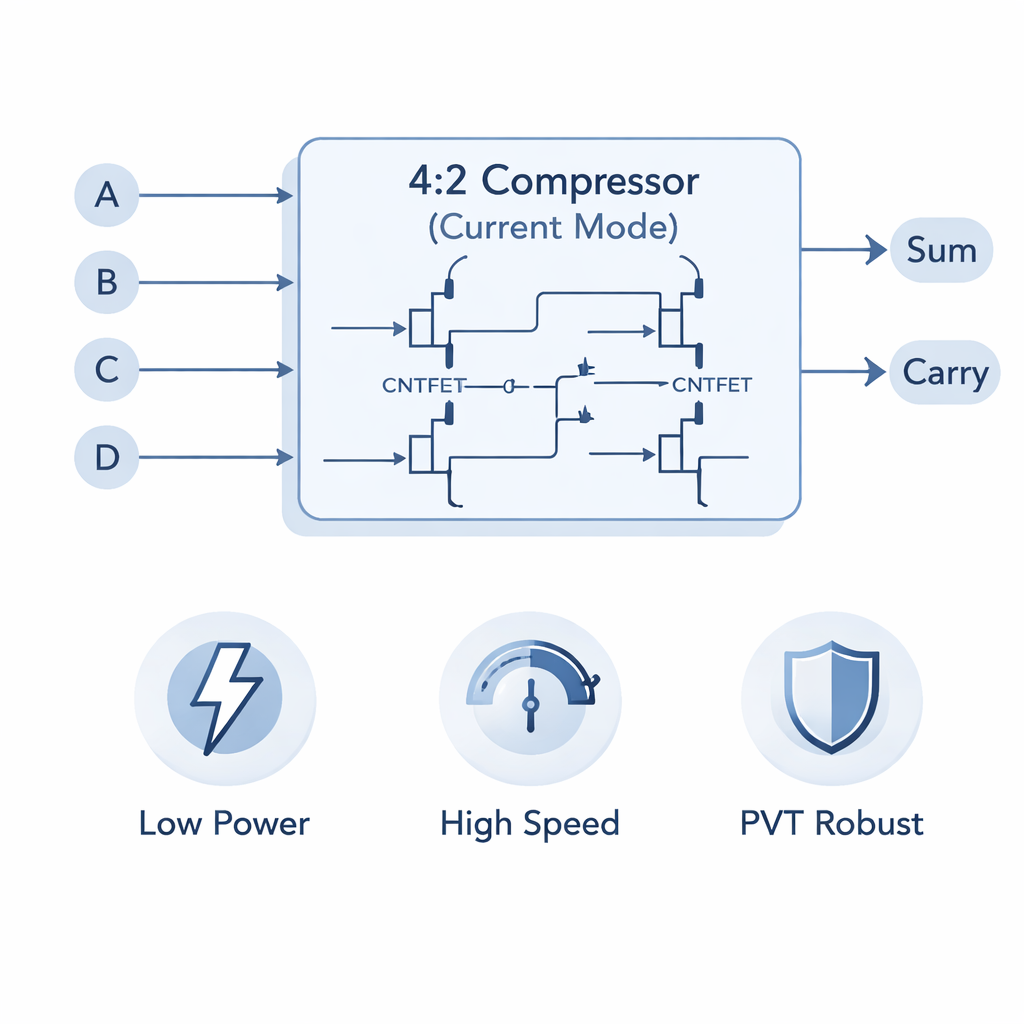

At the heart of the design lies a component called a 4:2 compressor, which reduces four input bits and a carry input into two outputs, “sum” and “carry.” Traditional compressors use voltage‑mode CMOS or FinFET transistors, which become harder to scale at very small sizes. This work instead combines current‑mode logic with 7‑nanometer carbon‑nanotube field‑effect transistors (CNTFETs). By viewing information as currents rather than just voltages, the circuits can directly sum currents without heavy threshold‑detection circuitry. CNTFETs, whose threshold voltage can be tuned by changing nanotube diameter, let the designers build majority, XOR, and other basic gates with very few transistors, high noise margins, and low energy per operation.

Six flavors of “good enough” compressors

The authors propose six new 4:2 compressor designs. Four are single‑mode approximate compressors, each exploring a different way to simplify the internal logic and reduce power, delay, or error. Two more are dual‑function compressors that can switch between exact and approximate behavior using power gating, so only one part of the circuit is active at a time. Across these options, they carefully measure error distance (how far an output can deviate from perfect), how often outputs are still exact, and how robust the circuits are to changes in process, voltage, and temperature. Thanks to the CNTFET current‑mode approach, the new compressors are 30–50% less sensitive to such variations than comparable CMOS or FinFET designs, while consuming only about 12–25 microwatts with sub‑nanosecond internal delays.

Two multiplier designs for images and AI

Using these compressors, the team constructs two 8×8 Dadda multipliers. The first type uses approximate compressors in every column, maximizing energy savings. The second type takes a more selective approach: it completely drops the four least significant output columns (truncation), uses approximate compressors in the middle columns, and keeps exact compressors in the most significant columns where mistakes would be visually obvious. Simulations in HSPICE and MATLAB show that, for the best configuration, power drops to about 0.52 mW, latency to 1.88 ns, and power‑delay product to 0.97 pJ—large improvements over prior approximate multipliers.

What this means for real images

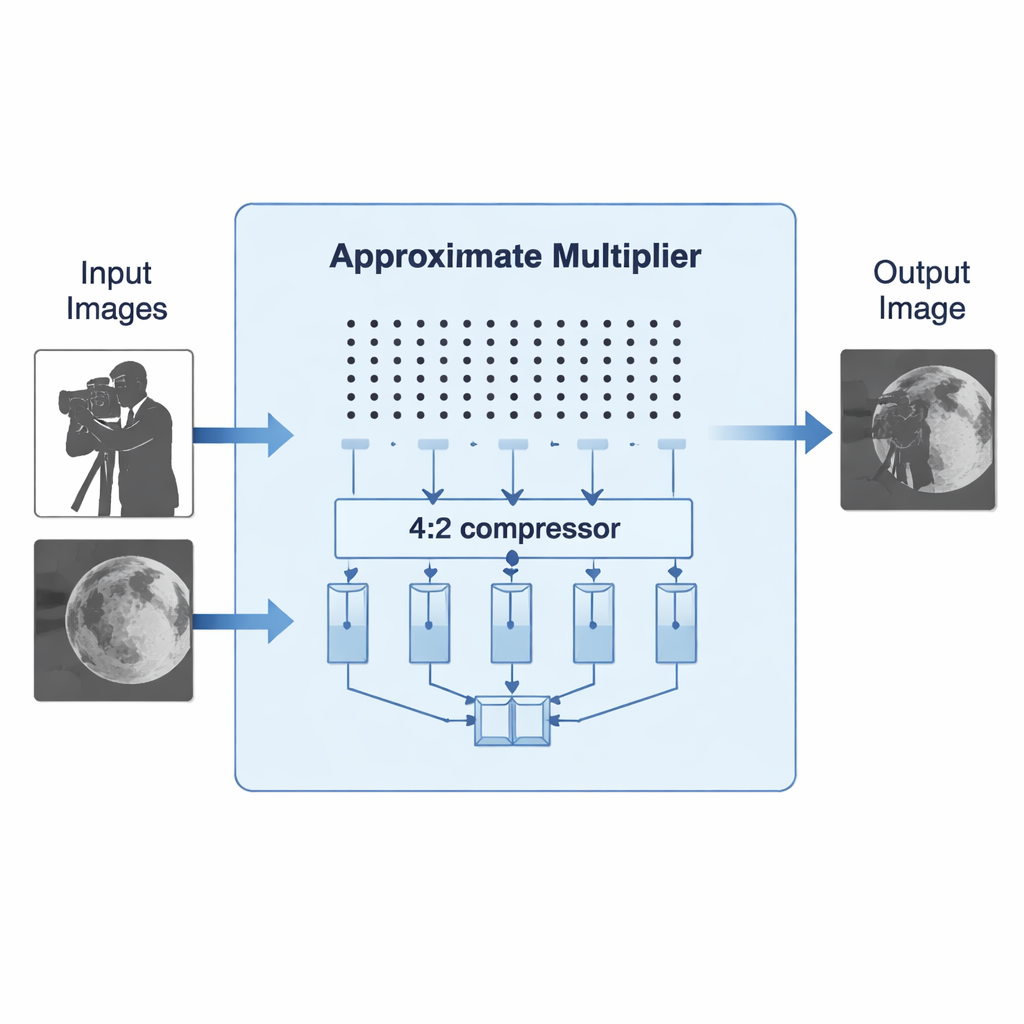

To test whether these savings matter in practice, the authors run standard image tasks such as multiplying two benchmark images (the classic “cameraman” and “moon”) and sharpening. They compare images produced by exact multipliers and their approximate designs. Despite internal arithmetic errors of up to ±2 in some cases, the best proposed multiplier improves structural similarity (MSSIM) from about 60% in earlier approximate designs to roughly 97%, and boosts PSNR by 15–20%. Visually, the images remain crisp and detailed, while the underlying hardware consumes far less energy and runs faster, making this approach attractive for low‑power cameras, portable vision systems, and edge AI devices where battery life and speed matter more than perfect arithmetic.

Citation: Foroutan, P., Navi, K. Design of low power and high speed approximate multipliers utilizing current mode 4 to 2 compressors based on CNTFET technology. Sci Rep 16, 4834 (2026). https://doi.org/10.1038/s41598-026-35104-5

Keywords: approximate multipliers, CNTFET, image processing, low power circuits, current mode logic