Clear Sky Science · de

Skalierbare und robuste multi-bit spintronische Synapsen für analoges Rechnen im Speicher

Warum „intelligenterer“ Speicher für Alltags‑KI wichtig ist

Von Sprachassistenten bis hin zu Foto‑Apps stützt sich moderne künstliche Intelligenz stark auf tiefe neuronale Netze – Programme, die Millionen winziger numerischer „Gewichte“ verarbeiten, um Entscheidungen zu treffen. Das ständige Hin- und Herschieben dieser Gewichte zwischen Speicher und Prozessor verbraucht weit mehr Energie als die eigentlichen Rechnungen. Diese Arbeit untersucht eine neue Art magnetischer Speicherzelle, die diese Gewichte nicht nur speichert, sondern auch hilft, die Berechnungen direkt dort auszuführen, wo die Daten liegen. Das verspricht schnellere und effizientere KI‑Hardware.

Gehirnähnliches Rechnen direkt im Speicherchip

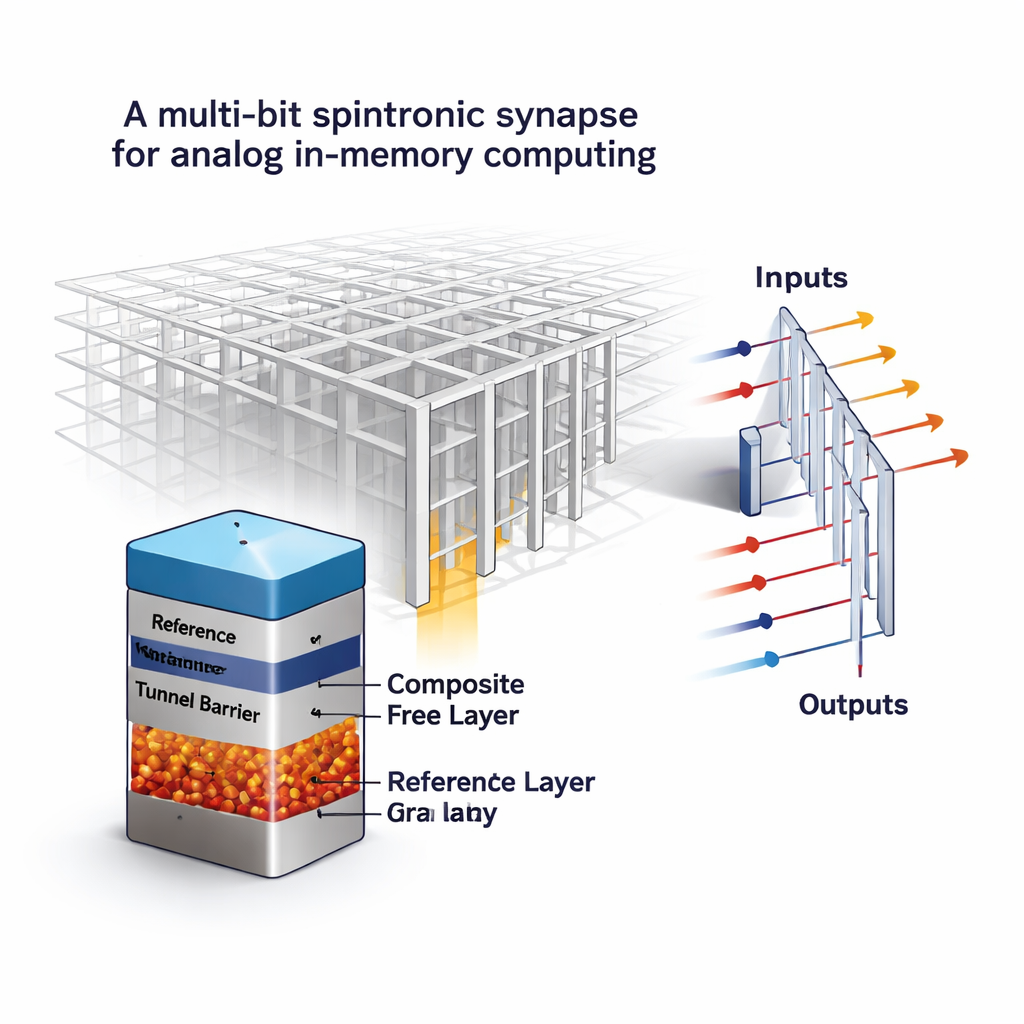

Heutige Computer folgen dem klassischen von‑Neumann‑Prinzip, bei dem Daten ständig zwischen Speicher und einem separaten Prozessor hin und her geschoben werden. Neuronale Netze, die im Kern auf massiven Matrix‑Vektor‑Multiplikationen beruhen, stoßen hier schnell an dieses Nadelöhr. Eine vielversprechende Alternative ist In‑Memory‑Computing: Ein großes Gitter (Crossbar‑Array) von Speicherzellen hält die Gewichte des Netzes und wandelt gleichzeitig anliegende Spannungen in Ausgangsströme um, die die Rechnung darstellen. Viele experimentelle Speicherbauelemente wurden für diese Rolle getestet, doch sie leiden oft unter Rauschen und driftenden Werten, was problematisch ist, wenn jede Zelle mehr als nur 0 oder 1 darstellen muss.

Magnetischen Speicher von An/Aus zu „analog“ verwandeln

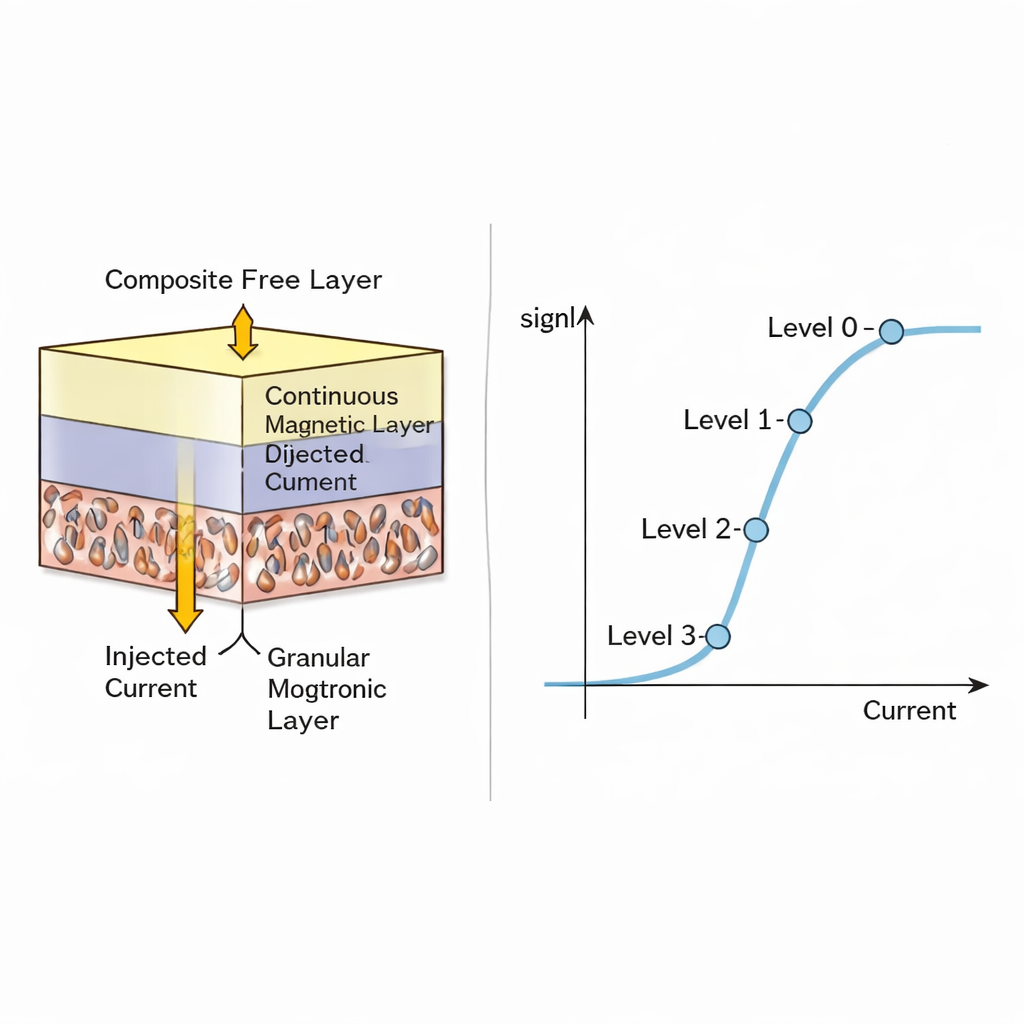

Die Autoren bauen auf magnetischem Direktzugriffsspeicher (MRAM) auf, einer nichtflüchtigen Technologie, die bereits für Geschwindigkeit, Langlebigkeit und Kompatibilität mit Standard‑Chipprozessen geschätzt wird. Eine konventionelle MRAM‑Zelle ist eine magnetische Tunnelverbindung: zwei magnetische Schichten, getrennt durch eine Isolatorschicht. Je nachdem, ob die Schichten gleichgerichtet oder entgegengesetzt sind, ist der elektrische Widerstand der Zelle niedrig oder hoch und kodiert ein einzelnes Bit. Der zentrale Kniff besteht hier darin, die „freie“ magnetische Schicht so umzudesignen, dass sie kein einheitlicher Block mehr ist, der sich auf einmal umschaltet. Stattdessen kombiniert das neue Design einen sehr dünnen durchgehenden Film auf einer dickeren, granularen magnetischen Schicht, die aus vielen winzigen magnetischen Körnern besteht. Jedes Korn kann seine Richtung bei leicht unterschiedlichen Strömen umschalten, sodass der Gesamtwiderstand mehrere Zwischen‑, stabile Pegel annehmen kann, anstatt nur „niedrig“ und „hoch“.

Wie viele Abstufungen des Magnetismus sind nützlich?

Mithilfe detaillierter Computermodelle der magnetischen Dynamik zeigt das Team, dass das Einspeisen eines spinpolarisierten Stroms in diese zusammengesetzte Schicht einen schrittweisen Umschaltprozess Korn für Korn auslöst. Beim Durchfahren des Stroms zeichnen die mittlere Magnetisierung und damit der Widerstand eine glatte S‑förmige Kurve nach, die nahezu kontinuierliche analoge Zustände ermöglicht. Die Autoren untersuchen anschließend, wie Fertigungsunterschiede zwischen Zellen und zufällige thermische Effekte von einem Schreibzyklus zum nächsten diese Pegel stören. Sie finden, dass die mittleren Zustände etwas verrauschter sind, die Extremzustände (vollständig in die eine oder andere Richtung geschaltet) jedoch sehr stabil bleiben. Für realistisch dimensionierte Bauelemente (etwa 50–75 Nanometer Kantenlänge) kommen sie zu dem Schluss, dass vier zuverlässig unterscheidbare Widerstandslevel – äquivalent zu 2 Bit pro Zelle – praktikabel sind, ohne übermäßige Fehler.

Von der Einzelzelle zum vollständigen KI‑Beschleuniger

Um nützlich zu sein, muss dieses mehrstufige MRAM zuverlässig auslesbar und in vollständige Rechensysteme integrierbar sein. Die Autoren entwerfen und simulieren einen Sensorschaltkreis, der einen schnellen „Flash“ Analog‑Digital‑Wandler verwendet, um zwischen den vier Widerstandsleveln jeder Zelle zu unterscheiden. Sie untersuchen, wie der Kontrast zwischen dem höchsten und niedrigsten Leitfähigkeitszustand Lesezeit, Energieverbrauch und die Größe der Sensorschaltung beeinflusst und zeigen, dass besserer Kontrast direkt zu schnelleren und energieeffizienteren Lesevorgängen führt. Anschließend betten sie ihr 2‑Bit‑pro‑Zelle‑MRAM‑Modell in einen simulierten In‑Memory‑Beschleuniger ein, der ein ResNet‑18‑Netzwerk auf dem CIFAR‑10‑Bilddatensatz ausführt. Im Vergleich zu einer Basisversion mit standardmäßigen 1‑Bit‑MRAM‑Zellen verdoppelt die Multi‑Bit‑Variante annähernd die Speicherdichte und halbiert die benötigte Anzahl an Crossbar‑Tiles. Das führt zu Reduktionen von Chipfläche, Energie und Latenz um bis zu etwa das 1,8‑Fache und zu einer mehr als 3‑fachen Verbesserung der kombinierten Energie‑Latenz‑Metrik, bei im Wesentlichen unveränderter Erkennungsgenauigkeit des Netzes.

Wie es sich gegenüber anderen Speicherideen behauptet

Die Studie vergleicht diesen Ansatz auch mit konkurrierenden Technologien wie resistivem RAM und Phasenspeicher sowie mit anderen magnetischen Konzepten, die auf der Bewegung von Domänenwänden oder Skyrmionen beruhen. Während diese Alternativen ebenfalls analoge Verhaltensweisen erzeugen können, benötigen sie oft größere Bauelemente oder spezielle Formen und sind tendenziell unvorhersehbarer. Im Gegensatz dazu behalten die granularen MRAM‑Zellen die Fertigungsfreundlichkeit und Lebensdauer des Mainstream‑MRAM bei und gewinnen gleichzeitig zusätzliche Speicherlevel. Systemtests deuten darauf hin, dass MRAM‑basierte Synapsen unter realistischen Variationen die Erkennungsgenauigkeit neuronaler Netze deutlich besser erhalten als ähnliche Entwürfe auf Basis variablerer resistiver Speicher, insbesondere wenn Netze zur weiteren Energieeinsparung ausgedünnt (sparse) werden.

Was das für die zukünftige Alltags‑KI bedeutet

Einfach ausgedrückt haben die Autoren eine Methode gezeigt, mit der eine bewährte magnetische Speichertechnologie gelehrt wird, nicht nur Nullen und Einsen zu speichern, sondern kleine analoge Gewichtswerte direkt in einer kompakten Zelle. Durch gezielte Ingenieursarbeit an einer geschichteten Struktur, die das magnetische Verhalten auf viele kleine Körner verteilt, erzielen sie mehrere stabile Widerstandslevel, die robust genug für reale KI‑Aufgaben sind. Werden diese Zellen in großen Arrays angeordnet und mit geeigneten Sensorschaltungen kombiniert, können sie die Kernberechnungen des Deep Learning ausführen und gleichzeitig den Datentransport drastisch reduzieren. Sollte dies in Hardware realisiert werden, könnten solche multi‑bit spintronischen Synapsen künftige KI‑Systeme – in Rechenzentren, Smartphones oder eingebetteten Sensoren – schneller und energieeffizienter machen, ohne die Genauigkeit zu opfern.

Zitation: Gupte, K.K., Mugdho, S.S., Huang, C. et al. Scalable and robust multi-bit spintronic synapses for analog in-memory computing. npj Unconv. Comput. 3, 8 (2026). https://doi.org/10.1038/s44335-026-00055-7

Schlüsselwörter: in-memory computing, spintronischer Speicher, MRAM, neuromorphe Hardware, tiefe neuronale Netze