Clear Sky Science · de

Gain-Cell-Embedded-Speicher mit Oxid-Halbleitern: Materialien und Integrationsstrategien für die nächste Generation On-Chip-Speicher

Warum schnellere, intelligentere Speicher wichtig sind

Unsere Telefone, Laptops und Rechenzentren werden immer leistungsfähiger, doch eine versteckte Geschwindigkeitsgrenze bleibt bestehen: das Verschieben von Daten zwischen Prozessor und Speicher. Dieser Artikel untersucht eine neue Art von On-Chip-Speicher, die diese „Speicherwand“ abmildern könnte und künftige Rechner für Aufgaben wie künstliche Intelligenz, Cloud-Computing und Alltagsanwendungen schneller und energieeffizienter machen würde. Indem man die Architektur der Speicherzellen und die verwendeten Materialien neu denkt, zielen Forschende darauf ab, deutlich mehr Daten dicht am Prozessor unterzubringen und gleichzeitig Energieverbrauch und Wärmeentwicklung zu reduzieren.

Der Engpass innerhalb moderner Computer

Über Jahrzehnte hat sich die Prozessorleistung deutlich schneller verbessert als der Hauptspeicher, der ihn mit Daten versorgt. Diese Diskrepanz, bekannt als Speicherwand, sorgt dafür, dass schnelle Chips häufig untätig warten, bis Informationen ankommen. Designer haben versucht, diesen Engpass durch mehrere Ebenen von Cache-Speicher direkt auf dem Prozessor zu mildern. Die heutigen Caches basieren auf einem Speichertyp namens SRAM, der sehr schnell, aber platz- und energieintensiv ist, weil jedes Bit sechs Transistoren benötigt. Um mehr Kapazität zu erreichen, stapeln Unternehmen SRAM-Chips dreidimensional oder fügen eingebettetes DRAM auf dem Chip hinzu, doch konventionelles DRAM hängt weiterhin von winzigen Kondensatoren ab, die bei extremen Skalierungen schwer herzustellen sind und sich nur schwer mit Standard-Logikschaltungen integrieren lassen.

Eine andere Art von Speicherzelle

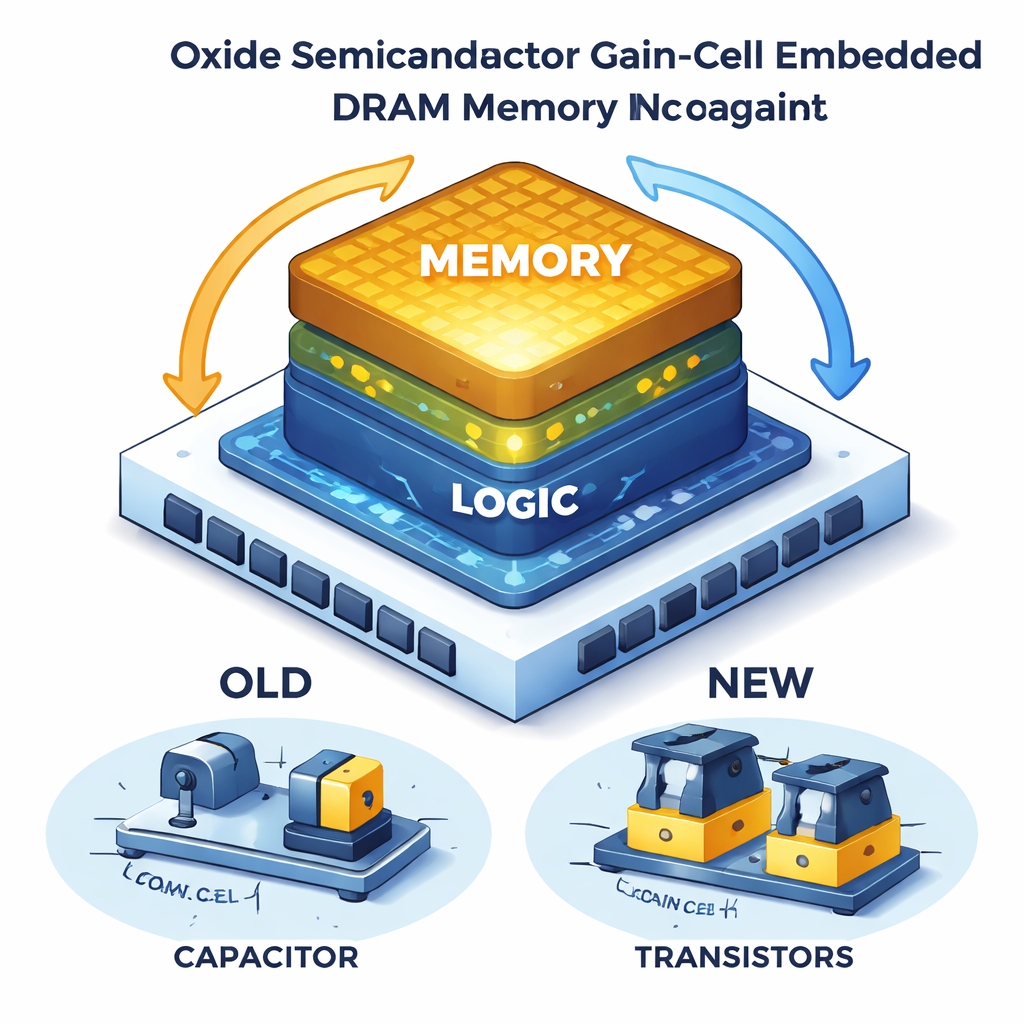

Die Arbeit konzentriert sich auf eine Alternative, genannt Gain-Cell-Embedded-DRAM oder GC-eDRAM. Anstelle eines separaten Kondensators zur Ladungsspeicherung verwendet eine Gain-Cell nur Transistoren zur Datenhaltung, was die Struktur vereinfacht und die Herstellung im Standard-Chipprozess erleichtert. Dieses Design eignet sich natürlich für dreidimensionales Stapeln über Logikschaltungen und verspricht dichte „Memory-on-Logic“-Layouts. Ein weiterer Vorteil ist das „nicht-destruktive Lesen“: Das Auslesen eines gespeicherten Werts entlädt diesen nicht sofort, wodurch die Häufigkeit von Refresh-Operationen reduziert werden kann. Allerdings entweicht bei traditionellen Siliziumversionen die gespeicherte Ladung in weniger als einer Millisekunde, sodass häufige Refreshs weiterhin Energie verschwenden und die Nutzbarkeit einschränken.

Oxid-Halbleiter: Ruhigere, kühlere Schalter

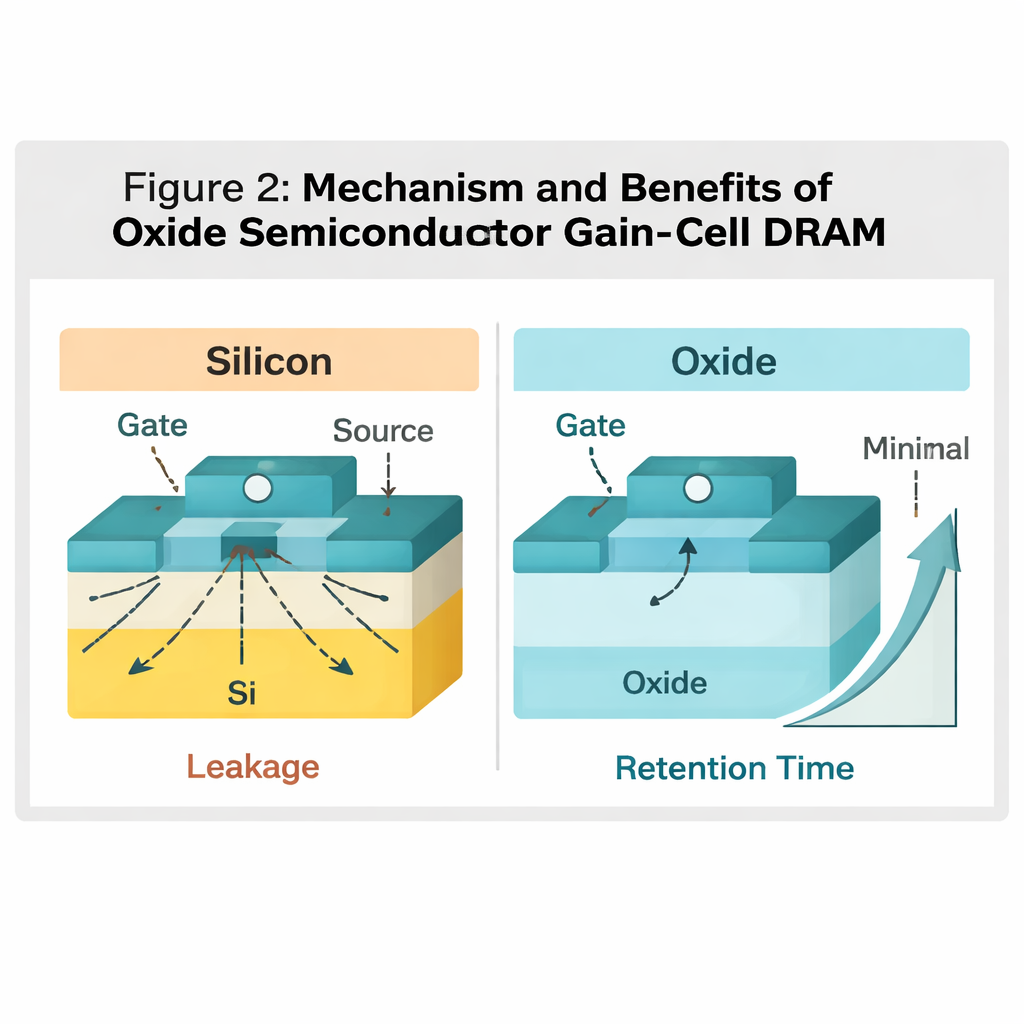

Um Leckströme in Gain-Cells zu überwinden, heben die Autorinnen und Autoren Oxid-Halbleiter hervor — Materialien wie Indium-Gallium-Zink-Oxid (IGZO) und verwandte Verbindungen — als neue Kanalmaterialien für die Transistoren. Diese Oxide haben eine breite Bandlücke, die unerwünschte Ströme stark unterdrückt, wenn ein Transistor ausgeschaltet sein soll. Messungen zeigen Ausschaltströme so winzig, dass sie an die Grenzen der Prüfausrüstung stoßen, und Prototyp-Gain-Cells halten Daten nun viele Sekunden, Stunden oder sogar länger als einen Tag, verglichen mit Tausendstelsekunden in Siliziumdesigns. Entscheidend ist, dass sich diese Oxide bei relativ niedrigen Temperaturen abscheiden lassen, die mit dem „Back-End“ der Chipfertigung kompatibel sind, wodurch Ingenieurinnen und Ingenieure dichte Speicherschichten direkt auf vorhandene Silizium-Logik aufbringen können, ohne diese zu beschädigen.

In die Höhe bauen: 3D-Stapel und winzige Transistoren

Während die Chips weiter schrumpfen, bringen allein kleinere Transistoren neue Probleme mit sich, etwa schlechte Kanalsteuerung und steigende Leckströme. Der Artikel gibt einen Überblick über fortschrittliche Transistorformen, die das Gate um den Kanal legen (Gate-All-Around- und Channel-All-Around-Designs), um auch bei Nanometer-Abmessungen eine enge Kontrolle zu gewährleisten. Durch den Einsatz von Oxid-Halbleitern in diesen Multi-Gate-Strukturen haben Forschende sehr kurze Kanäle, extrem geringe Leckströme und starke Datenretention bei vertikal gestapelten Speicherschichten demonstriert. Einige experimentelle Entwürfe erreichen bereits die Flächeneffizienz der besten heutigen DRAM-Zellen oder übertreffen sie, was darauf hindeutet, dass künftige Chips enorme Speicherkapazitäten auf sehr kleinem Raum direkt über den Prozessorkernen unterbringen könnten.

Von Labor-Materialien zu zuverlässigen Produkten

Um diese vielversprechenden Bauelemente in praktische Speicher zu überführen, ist sorgfältiges Materialengineering notwendig. Der Artikel beschreibt, wie das Anpassen der Metallmischung im Oxid, die Kontrolle des Sauerstoffgehalts und das Kristallisieren der Filme Geschwindigkeit und Langzeitstabilität ausbalancieren können. Er behandelt auch Möglichkeiten zur Handhabung von Defekten, Wasserstoffkontamination und den empfindlichen Grenzflächen zwischen Oxiden und Isolationsschichten, damit die Bauelemente unter Hitze und langdauerndem Betrieb stabil bleiben. Schließlich wird die Gestaltung der metallischen Kontakte diskutiert, sodass der Kontaktwiderstand die Vorteile der neuen Materialien nicht zunichte macht. Zusammen sollen diese Strategien Speicher liefern, der sowohl dicht als auch zuverlässig genug für die Großserienfertigung ist.

Was das für das Alltags-Computing bedeutet

Die Autorinnen und Autoren kommen zu dem Schluss, dass Gain-Cell-Speicher mit Oxid-Halbleitern die Architektur künftiger Chips verändern könnten. Durch die Kombination kleiner, leckstromarmer Speicherzellen mit 3D-Stapeln über Logikschaltungen könnten Designer deutlich mehr schnellen Speicher neben dem Prozessor platzieren und zugleich den Energiebedarf unter Kontrolle halten. Das würde die Speicherwand entschärfen und alles von KI-Beschleunigern über Cloud-Server bis zu persönlichen Geräten schneller und effizienter machen. Obwohl Herausforderungen in Zuverlässigkeit, Fertigungsuniformität und vollständiger Chip-Integration bestehen bleiben, skizziert die hier besprochene Arbeit einen klaren Weg hin zu kompakteren, leistungsfähigeren und energieeffizienteren Rechensystemen.

Zitation: Chung, S.W., Yoon, S.H. & Jeong, J.K. Oxide semiconductor gain cell-embedded memory: materials and integration strategies for next generation on-chip memory. Commun Eng 5, 39 (2026). https://doi.org/10.1038/s44172-026-00616-5

Schlüsselwörter: On-Chip-Speicher, Oxid-Halbleiter, DRAM-Skalierung, 3D-Integrierte Schaltungen, KI-Hardware